The integrated circuit design field is facing a severe reality. Only about 20% of ASIC chips succeed on their first tape-out.

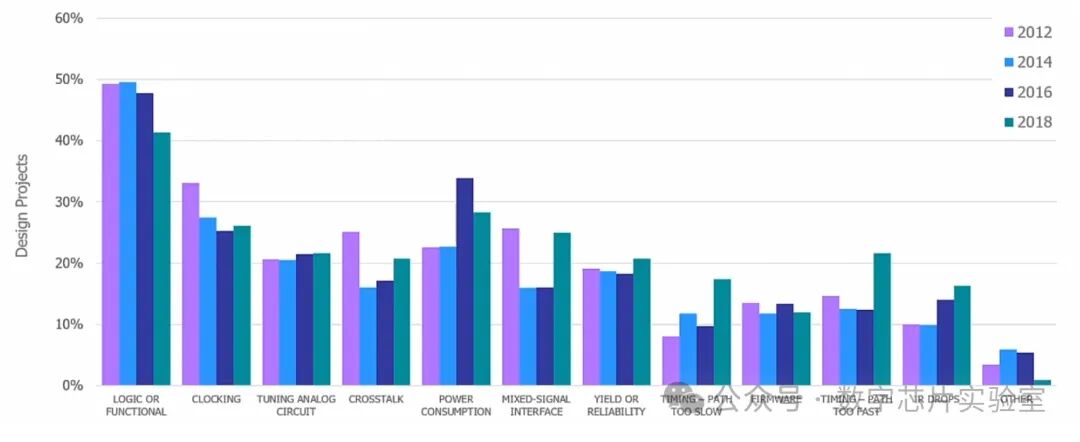

A significant reason for the high failure rate is that the challenges brought by new process nodes have not been fully understood. While some long-standing issues have been integrated into design tools and processes, problems such as mixed-signal interfaces, crosstalk, timing, and voltage drop remain major causes of re-tape-out.

The following image clearly illustrates the impact of different types of ASIC defects on re-tape-out, including logic or functional issues, clock problems, timing analysis, and more.

Some chips fail due to overly casual design processes, while others may not necessarily fail because of functional issues. If the silicon returns running 10% slower than expected, or consuming 10% more power than anticipated, it may lack competitiveness in the market, necessitating a re-tape-out.

People generally focus on functional issues and timing problems, but power issues are also very important.

As chip integration increases, on-chip power becomes an increasingly significant challenge. Accurate modeling and minimization of voltage margins are crucial for balancing energy efficiency and stability. Some companies take risks to push designs forward, even when problems are discovered. Companies may proceed with tape-out despite knowing there are serious IR drop issues, as schedule is often prioritized over perfection.

More and more issues are becoming interrelated. For example, power, IR drop, thermal management, timing, and electromigration are all connected, yet most analyses are still conducted separately.

Power noise can lead to voltage supply drops, and the same cell in different locations may experience timing delays due to reduced voltage, ultimately resulting in functional issues.

Complexity leads to higher power density, which in turn creates localized hotspots within the chip. Increased cell density also exacerbates voltage drop issues. High-precision temperature sensors and voltage monitors can help systems manage and adapt to these conditions, improving reliability and optimizing performance.

These issues are particularly pronounced in data centers and AI designs, where high-performance demands place tremendous pressure on temperature and voltage management.