Unveiling I2C Pull-Up Resistor Value Techniques: 5 Key Design Points and Practical Cases

Introduction: Why Must I2C Be Equipped with Pull-Up Resistors?

In the communication between the main control chip and other modules (such as cameras, sensors, etc.) in embedded systems, the I2C bus is widely used due to its simplicity, reliability, and low cost. However, many engineers frequently encounter pitfalls during design:Should the pull-up resistor be 2.2K, 4.7K, or 10K? Does having too many devices on the bus lead to communication failures? This article will dissect the technical principles in detail and reveal the secrets of selecting I2C pull-up resistor values.

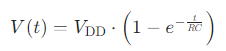

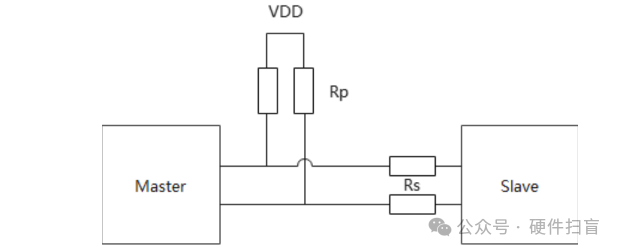

Since the I2C interface uses an Open Drain mechanism, the device itself can only output a low level and cannot actively output a high level; it can only pull the signal line to a high level through an external pull-up resistor RP. Therefore, pull-up resistors on the I2C bus are essential!

In the IIC bus system, the selection of pull-up resistors is a critical aspect, primarily involving two key points.

The first is the sinking current

Since the IIC bus interface is mostly open-drain output, when the device outputs a low level, the current flows through the pull-up resistor into the device. If the resistance value of the pull-up resistor is too small, the sinking current will be too large, which may cause the low level output of the device port to rise, even exceeding the 0.4V limit specified by the I2C protocol, and in severe cases, it may damage the port; conversely, if the resistance value is too large, although the sinking current will decrease, it will also affect the signal’s driving capability and transmission quality.

The second is the speed (timing constraints),

The IIC bus has various transmission speeds, such as standard speed 100KHZ and high speed 400KHZ, and different speeds have strict requirements on the signal’s rise time. The pull-up resistor will form an RC filter circuit with the equivalent capacitance in the line, affecting the signal’s rising edge. If the pull-up resistor value is inappropriate, it will cause the signal rise time to be too long, failing to meet the timing constraints at specific speeds, leading to data transmission errors or instability. Therefore, considering both the sinking current and speed factors, selecting the pull-up resistor reasonably is crucial for ensuring the stable and efficient operation of the IIC bus.

Two Core Formulas for Pull-Up Resistor Value

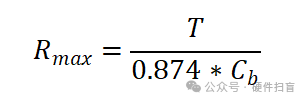

The maximum value of the pull-up resistor is generally determined by the maximum bus capacitance (Cb).

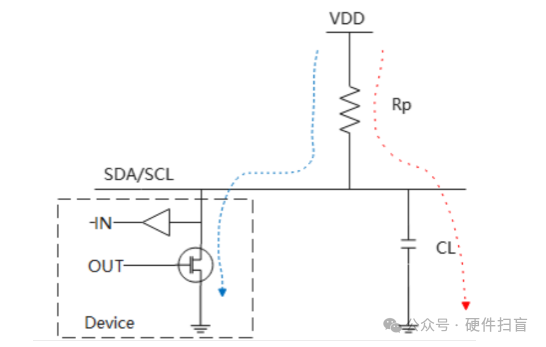

The minimum value of the pull-up resistor is determined by Vdd and the pull-up driving current (generally a maximum of 3mA).

1. Minimum Resistor Value Formula (Sinking Current Limitation)

• Example: When VDD=5V, Rmin ≈1.7KΩ; when VDD=2.8V, Rmin≈ 800Ω

• Example: When VDD=5V, Rmin ≈1.7KΩ; when VDD=2.8V, Rmin≈ 800Ω- • Trap: Using a 1KΩ resistor results in a sinking current of 5mA, which may burn out the output pin.

Question 1: Why is it 0.4V?

1.I2C Specification (NXP official document UM10204) clearly defines: Vol(max) = 0.4V

That is, when the device outputs a low level, the bus voltage must be below this value; otherwise, the master device cannot reliably recognize logic “0”.

- 2. Physical Significance • The low-level threshold of digital circuit switching: The low-level threshold of CMOS/TTL logic gates is usually 0.8V, and 0.4V is a safety margin reserved through margining design.

- 3. Driving Capability Constraints: Choose the minimum resistance that meets 𝐼𝑂𝐿=𝑉𝐷𝐷−𝑉𝑂𝐿𝑅𝑝 to ensure it is within the allowable sinking current range (usually limited to 3mA).

2. Maximum Resistor Value Formula (Timing Constraints)

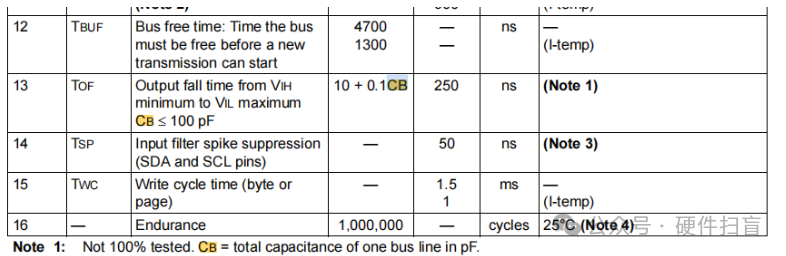

Cb is Bus Capacitance, which can generally be found in chip documentation: for example, the Microchip 24C02 chip documentation states:

• When the bus rate is 100kHz, T=1μs; at 400kHz, T=0.3μs

• When the bus rate is 100kHz, T=1μs; at 400kHz, T=0.3μs- • Practical Data: Assuming Cb=200pF, at a 400kHz rate, Rmax=7KΩ

Question 2: Why is it 0.874? Is there technical support behind it?

In IIC bus design, the maximum value formula for pull-up resistors Rmax=T/(0.874×Cb) contains the coefficient 0.874, which embodies rigorous signal integrity principles. This coefficient originates from the mathematical derivation of the RC circuit charging curve and combines the specific requirements of the IIC protocol for signal rise time.

Technical Principle Analysis:

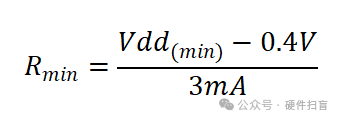

1. RC Charging Curve Characteristics The pull-up resistor R and the bus equivalent capacitance C form a first-order RC circuit, and its charging voltage formula is:

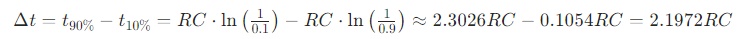

When the signal rises from a low level (0V) to a high level (VDD), the rise time is usually defined as the time difference for the voltage to rise from 10% to 90% VDD. Substituting into the formula yields: At this point, if Δt=T, then Rmax=T/2.1972*Cb, but this coefficient differs significantly from 0.874.

At this point, if Δt=T, then Rmax=T/2.1972*Cb, but this coefficient differs significantly from 0.874.

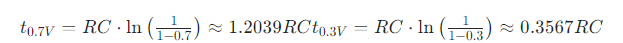

- 2. Actual Constraints of the IIC ProtocolThe IIC protocol has stricter definitions for rise time:The time difference from low level (0.3V) to high level (0.7V). Substituting into the formula:

- 3. The time difference Δt=1.2039RC−0.3567RC=0.8472RC. Therefore, Rmax=T /0.8472*Cb, at this point the coefficient approaches 0.874.

- 4. Engineering Corrections and Empirical Values In practical applications, parasitic parameters in the circuit (such as PCB trace capacitance, device input capacitance) can lead to calculation errors. To ensure that signals still meet timing requirements under extreme conditions, engineers usually introduce a safety factor to correct theoretical values, ultimately arriving at the empirical coefficient 0.874. This value not only ensures calculation convenience but also leaves room for practical engineering. 0.874 is not arbitrarily set but is a product of the comprehensive synthesis of the RC circuit mathematical model and IIC protocol specifications. Through rigorous derivation and engineering validation, it ensures that the pull-up resistor meets timing constraints while considering system reliability and anti-interference capability. In actual design, it is recommended to flexibly use the formulas for precise calculations based on specific circuit parameters (such as measured values of (C_b)) and protocol rates (such as T corresponding to 100kHz or 400kHz).

2. Value Strategies in Different Scenarios

| Application Scenario | Power Voltage | Recommended Resistance Value | Tolerance Range |

| Industrial Controller | 5V | 4.7KΩ | 200pF/400kbps |

| Long-distance Communication Devices (Anti-Interference) | 3.3V | 3.3KΩ | 150pF/200kbps |

| Low-Power IoT Devices (Low Power) | 1.8V | 10KΩ | 50pF/100kbps |

Typical Cases:

- • The main control board of the GoPro sports camera uses two 2.2K resistors in parallel (equivalent to 1.1KΩ) to handle transient currents during high-speed shutter control.

- • The Tesla Autopilot system uses precision 0.1% tolerance 4.99K resistors to ensure synchronous communication among multiple sensors in the vehicle.

3. Hardware Design Experience Points

- 1. PCB Layout

- • It is recommended that the pull-up resistor be placed close to the signal output end (such as next to the MTK processor).

- • The SDA/SCL lines should be of equal length (length difference < 5mm), with ground lines arranged on both sides.

- • Use a shielding layer to wrap the signal lines in the antenna area (refer to mobile phone RF module design).

- • At the FPC pivot, series a 100Ω resistor (as shown below), which has been measured to reduce ringing noise by over 30%.

4. Five Pitfall Avoidance Guidelines for Embedded Development

- 1. Dynamic Adjustment Technology

// STM32 implements variable pull-up resistor through IO switching GPIO_InitStruct.Pull = GPIO_NOPULL; // Default no pull-up if(speed_mode == HIGH_SPEED) HAL_GPIO_WritePin(GPIO_PULL_CTRL, HIGH); // Enable strong pull-up - 2. Software Simulation Considerations

- • Sampling time must be ≥ 3 times the RC time constant.

- • When debugging with an oscilloscope, the trigger must be at the threshold point of 30% VDD.

- • The SMBus Alert response mechanism must be enabled.

- • Use a secondary retransmission protocol in case of bus conflicts.

5. Solutions for Extreme Scenarios

- 1. Ultra-Long Bus (>1m)

- • Use the PCA9600 bus extender chip, which supports communication up to 250 meters.

- • Parallel Schottky diodes (such as BAT54S) to enhance edge speed.

- • Choose thick film resistors (such as Vishay CRCW-HP series).

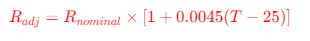

- • Set temperature compensation:

Conclusion: Quick Reference Table for Design Parameters

| Parameter | Recommended Range | Key Impact |

| Resistor Power Consumption | ≤3mW | Temperature rise leads to resistance drift. |

| Signal Rise Time (400kbps) | <300ns | ISO7637 transient test fails. |

| Bus Node Count | ≤10 | Exceeding requires a bus driver. |

| Wiring Capacitance | ≤200pF | Every additional 50pF reduces speed by 100kbps. |