Editor’s Note: This article is adapted from Chapter 1 of “The ASIC Handbook,” based on the original text and combined with the author’s practical experience, with some modifications.

The ASIC Handbook – ASIC Project 1

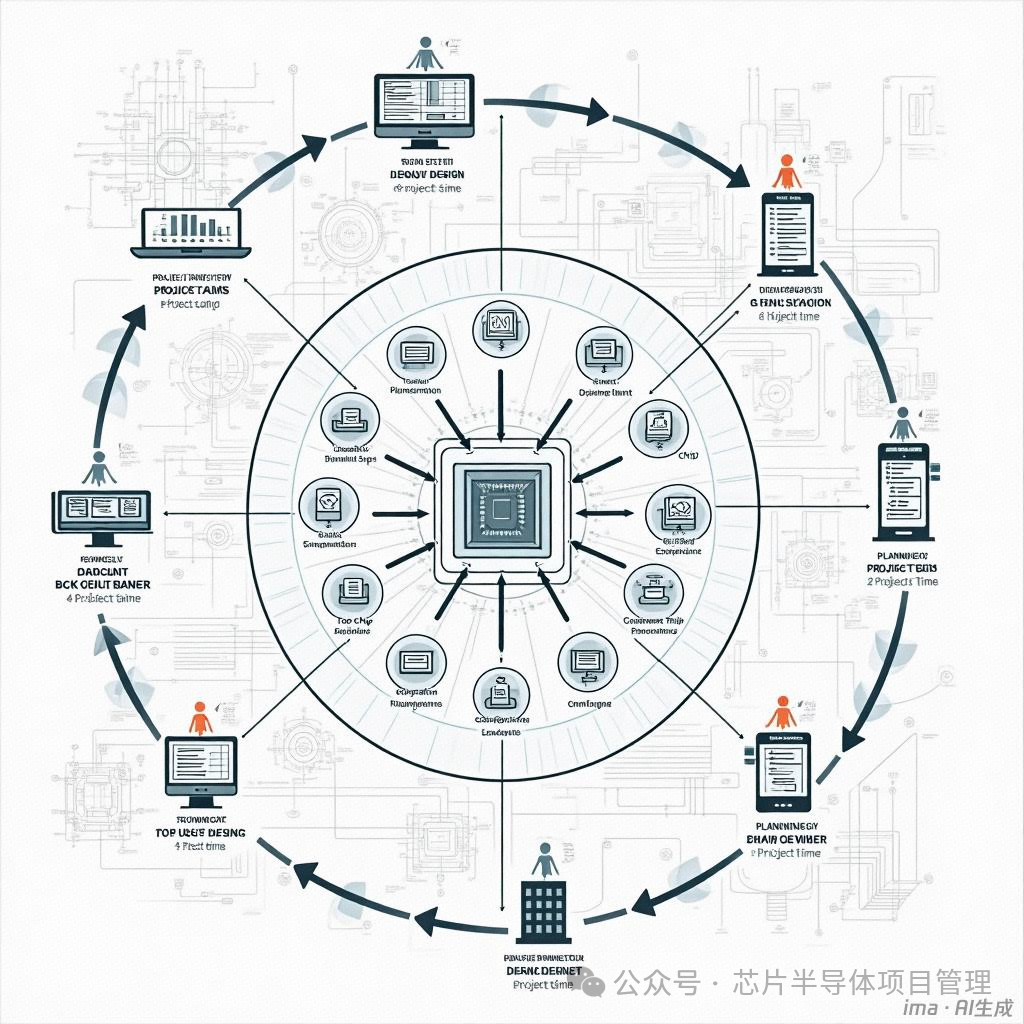

4 Top-Level Design Phase (Top-Level Design Phase)

Output Deliverables:

- Approved functional requirements specification

- Defined top-level architecture documentation

- Resource planning and team formation plan

Main Tasks:

(1) Architecture Design: Balance cost, performance, resources, and risks, defining the functional division between ASIC and board-level/software.

• Write the functional requirements specification document

• Brainstorm various architectural options

• Analyze architectural options—considering technical feasibility, resource requirements, development timelines, etc.

• Generate top-level architecture documentation

• Identify key modules—initiate early if necessary

• Identify potential third-party IP module requirements

• Estimate die area, pin count, cost, power consumption, etc.

• Determine design route/design flow

(2) Toolchain Confirmation: Select synthesis, simulation tools, and establish design flow documentation (see Chapter 3).

(3) Team Formation: Recruit core members and plan training to ensure hardware/software engineers collaborate. Brainstorm potential risks.

Project Manager Tasks:

- Develop project plans and coordinate resources (personnel, equipment, tools).

- Negotiate contract terms with IP suppliers.

5 Module Specification Phase

Output Deliverables:

- Module decomposition and interface definition document

- Accurate project planning (including risk mitigation measures)

Main Tasks:

- Module Decomposition: Split the top-level architecture into sub-modules through team meetings, clarifying interface signals and timing.

- Specification Review: Organize cross-department expert reviews to ensure module functionality aligns with system objectives.

- Testing Framework: Define testing platform architecture and assign testing case development tasks.

Project Manager Tasks:

• Conduct team-building activities and implement individual incentive measures

• Begin considering die evaluation/verification work

• Establish a quality project framework, clarifying information storage locations and update control mechanisms

• Update project plans, allocating resources for lower-level module design tasks

• Analyze and manage project risks

Risk Control:

- Communication Isolation: Ensure team members understand project objectives through daily stand-up meetings.

- Requirement Changes: After freezing interface specifications, any modifications must be approved through change control processes.

6 Module Design and Implementation

Output Deliverables:

- Completed RTL code, module-level simulation, and synthesis

- Chip area estimation and pin allocation scheme

Main Tasks:

• Module design, coding, testing, and synthesis

• Design, code, and test chip-level testing platforms

• Generate more accurate silicon area estimates

Project Manager Tasks:

• Develop documentation specification guidelines, clarifying documentation standards and detail requirements

• Specify review processes, defining review content and timelines

• Review quality framework implementation plans with the team

• Chair weekly project meetings, continuously tracking and closing action items

• Negotiate with suppliers to determine prototype layout schemes

• Determine test vector strategies and required test coverage

• Reserve prototype production and testing resources

• Obtain third-party simulation models

Technical Points:

- Code Quality: Follow company coding standards, enforcing register reset conditions to avoid unknown states (X) in gate-level simulations.

- Early Synthesis: Run experimental synthesis during the RTL phase to monitor timing and area metrics.

- Testing Platform Development: Use synthesizable test code to support hardware-accelerated verification.

Potential Risks:

• Progress delays may occur at this stage—reviews should be conducted early, and plan execution should be closely monitored

• Chip gate count may exceed maximum estimates—architecture adjustment plans should be considered

Most team members at this stage will undertake core tasks, while others will handle various miscellaneous work. For management convenience, this stage can be divided into two main work lines: first, describe the main team’s task content, and then explain the arrangement of remaining tasks.

7 Subsystem Simulation

Objective:

- Validate the integrated functionality of logic-related modules, shortening overall chip simulation time.

Strategy:

- Layered Testing: For communication-type chips, trigger specific error conditions (e.g., FIFO overflow) through subsystem simulation to avoid time-consuming full-system simulations.

- Automation Scripts: Batch run tests and record results, reducing manual intervention.

Output Deliverables:

• Successful first run of subsystem simulation

• Reviewed subsystem simulation specifications

• Subsystem module testing completed

Main Tasks:

• Write and review the testing checklist document.

• Write testing “pseudo-code” (e.g., CPU register access, test platform configuration).

• Run simulations.

Project Manager Tasks:

• Closely monitor the plan; schedule regular brief meetings to discuss progress.

Risk Alerts:

• Poor communication of simulation issues among team members may unnecessarily extend time; the project manager should prioritize issues daily.

8 System Simulation and Synthesis

Output Deliverables:

• Successful first run of system simulation

• Reviewed system simulation specification documents in place

• Completed all RTL and gate-level simulations

• Generated initial trial netlist

Main Tasks:

• Write and review the testing list document

• Write testing “pseudo-code” (including CPU register access, test platform configuration, etc.)

• Execute RTL and gate-level simulations

• Use the fault reporting system to record and track defect repair progress

• Check chip design rule compliance

• Write chip device user guide

• Create synthesis scripts and initial experimental netlist

• Develop layout planning and documentation

Project Manager Tasks:

• Closely monitor project progress, schedule brief meetings to discuss progress

• Coordinate with ASIC suppliers to hold layout design meetings

Risk Alerts:

• Poor communication among engineers will significantly extend the implementation cycle of the first system simulation

9 Layout and Backend Phase

Output Deliverables:

- Post-layout timing/capacitance information.

- Standard Delay Format (SDF) files.

- Power analysis report and test vectors (IDDQ/scan chain).

Main Tasks:

- Manually fix critical path timing violations through Engineering Change Orders (ECO).

- Layout of experimental and final netlists

- Check for errors in netlists and test vectors

- Generate post-layout timing/capacitance information

- Complete cell layout, clock tree insertion, routing, and design rule checks (DRC).

- Generate Standard Delay Format (SDF) files for post-simulation.

References:

Horspool Nigel., & Gorman Peter. (2025). The ASIC Handbook. Upper Saddle River, NJ: Prentice Hall.

Chip semiconductor industry project management series articles

PowerProjectPro semiconductor industry application cases

|

This circle has over 20 years of experience in semiconductor industry R&D and project management, IT digitalization, striving to create industry practice templates, and assisting in the efficient and high-quality delivery of chip and semiconductor R&D through digitalized R&D management. |