Click

Blue Text

Follow us~

Today, I share an experience summary on PCB process design, hoping to inspire industry colleagues.

1 PCB Basic Technology

1.1 PCB Size and Shape

The welding processing dimensions of the PCB material shape are width (200mm~250mm) * length (250mm~300mm).

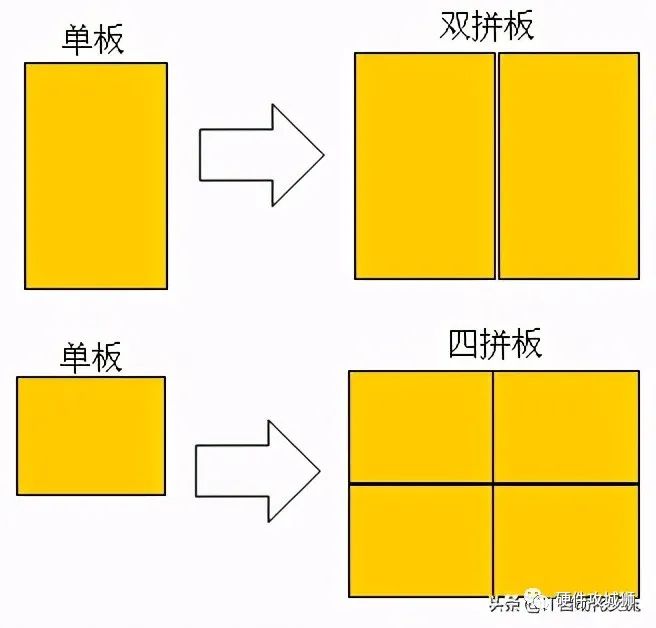

For PCBs with a long edge less than 125mm or a short edge less than 100mm, a splicing method can be used (as shown in Figure 1).

This size helps avoid issues during wave soldering and reflow soldering processes.

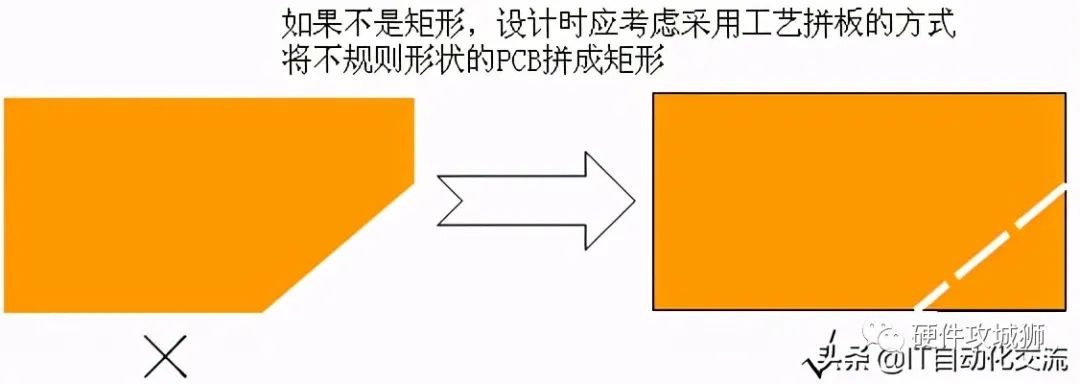

If it is not rectangular, it will cause instability during processing on the conveyor belt, flipping of the board during insertion, and issues with solder splashing onto the component surface when passing through the wave soldering tank.

Figure 1

If it is not rectangular, use a process splicing method to form a rectangular shape from an irregularly shaped PCB, especially for the four corners; if there are notches, they should be filled to form a rectangle. For PCBs with only surface-mounted components, notches are allowed, but their size must be less than 1/3 of the length of the edge.

Figure 2

1.2 PCB Substrate

In the design of the circuit board, the requirements for the PCB material must be specified and marked in the technical requirements of the PCB design document, including:

PCB material and grade (commonly used are epoxy resin glass fiber cloth-based FR-4, FR-5);

Flame retardant grade (UL94-V0, UL94-V1 grade, or green flame retardant type);

Material thickness, nominal specifications include 0.8, 1.0, 1.2, 1.6, 2.0, 2.5, 3.0, 3.5 (unit mm);

Material thickness tolerance ±10%;

For medical device products, the material thickness must be ≥1.6mm, A1, A2 grade;

In instruments used in flammable and explosive environments, the flame retardant grade should be marked on the PCB.

1.3 Coatings

The types of PCB coatings include tin plating (preferred), nickel-gold plating. Tin-plated PCBs are prone to oxidation when exposed to air for a long time,and should be vacuum packaged during storage in the factory.

1.4 Number of Layers

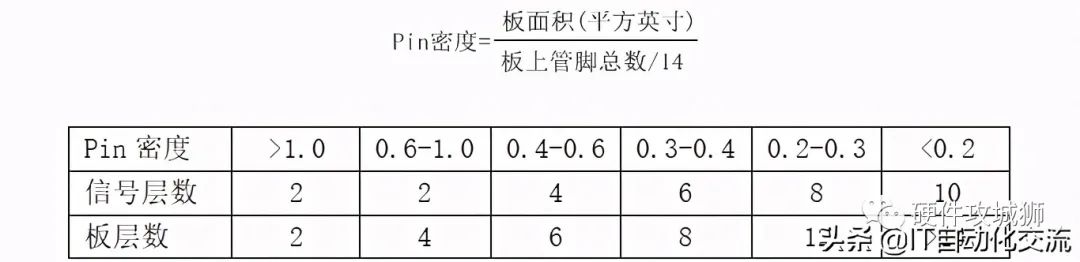

Multi-layer PCBs have outstanding effectiveness in electromagnetic compatibility protection,but also have higher manufacturing costs, so the design should compromise according to signal requirements.

When fclk>5MHz, or tr<5ns (the rise or fall time of the pulse), multi-layer boards are recommended; once it is determined to use a multi-layer board, the number of wiring layers should be determined based on pin density.

Figure 3 Pin Density

If a double-sided board must be used, one side of the PCB must be made as a complete ground layer.

1.5 Design for Manufacturability

When designing PCBs, it is important to leave sufficient space and reference for the manufacturing process to avoid technical risks during production.

During assembly and soldering, a blank width of ≥5~10mm should be left on both sides of the PCB, where no components or solder points should be placed, serving as the process edge.

If the PCB cannot leave a process edge, auxiliary edges of 5~10mm can be added to both conveyor edges as process edges, which can be removed after soldering.

Reference points used in the assembly process must be set on the PCB (also known as optical MARK points or MARK points), as reference points for device placement. The form of the pads for reference points and the symmetrical layout should be confirmed with the process engineers of the assembly manufacturers.

A background area should be set around the MARK points, and no other pads, silkscreen, or solder mask should be present in this area.

The center of the reference point should be more than 5mm away from the edge of the board; each type of reference point should have at least two, placed diagonally and asymmetrically.

BGA and multi-pin packages should have local reference points to prevent thermal errors during operation or cumulative errors of the PCB, which may cause misalignment of the placement of fine-pitch devices.

For BGA packaged devices and other packaged devices with more than 100 pins, a pair of local reference points must be placed diagonally; the optical reference points should be placed within 5mm of the device perimeter; no components should be placed within 3mm around the optical reference points.

2. Pads and Vias

2.1 Pads

The quality of the pads directly affects the soldering effect, so the design of the pads is crucial.

When the pad hole diameter is 0.3~0.5mm wider than the device lead width, and the total pad diameter is 2~2.5 times the pad hole diameter, it is ideal for achieving good wetting angles during soldering.

The hole diameter D for through-hole solder pads for through-hole resistors, capacitors, inductors, ferrites, diodes, and transistors is equal to the outer diameter d of the component leads + (0.3~0.5mm).

Surface mount pads at both ends should be well-symmetrical to ensure balanced surface tension of the molten solder, avoiding bridges and shifts during soldering; violating this requirement may lead to soldering defects during reflow soldering.

When there are many pins on each row of plug-in components, the pad arrangement direction should be parallel to the board entry direction; it is recommended to set up solder pads to absorb excess solder, avoiding the connection of 2~3 pads parallel to the board entry direction at the tail end of the wave soldering.

2.2 Through Vias

Design rules for through vias: the standard size for through vias is:Hole diameter: board thickness ≥ (1:6);

For high-speed signals, a through via generates 1~4nH of inductance and 0.3~0.8pF of capacitance, so when laying high-speed signal lines, the number of through vias should be minimized; for parallel high-speed signal lines, such as address lines and data lines, if layer changes are unavoidable, ensure that the number of through vias for parallel signal lines is the same.

2.3 Mounting Screw Holes

The mounting screws on the PCB should have a prohibited area, with the prohibited area diameter = (screw diameter * 2.2) + (2~3mm) to ensure sufficient electrical insulation space.

3. Layout Rules

3.1 Device Orientation

For plug-in components with multiple pins on the soldering side, such as connectors, DIP package devices, and T220 package devices, the axis should be perpendicular to the wave soldering direction during layout.

Active components such as PLCC and QFP should avoid wave soldering.

Similar types of plug-in components should be placed in one direction along the X or Y axis.

For similar polar discrete components, it is best to keep the direction of polarity consistent within a functional area along the X or Y axis.

3.2 Device Layout

The recommended minimum spacing between components is:

① The edge spacing of small surface-mounted resistor and capacitor pads >0.3~0.7mm;

② The spacing between other chip components, SOTs, and SOICs is 1~1.25mm;

③ The spacing between SOICs and between SOICs and QFPs is 1.5~2.0mm;

④ The spacing between PLCCs and chip components, and between SOICs and QFPs is 2~2.5mm;

⑤ The spacing between PLCCs is 3~4mm;

⑥ The spacing between the outer side of the plug-in component pads and the outer side of the chip component pads should be greater than 1.5~2mm;

⑦ The edge spacing of plug-in components passing through wave soldering should be greater than 1~2mm;

⑧ The distance between BGA and adjacent components should be greater than 3~5mm.

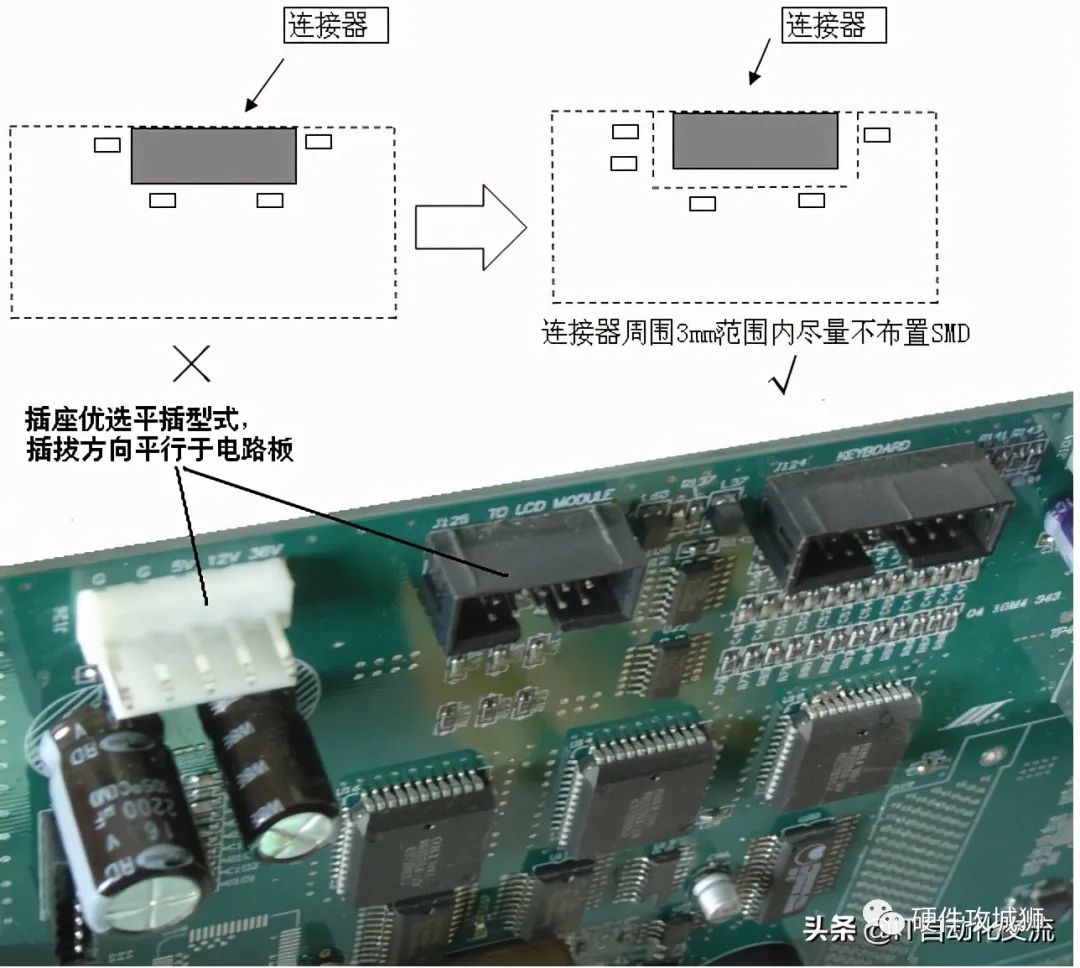

For adjustable and pluggable components, do not place SMT components within a 3mm range around the board surface to prevent insertion stress from damaging components; connectors far from the mounting pillars should preferably be flat connectors.

Figure 4 Socket Installation Direction

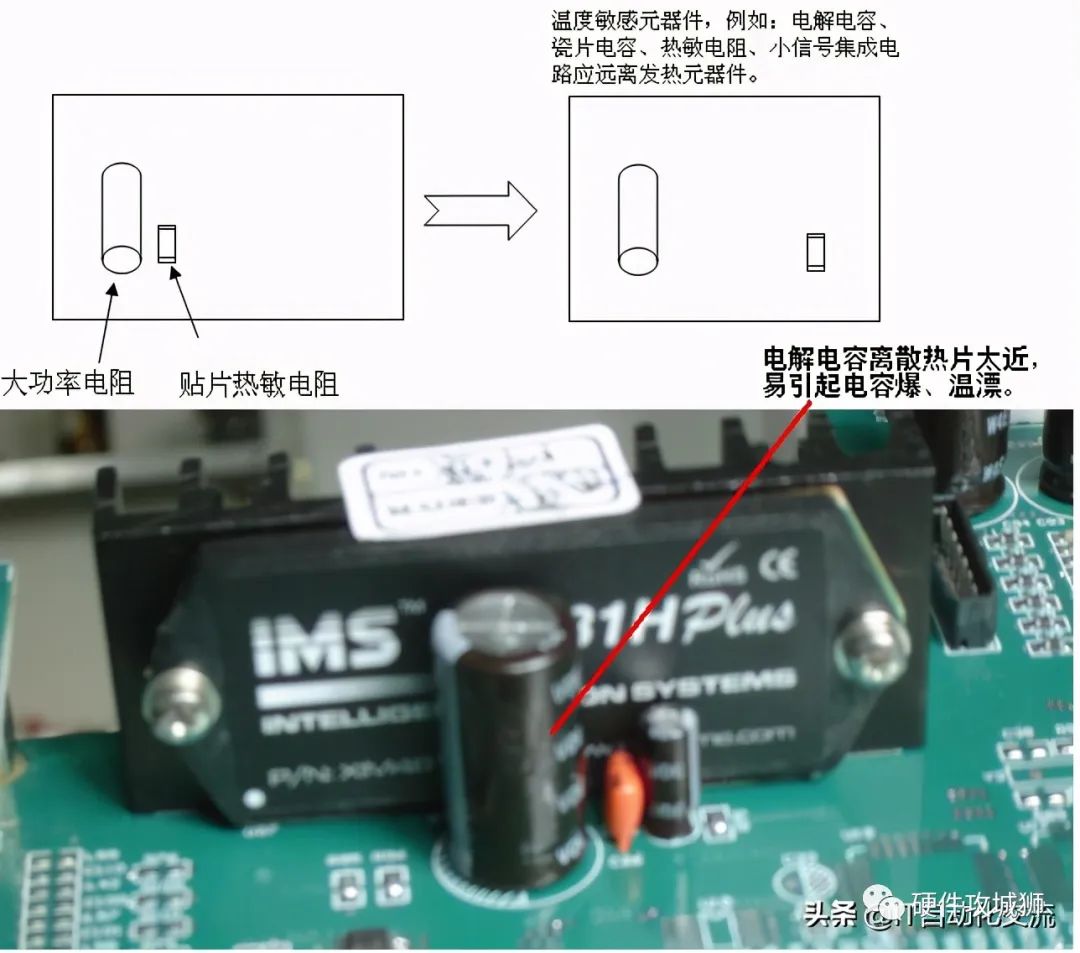

Under natural cooling conditions, temperature-sensitive components such as ceramic capacitors, electrolytic capacitors, thermistors, and temperature-sensitive ICs should be kept away from heat-generating components; if they cannot be kept away, temperature tests should be conducted to ensure that the temperature rise of sensitive components is within the derating usage range.

Figure 5 Temperature Sensitive Components Away from Heat Sources

Layout rules matching soldering processes:

① To reduce the number of heating cycles for the PCB, the following order should be followed when choosing the device layout method: single-sided plug-in—single-sided surface mount—single-sided mixed mount—A side mixed mount B side plug-in—A side mixed mount B side surface mount—double-sided mixed mount;

② If there are a small number of components, such as buzzers, LEDs, sockets, etc., that must be plugged in on the bottom side, manual rework may be used.

Devices with thermal power density >0.4W/cm3 should have heat sinks or be mounted on metal bases or enclosures to enhance the overheating capacity of the components.

High-power resistors without heat sinks should be elevated 3~5mm for heat dissipation.

4 Wiring Rules

4.1 PCB Wiring Coating

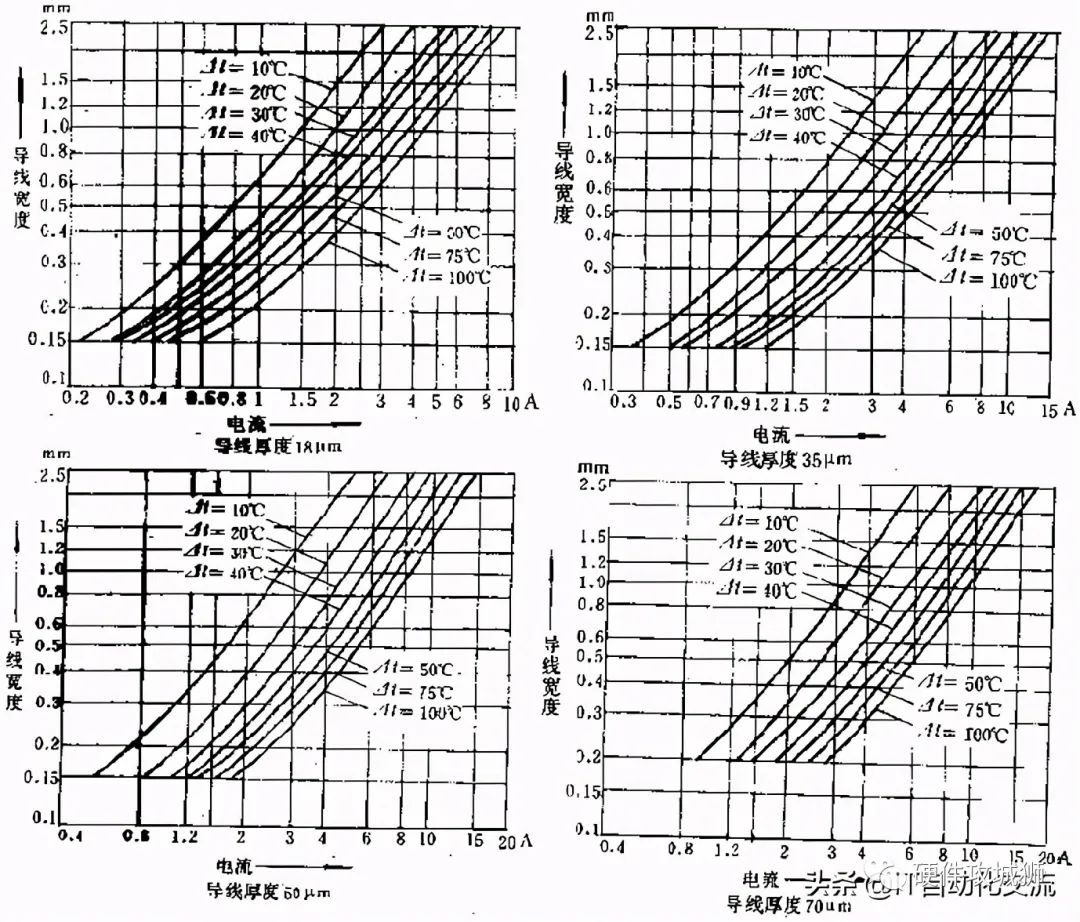

The relationship between PCB copper foil line width/thickness/current carrying capacity is determined according to (Figure 4.1):

Printed lines generate temperature rise when current passes through, which is related to the line width when the copper foil thickness is fixed.

If the design needs to increase the current of the line and cannot widen the line, the temperature rise of the line should be fully estimated.

According to standard SJ/Z1675-81, when the thickness of the line is fixed, the relationship between the load current and temperature rise for lines of different widths is shown in the figure.

Figure 6

4.2 Wiring Rules

Gold fingers protruding from the board edges, the two ends of the board side where the gold fingers are located (R1.0~R1.5 rounded corners), and the connecting end face of the gold fingers (the chamfer size should refer to the PCB thickness, R0.5 or less, to facilitate insertion and removal) should be chamfered;

No pads should be present at the inner end of the gold fingers, and pads and components should be kept away from the gold fingers.

A/D signals, input/output signals, currents that differ by two orders of magnitude, high/low voltage, and high/low frequency signals must be kept away from each other; if they cannot be kept away, ground lines should be laid between them for isolation.

Any line spacing ≥3 times the width of the printed line, i.e., ≥3W, can avoid 70% of the electric field interference between two lines.

The ground plane on the PCB should extend 20H beyond the edges of the power layer and signal layer (the thickness of the power and ground or signal layer to ground is 1H), limiting 70% of the electric field radiation within the edge of the ground layer.

A 3mm prohibited area should be left around BGA devices, preferably a 5mm prohibited area.

Signal lines should be avoided under crystal oscillators, heat sinks, relays, optocouplers, power modules, transformers, and voltage regulators.

Wiring widths within the same grid should be consistent; changes in line width can lead to uneven impedance characteristics, causing reflections when transmitting signals at high speeds; this should be avoided in PCB wiring. If changes in line width are unavoidable, the effective length of the inconsistent portions should be minimized, such as for lead wires of BGA packages and connectors.

Signal lines and their loops should form closed loops; floating wiring is not allowed on this closed loop; special attention should be paid to self-loops that may occur on the same layer or different layers, generating unnecessary radiation and receiving interference.

Pads on large copper foils are connected to pads through thermal isolation bands, i.e., thermal pads, with a “米” or “十” shape connection between the pads and copper foil. Thermal pads should not be used for pads carrying high currents.

4.3 Socket Pin Routing

Each power supply on the socket pin should be paired with at least one ground pin.

5 Markings

5.1 Types of Markings

The following areas and contents on the PCB should be marked with silkscreen: PCB version number, pin symbols, device polarity, device orientation, safety identification, hazard identification, and parameter values of key points (such as marking the supply voltage next to the power socket, Vcc1 3.3V;

marking the voltage pins and key voltage testing points on critical ICs, as well as other functional parameters such as waveform, frequency, etc.

Warning identifiers should be in all uppercase letters, and descriptive text should start with an uppercase letter followed by lowercase letters.

Figure 7 Marking Requirements

The fuse marking should include fuse serial number, melting characteristics, rated current value, explosion-proof characteristics, rated voltage value, and English warning identifier; if there is no space on the PCB for layout markings, the warning content can be explained in the product manual.

The five safety regulation markings on the PCB (certification mark, manufacturer, manufacturer model, certification document number, flame retardant grade) should be complete.

5.2 Marking Requirements

Silkscreen numbers should be placed next to the corresponding components and should not be covered by the components after installation or obscured by the body or other components; the direction of the numbers within each board should remain consistent or maintain a consistent direction within a functional circuit range.

No silkscreen should be present on pads, solder paths, through holes, and test pads.

Silkscreen should clearly indicate representative pin numbers for easy identification of other pins and checking the direction of connectors.

The spacing between silkscreen characters should be >5mil, and the spacing from the edge of the pad should be >5mil; the width of silkscreen character lines should be 6mil~12mil, preferably 8~10mil; the height of silkscreen characters should be 50mil~60mil; adjustments may be made for smaller PCB areas.

6. Testability Design

ICT test points on the PCB should be on the soldering side; the pad size for test points should be ≥24mil (0.6mm), and the minimum spacing between two separate test points should be 60mils (1.5mm);

For PCBs requiring ICT testing, two 125mil non-plated holes should be designed diagonally on the PCB for ICT testing positioning;

Surface mount component pads should not double as test pads.

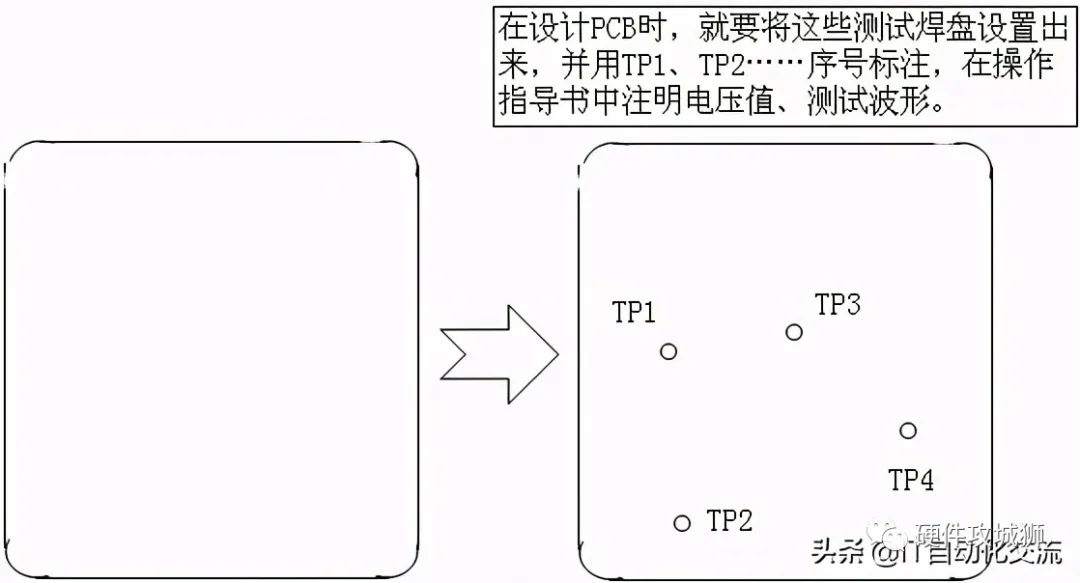

When the machine is powered on, a digital multimeter can be used to check the total supply voltage of the single board, the supply voltage of each functional circuit, the voltage of key components, and waveforms at key locations.

When designing the PCB, these test pads should be set up and labeled with TP1, TP2…… in sequence, indicating voltage values and test waveforms in the operational guide.

Figure 8 Test Point Requirements

7. Cables

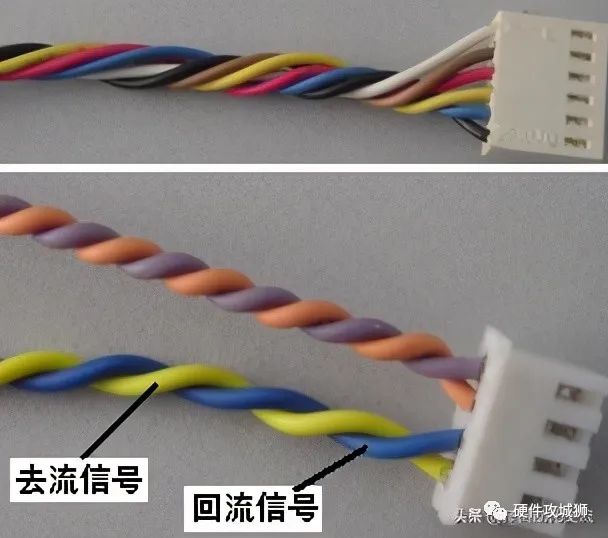

Non-shielded signal wire twisting guidelines:

① Non-shielded signal cables and incompatible signal lines (in/out, A/D signals, high/low level signals, high/low frequency signals) should not be twisted together;

② The outgoing signal and return signal of the signal line should be twisted together.

Figure 9 Outgoing and Return Signals Twisted Together

For shielded cables, the ferrite ring should be installed on the inner side of the shield layer.

For cables inside the chassis, the ferrite ring should be fixed to the circuit board or chassis wall using hot melt adhesive.

8. Board Level Grounding Measures

For signals above 10MHz, multiple ground points should be used nearby, with a ground plane covering a large area.

Grounding rules for mixed high and low frequency circuits:

≤1MHz should use single-point grounding (but be cautious of common impedance interference);

≥10MHz should use multiple nearby grounding;

For frequencies between 1~10MHz, if the ground line length <λ/20, then use single-point grounding; if the ground line length >λ/20, then use multiple nearby grounding; λ is the wavelength.

It is recommended that low-frequency digital ground (below 10MHz), analog ground, working power ground (for relays, stepper motors), safety ground, surge protection ground, and shield ground should first be grounded separately,and then connected with direct connections, small resistors, ferrite beads, capacitors, large resistors, etc., depending on the grounding purpose.

The purposes of grounding are as follows:

① If grounding is needed for equal potential—ground should be directly connected;

② If there are pulse currents on the digital ground but the two grounds need to be equal potential, connect with a small resistor to slow down the ground current impact;

③ If there is high-frequency interference on the ground, use ferrite beads to dissipate high-frequency pulse currents;

If you wish to discharge static charge but isolate direct current, connect with a capacitor.

Meizhou City Printed Circuit Industry Association

Source: PCB Media

Copyright statement: The above pictures and texts are copyrighted by the original author. The “Meizhou City Printed Circuit Industry Association” is sharing as a reprint. If there are any copyright issues, please contact us for deletion.