Abstract: This design guide discusses how to design RS-485 interface circuits. It covers the necessity of balanced transmission line standards and provides an example of a process control design. The article also discusses line loading, signal attenuation, failure protection, and current isolation under different headings.

This article focuses on the most widely used balanced transmission line standard in industry: ANSI/TIA/EIA-485-A (hereinafter referred to as 485). After reviewing some key aspects of the 485 standard, it introduces how to implement differential transmission structures in practical projects through an example of factory automation.

In long-distance, high-noise environments, data transmission between computer components and peripherals is often difficult. Whenever possible, single-ended drivers and receivers should be avoided. For systems requiring long-distance communication, balanced digital voltage interfaces are recommended.

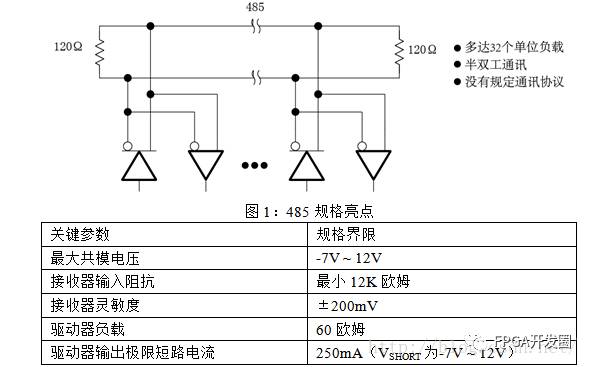

485 is a balanced (differential) digital transmission line interface developed to improve the limitations of TIA/EIA-232 (hereinafter referred to as 232). The features of 485 include:

-

High communication rate – up to 50M bits/s

-

Long communication distance – up to 1200 meters (Note: at 100Kbps)

-

Differential transmission – lower noise radiation

-

Multiple drivers and receivers

In practical applications, if reliable and low-cost data communication is needed between two or more computers, 485 drivers, receivers, or transceivers can be used. A typical example is the use of 485 to transmit information between sales terminals and a central computer. Using twisted pair cables to transmit balanced signals results in lower noise coupling, and since 485 has a wide common-mode voltage range, it allows communication rates of up to 50M bit/s or several kilometers of communication distance at lower speeds.

Due to the widespread use of 485, more and more standards committees are adopting the 485 standard as the physical layer specification for their communication standards. This includes ANSI’s SCSI (Small Computer System Interface), Profibus standards, DIN measurement bus, and China’s multifunctional electric energy meter communication protocol standard DL/T645.

The balanced transmission line standard 485 was developed in 1983 for data transmission interfaces between hosts and peripherals. The standard only specifies the electrical layer, while other aspects such as protocols, timing, serial or parallel data, and linkers are defined by the designer or higher-level protocols.

Initially, the 485 standard was defined as an upgrade to the flexibility aspects of the TIA/EIA-422 standard (hereinafter referred to as 422). Since 422 only supports simplex communication (Note: 422 uses two pairs of differential communication lines, one pair for sending and one pair for receiving, so data is transmitted in one direction on a single line), 485 allows multiple drivers and receivers on a single pair of signal lines, which is beneficial for half-duplex communication (see Figure 1). Like 422, 485 does not specify a maximum cable length, but under 24-AWG cable at 100kbps conditions, it can transmit 1.2km; 485 also does not limit the maximum signal rate, which is instead limited by the rise time and bit time ratio, similar to 232. In most cases, due to transmission line effects and external noise interference, cable length is more likely to limit signal rate than the driver.

2.1 Line Loading In the 485 standard, line loading must consider the termination and loading on the transmission line. Whether to match the termination of the transmission line depends on the system design and is influenced by the transmission line length and signal rate (generally, low-speed short distances may not require termination matching).

2.1.1 Transmission Line Termination Matching Transmission lines can be divided into two models: distributed parameter model [1] and lumped parameter model [2]. Testing which model the transmission line belongs to depends on the signal transition (rise/fall) time tt and the propagation time from the driver output to the end of the cable tpd.

If 2tpd ≥ tt/5, the transmission line must be treated according to the distributed parameter model, and proper termination matching must be handled; otherwise, the transmission line can be treated as a lumped parameter model, and termination matching is not required.

Note 1: Distributed parameter model – The voltage and current in the circuit are functions of time and depend on the geometric size and spatial location of the device.

Note 2: Lumped parameter model – The voltage between any two endpoints in the circuit and the current flowing into any device endpoint are completely determined and do not depend on the geometric size and spatial location of the device.

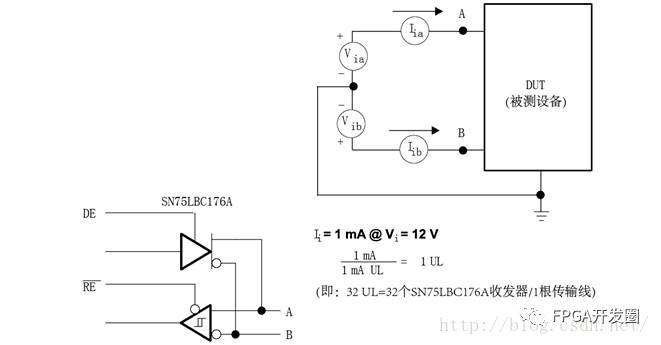

2.1.2 Unit Load Concept The maximum number of drivers and receivers connected to the same 485 communication bus depends on their load characteristics. The load of drivers and receivers is measured relative to a unit load. The 485 standard specifies that a maximum of 32 unit loads can be connected to a single transmission bus.

A unit load is defined as: in a 12V common-mode voltage environment, allowing a steady-state load current of 1mA, or in a -7V common-mode voltage environment, allowing a steady-state load current of 0.8mA. Unit loads may consist of drivers, receivers, and failure protection resistors but do not include AC termination matching resistors.

Figure 2 provides an example of unit load calculation for the SN75LBC176A transceiver. Since this device integrates the driver and receiver into a transceiver (i.e., the driver output and receiver input are connected to the same bus), it is difficult to separately obtain the driver leakage current and receiver input current. For calculation convenience, the receiver input impedance is considered to be 12 kΩ and a current of 1mA is given to the transceiver. This can represent one unit load, allowing up to 32 such loads on a transmission bus.

As long as the input impedance of the receiver is greater than 12kΩ, more than 32 such transceivers can be used on a single transmission bus.

Figure 2: Unit Load Concept

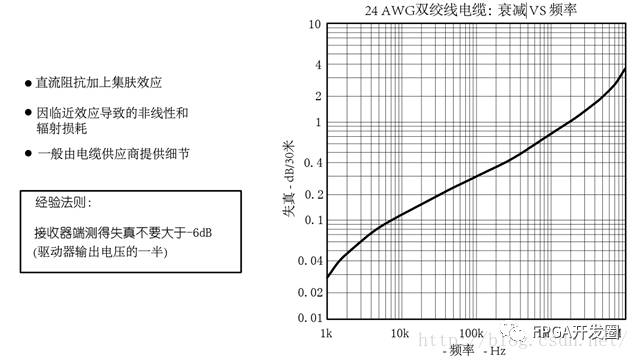

2.2 Signal Attenuation and Distortion A useful rule of thumb is that under maximum signal rate (in Hz) communication conditions, a signal attenuation of -6dB is allowed. Generally, cable suppliers provide signal attenuation charts. The curve shown in Figure 3 illustrates the relationship between 24-AWG cable attenuation and frequency.

Figure 3: Signal Attenuation

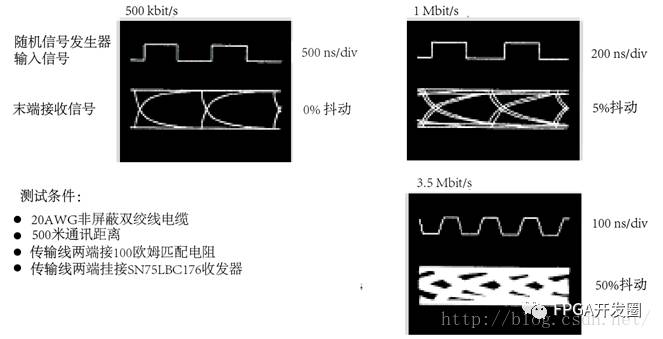

The simplest way to determine the extent of random noise, jitter, distortion, etc., affecting the signal is to use an eye diagram. Figure 4 shows the signal distortion at the receiving end under different signal rates using a 20AWG twisted pair cable at 500 meters. As the signal rate further increases, the impact of jitter becomes more pronounced. At 1Mbit/s, the jitter is about 5%, while at 3.5Mbit/s, the signal starts to be completely drowned out, and the transmission quality is severely degraded. In practical systems, the maximum allowable jitter is generally less than 5%.

Figure 4: 485 Signal Distortion vs Signal Rate

2.3 Fault Protection and Failure Protection 2.3.1 Fault Protection Like any system design, it is essential to habitually consider fault response measures, whether these faults are naturally occurring or environmentally induced. For factory control systems, there is usually a requirement to protect against extreme noise voltages. The differential transmission mechanism provided by 485, especially the wide common-mode voltage range, gives 485 a certain immunity to noise. However, in complex and harsh environments, its immunity may be insufficient. There are several ways to provide protection, and the most effective method is through current isolation, which will be discussed later. Current isolation can provide better system-level protection, but it is also more expensive. A more popular and cost-effective solution is to use diode protection. Using diodes instead of current isolation is a compromise that provides protection at a lower level. Examples of external diodes and integrated transient protection diodes are shown in the following figures:

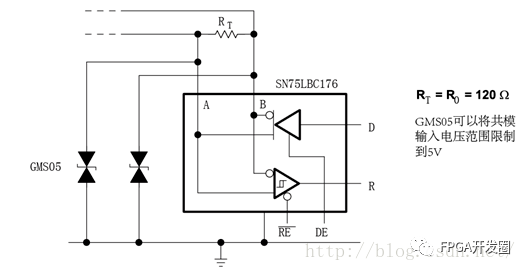

Figure 5 shows the SN75LBC176 transceiver with external diodes to prevent transient spikes.

Figure 5: Input Protection in Noisy Environments

RT is usually the termination resistor, equal to the cable characteristic impedance R0.

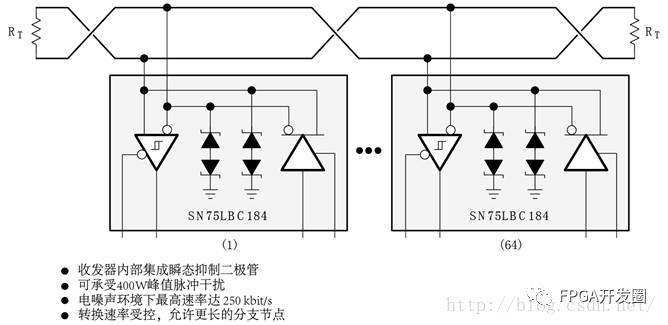

Figure 6 shows the SN75LBC184 485 transceiver with integrated transient suppression diodes, suitable for cases where full 485 functionality is desired but PCB space is limited. The SN75LBC184 integrates protective diodes internally to address high-energy electrical noise environments and can directly replace the SN75LBC176.

Figure 6: Integrated Transient Voltage Protection for Noisy Environments

2.3.2 Failure Protection Many 485 applications also require failure protection, which is very useful at the application layer and needs careful consideration and understanding.

In any interface system where multiple drivers/receivers share the same bus, drivers are mostly in an inactive state, referred to as the bus idle state. When the driver is in the idle state, the driver output is in a high-impedance state. When the bus is idle, the line voltage is in a floating state (meaning it is uncertain whether it is high or low). This may cause the receiver to be erroneously triggered to high or low (depending on environmental noise and the last polarity of the floating line). Clearly, this situation is undesirable. There needs to be relevant circuitry in front of the receiver to convert this uncertain state into a known, predetermined level, referred to as failure protection. Additionally, failure protection must prevent data errors caused by short circuits.

There are many ways to implement failure protection, including adding hardware circuits and using software protocols. Although implementing a software protocol is more complex, it is the preferred method. However, most system designers and hardware designers prefer to implement failure protection using hardware, so adding hardware circuits for failure protection is more commonly used.

Regardless of whether a short circuit or an open circuit occurs, the failure protection circuit must provide a clear input voltage to the receiver. If the environment in which the communication line is located is very harsh, then line termination matching is also necessary.

Currently, many manufacturers have begun to integrate some failure protection circuits (such as open-circuit failure protection) into the chip. Typically, these additional circuits simply add a large value pull-up resistor at the non-inverting input of the receiver and a large value pull-down resistor at the inverting input of the receiver. These two resistors are usually around 100KΩ, and these resistors, along with the termination matching resistor, form a potential driver that can only provide a few mV of differential voltage. Therefore, this voltage (receiver threshold voltage) is not sufficient to switch the receiver state. Using such internal pull-up and pull-down resistors allows the bus not to require termination matching but will significantly reduce the maximum signal rate and reliability.

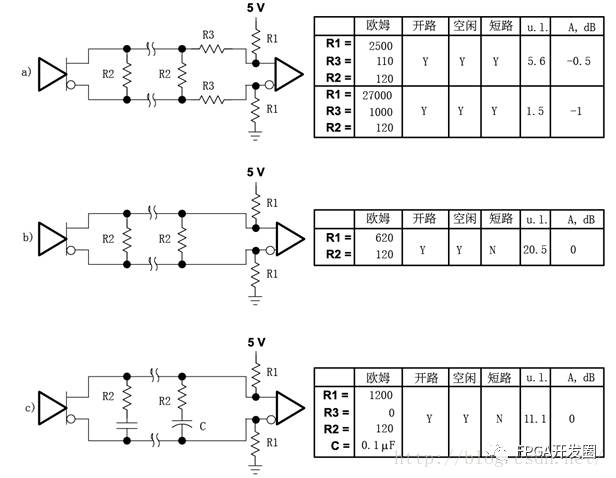

Figure 7 provides some common external failure protection circuits for 485 interfaces, each circuit strives to maintain the receiver input voltage above the minimum threshold and maintain a known logical state under one or more failure conditions (open circuit, idle, short circuit). In these circuits, R2 represents the transmission line impedance matching resistor and becomes part of the voltage driver: generating a steady-state bias voltage. It is assumed that each receiver represents one unit load.

The table on the right side of Figure 7 lists some typical resistor and capacitor values, types of failure protection provided, the number of unit loads used, and signal distortion. In the next section, the resistance values in the short-circuit failure circuit will be calculated to illustrate how to modify these resistance values to suit specific designs.

Figure 7: External 485 Failure Protection Circuits

To achieve short-circuit protection, more resistors are needed. When the cable is short-circuited, the transmission line impedance becomes zero, and the termination matching resistor is also shorted. Adding extra resistors in series at the receiver input can achieve short-circuit failure protection.

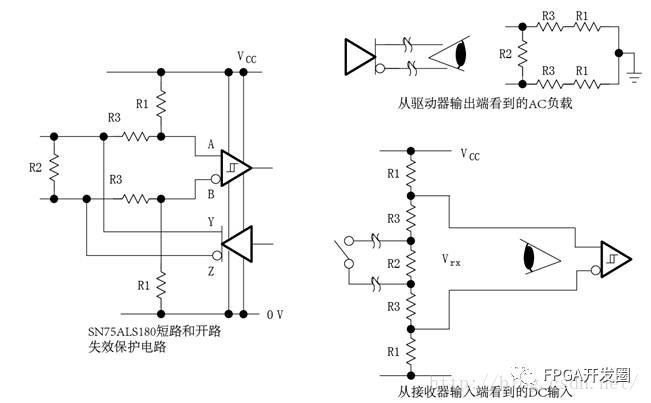

Figure 8 shows that the additional resistor R3 can only be used in cases where the driver and receiver are separated. Most current 485 drivers and receivers are integrated into one chip (known as a transceiver) and are internally connected to the same bus. This type of transceiver cannot use short-circuit failure protection. If short-circuit protection is needed, a transceiver with integrated short-circuit protection can be chosen, or separate driver and receiver devices, such as the SN75ALS180, can be used. If short-circuit failure protection circuits are used in transceivers, resistor R3 will cause additional distortion in the output signal. Separate driver and receiver devices like the SN75ALS180 will not have this issue, as the driver is directly connected to the bus, bypassing R3.

Figure 8: Short Circuit/Open Circuit Failure Protection Circuit

The following calculations will be performed on the resistance values. If the transmission line is short-circuited, R2 is removed from the circuit, and the input voltage at the receiver is: VID= VCC * 2R3 / (2R1 + 2R3)

For 485 applications, the standard specifies that the receiver can recognize input signals as low as 200mV. Therefore, when VID > VIT or VID > 200mV, a known state can be determined. This is the first design constraint: VCC* 2R3 / (2R1 + 2R3) > 200mV

When the transmission line is in a high-impedance state, the receiver is influenced by R1, R2, and R3, and its input voltage is: VID= VCC* (R2 + 2R3) / (2R1 + R2 + 2R3)

The second design constraint is obtained: VCC * (R2 + 2R3) / (2R1 + R2 + 2R3) > 200mV

The transmission line will be affected by the termination matching resistor R2 and the parallel effect of two times (R1+R3). The characteristic impedance Zo of the transmission line must match this, resulting in the third design constraint: Zo= 2R2 * (R1 + R3) / (2R1 + R2 +2R3)

Other design constraints include additional line loads provided by the failure protection circuit, signal distortion caused by R3 and R1, and receiver input resistance.

Note: 485 transceivers such as SN75HVD10 and newer products integrate short-circuit/open-circuit failure protection circuits internally.

2.4 Current Isolation Computer and industrial serial interfaces are often in noisy environments that may affect the integrity of data transmission. For any interface circuit, a method that has been tested to improve noise performance is current isolation.

In data communication systems, isolation means that there is no direct current flow between multiple drivers and receivers. Isolation transformers provide power to the system, and opto-isolators or digital isolator devices provide data isolation. Current isolation can eliminate ground loop currents and suppress noise voltages. Therefore, using this technique can suppress common-mode noise and reduce other radiated noise.

For example, Figure 9 shows a node of a process control system connected to a data logger and a main computer via an RS-485 link.

When a nearby motor starts, there can be a momentary difference in ground potential between the data logger and the computer, which usually causes a large current. If data communication does not use an isolation scheme, data may be lost, and in worse cases, the computer may be damaged.

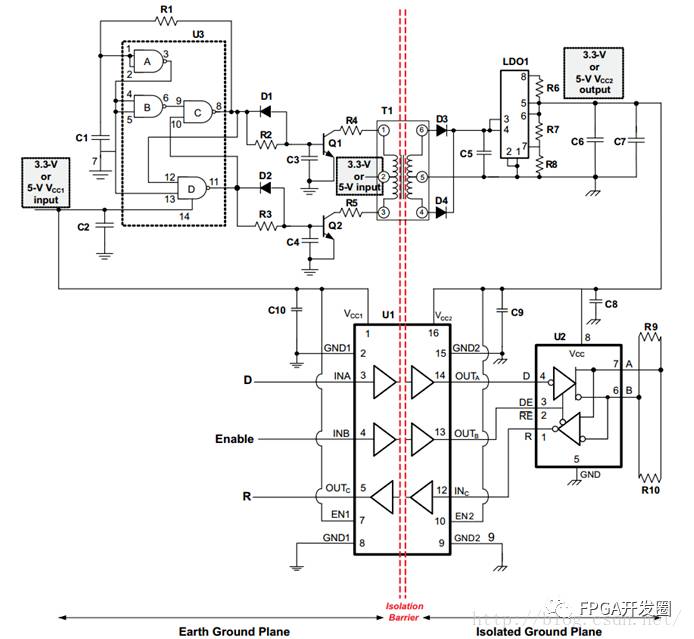

2.4.1 Circuit Description The schematic diagram shown in Figure 9 is a node of a distributed monitoring, control, and management system, which is commonly used in process control. Data is transmitted through a pair of twisted wires, and the ground uses a shield layer. Such applications often require low power consumption because many remote stations use batteries or require backup batteries (after power failure, the device needs to work for a certain time using backup batteries). Additionally, using low-power counting allows for small isolation transformers. As shown in Figure 9, the transceiver uses SN65HVD10; of course, any TI 3.3V or 5V RS485 transceiver, 3.3-V TIA/EIA-644 LVDS, or 3.3-V TIA/EIA-899 M-LVDS transceiver can use this circuit.

2.4.2 Operating Principle The example shown in Figure 9 can be used for 3.3V or 5V, with the power supply isolated by a transformer, and the data signal isolated by a digital isolator. Because the 485 transceiver requires an isolated power supply, an adjustable LDO regulator must be isolated. A NAND gate oscillator circuit can be used to drive the isolation transformer to achieve this function. The output voltage of the transformer is adjusted and filtered before being supplied to the low dropout linear regulator. In high EMI environments, this method is commonly used to prevent noise coupling from other long-distance powered electronic systems to the main power supply. TPS7101 is used to power other electronic components, providing up to 500mA of current. By adjusting the bias resistor R7, TPS7101 can output 3.3V or 5V, with specific resistance values listed in the BOM.

Data signal isolation is completed by a three-channel digital isolator ISO7231M. This device can provide 2.5KV (rms) voltage isolation and 50KV/us instantaneous discharge protection through a signal rate of 150Mbps.

Figure 9: 3.3V or 5V Isolated 485 Node (Left is Ground Plane, Right is Isolated Ground Plane)

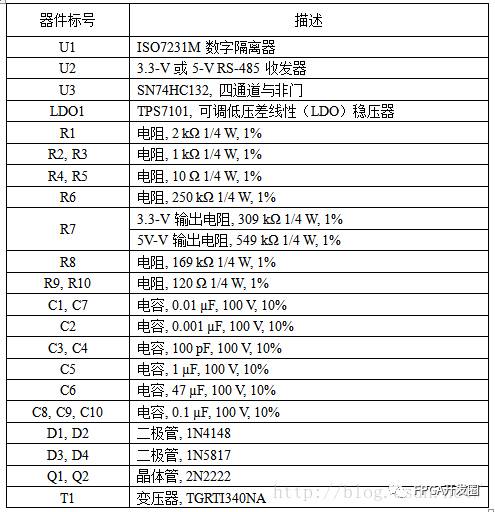

Table 1: BOM List for 3.3V or 5V Isolated 485 Node

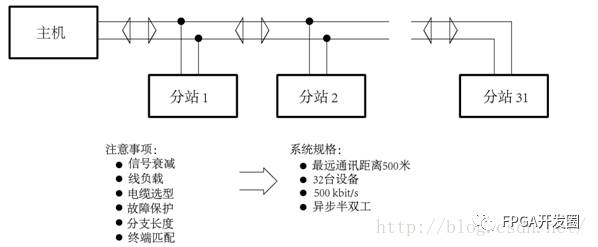

To gain more knowledge about 485 system design, a good approach is to look at specific examples. Consider a system: a factory automation system with a capacity of one main controller and several sub-stations, each capable of sending and receiving data. The system characteristics are as follows, with general specifications shown in Figure 10.

-

Farthest sub-station is 500 meters from the main controller

-

31 sub-stations (32 devices including the main controller)

-

Signal transmission rate of 500 kbit/s

-

Half-duplex communication

Figure 10: Example of Process Control Design

Devices following the 485 standard transmit data at 500 kbit/s, requiring that the driver output transition (rise/fall) time tt must not exceed 0.3 unit interval (UI), thus: tt ≤ 0.3 * UItt ≤ 0.3 * (1 /(500 * 103) ) = 600ns

If the cable signal transmission speed equals the speed of light in a vacuum, the signal transmission delay tpd is 3.33ns/m, multiplied by the transmission line length of 500 meters, resulting in 1667ns.

According to the formula in section 2.1, it can be determined whether the transmission line is a distributed parameter model or a lumped parameter model: if 2tpd ≥ tt/5, the transmission line is considered a distributed parameter model. Clearly, 3334 > 120, so the transmission line model in this example is a distributed parameter model. In industrial environments, this type of transmission line must have termination matching.

Regarding attenuation, although the fundamental frequency for a signal rate of 500 kbit/s is 250 kHz, we still calculate attenuation at 500 kHz because the signal actually contains higher frequency components. According to the empirical rule that maximum attenuation should not exceed -6dB, the maximum attenuation at the end of the 500-meter cable should be less than -6dB, which is 0.36dB/30 meters. We refer to the chart in Figure 3, which is provided by the cable manufacturer, showing the relationship between attenuation and frequency. The attenuation corresponding to a frequency of 500 kHz is slightly more than 0.5dB/30 meters, exceeding the design constraint of 0.14dB/30 meters. In this example, this is acceptable because slightly reducing the noise margin provided by conservative rules is permissible.

Source: zhzht19861011’s blog

Metamako adopts multi-FPGA: Successfully develops a new low-latency high-performance network working platform supporting parallel operation of APPs.

Design trade-offs using precision SAR converters and Σ-Δ converters in multiplexed data acquisition systems.

[Expert Q&A] How to calculate jitter on FCLK when using PLL residing in PS designed in XPS?

Testing 5G UFMC signal modulation transmission standards based on NI SDR and PXI platforms.

[Expert Q&A] PetaLinux PSS_REF_CLK binding issues.

Converting floating-point to fixed-point significantly reduces power consumption and costs.

[Expert Q&A] MIG 7 series timing analysis — Alarms on DQS pins — Input delay constraint loss.

Bittware applies Xilinx Virtex UltraScale+ VU13P to expand XUPVV4 PCIe card.

Massive MIMO and beamforming: Signal processing behind the buzzwords of 5G.

Hyundai Heavy Industries adopts NI HIL (hardware-in-the-loop) simulation to accelerate product development.

Xilinx fully programmable devices: Outstanding development platform for compute-intensive systems.

Will neural networks become the future trend of machine vision?

Solving the challenges of data processing and transmission in autonomous driving, the Zynq platform emerges.

Embodiment of intelligence and efficiency: Adaptive building models.

Surprising! Zynq reduces nitrogen oxide emissions from hybrid vehicles by 50%!

Baido Cloud FPGA standard development environment.

Must-see content | Learn how to obtain a Vivado license.

Strongly coming, Baidu deploys Xilinx FPGA on the new public cloud acceleration service.

HLS video tutorial 25: Course system introduction and summary.

In the era of big data, how to leverage both CPU and FPGA advantages simultaneously?

Scan the QR code to apply for joining