👆If you would like to meet regularly, feel free to star 🌟 and bookmark it~Source: ContentTranslated fromsemiwiki..

👆If you would like to meet regularly, feel free to star 🌟 and bookmark it~Source: ContentTranslated fromsemiwiki..

In an era where the scale, complexity, and diversity of artificial intelligence workloads are continuously increasing, chip manufacturers face mounting pressure to provide solutions that are not only fast but also flexible and programmable. Semidynamics recently announced the launch of Cervell™, a fully programmable neural processing unit (NPU) designed to handle scalable AI computing from the edge to the data center. Cervell represents a fundamental shift in the conception and deployment of AI processors. It is the pinnacle of Semidynamics’ evolution from modular IP components to a tightly integrated unified architecture, rooted in the open RISC-V ecosystem.

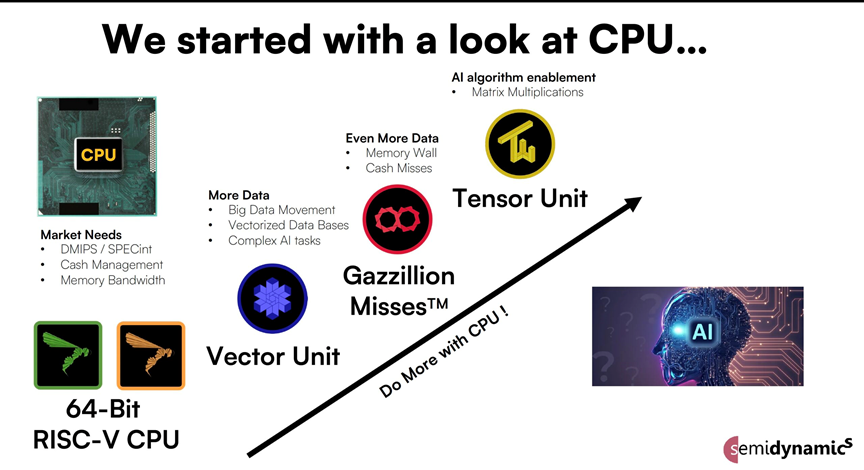

The architectural DNA of Cervell can be traced back to Semidynamics’ early innovations in customizable processor components. The company initially developed highly configurable 64-bit RISC-V CPU cores, allowing customers to customize logic and instruction sets according to their unique needs. These cores laid the foundation for control flow and orchestration in AI and data-intensive systems.

As AI workloads continue to evolve, Semidynamics introduced vector units and tensor units to enhance the performance of its RISC-V platform. The vector units can efficiently process large datasets in parallel, making them ideal for signal processing and inference tasks. Meanwhile, the tensor units provide native support for matrix-intensive computations, such as the core calculations in deep learning. Importantly, both units are designed to share the same register file and memory system, reducing latency and increasing integration.

These components form the basis of what the company calls an “integrated” IP architecture—a modular approach that allows chip designers to freely assemble computational units suited to their applications. However, it still requires developers to manage and orchestrate these units at the system level. Cervell changes this.

As AI models become increasingly large and complex, the demand for a more unified computing platform has become more apparent. Traditional computing methods—where the CPU is responsible for orchestration and discrete accelerators handle AI inference—are increasingly constrained by memory bottlenecks, data transfer latencies, and software complexity. The fragmented architecture requiring independent cores for control, vector operations, and tensor operations can no longer meet the performance and efficiency demands of modern AI workloads.

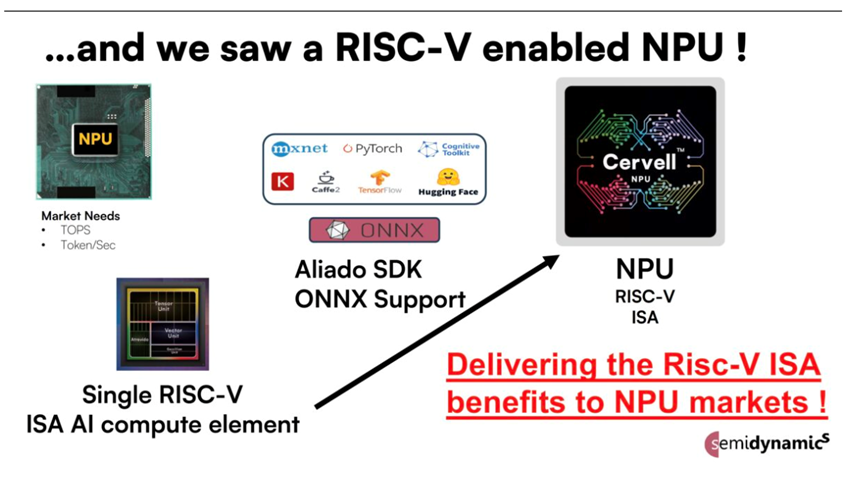

Moreover, as customers begin to prioritize programmability and long-term flexibility, fixed-function off-the-shelf NPUs are clearly inadequate. Semidynamics saw an opportunity to merge its modular IP modules into a single, cohesive computing architecture. Cervell is a RISC-V NPU that is not only scalable and programmable but also eliminates the need for fallback or offload operations.

The difference between Cervell and traditional NPUs is that it unifies computational components under a single architecture. Cervell does not view the CPU, vector units, and tensor engines as independent modules that need coordination; rather, it integrates these three components into a single processing entity. Each element operates within a shared, consistent memory model, meaning data can flow seamlessly between control logic, vector processing, and matrix operations without DMA transfers or synchronization barriers.

This integration allows Cervell to perform a variety of AI tasks without relying on an external CPU. Tasks that previously caused performance bottlenecks (such as control flow in transformer models or nonlinear functions in recommendation engines) can now be handled within the same core. Cervell supports up to 256 TOPS of computational power at maximum configuration, achieving data center-level inference performance while maintaining sufficient flexibility for low-power edge deployments.

Cervell eliminates the artificial boundaries between computation types, providing AI developers with a simplified software stack and more predictable performance. Its design challenges the status quo of traditional NPUs, which often rely on closed, fixed-function pipelines with limited configurability. In contrast, Cervell enables enterprises to customize the architecture according to their algorithms, resulting in truly differentiated solutions.

None of this would be possible without the open RISC-V instruction set architecture. RISC-V allows developers and chip designers to deeply customize the ISA, adding proprietary instructions while maintaining compatibility with the open software ecosystem. For Cervell, RISC-V is not just a technical enabler but a strategic differentiator.

Unlike proprietary ISAs that limit innovation to vendor roadmaps, RISC-V allows Cervell’s capabilities to evolve with customer needs. The openness of RISC-V means that enterprises can build processors that meet their business and technical requirements without being locked into a closed ecosystem. This flexibility is crucial in the field of artificial intelligence, where workloads are rapidly changing, and adaptability can become a competitive advantage.

While the integrated IP architecture laid the foundation for Cervell’s development, the differences between the two are significant. Previously, customers had to select and integrate CPU, vector, and tensor components themselves, which often led to complexities in toolchain and memory integration. Cervell integrates these elements into a pre-integrated NPU, simplifying deployment and scaling.

Cervell is a comprehensive product that includes a consistent memory subsystem, programmable logic across all computational layers, and software-ready interfaces that support common AI frameworks. Additionally, Cervell introduces performance scaling configurations from C8 to C64, ensuring that the same architecture can serve all applications from ultra-low-power IoT devices to multi-rack data center inference systems.

Reference Link

https://semiwiki.com/artificial-intelligence/356176-from-all-in-one-ip-to-cervell-how-semidynamics-reimagined-ai-compute-with-risc-v/

Click here👆 to follow and lock in more original content

*Disclaimer: The content of the article represents the author’s personal views, and Semiconductor Chip News reprints it only to convey a different perspective, which does not represent Semiconductor Chip News’s endorsement or support of that view. If there are any objections, please feel free to contact us.

Recommended Reading

100 Trillion, Invested in Semiconductors

Chip Giants, Market Value Plummets

Jensen Huang: HBM is a Technological Marvel

Jim Keller: RISC-V Will Definitely Prevail

The 10 Highest Valued Chip Companies Globally

If you like our content, please click“Looking” and share it with your friends~