NOR flash memory plays an irreplaceable role in artificial intelligence, automotive electronics, and industrial fields due to its advantages of high speed, reliability, and long lifespan. Currently, the commonly used planar NOR flash faces bottlenecks in size scaling below 50 nanometers, making it difficult to further enhance integration density, optimize device performance, and reduce manufacturing costs. To overcome these bottlenecks, researchers have proposed various three-dimensional NOR (3D NOR) devices based on polycrystalline silicon channels; however, the low mobility and slow read speed of polycrystalline silicon channels affect the overall performance of NOR devices. Recently, Researcher Zhu Huilong from the Integrated Circuit Pilot Process Research Center at the Microelectronics Institute (Note: University of Science and Technology of China, Class of 772) and his team developed a high-performance single-crystal channel 3D NOR flash memory device using a newly developed vertical transistor process. The stacked transistors not only leverage the high-performance advantages of single-crystal silicon channels but also benefit from the low manufacturing costs of three-dimensional integrated structures. This allows for a significant increase in memory integration density and storage capacity without the need to upgrade photolithography equipment, while achieving performance equal to or better than that of planar single-crystal silicon channel NOR flash devices. The team’s 3’3’2 three-dimensional NOR flash array successfully achieved normal read and erase operations, reaching read current and programming/erasing speeds comparable to those of two-dimensional NOR flash devices. Moreover, the new process is compatible with mainstream silicon-based processes, facilitating its application. The related results were published as a cover and “Editors Picks” article titled “A Novel 3D NOR Flash with Single-Crystal Silicon Channel: Devices, Integration, and Architecture” in the prestigious international microelectronics journal IEEE Electron Device Letters. PhD student Huang Weixing is the first author, and Zhu Huilong is the corresponding author. This is also the second time that the vertical nano-device research results from Zhu Huilong’s team have been selected as an “Editors Picks” article. This research was partially funded by the Chinese Academy of Sciences’ independent deployment project (Y7YC01X001). Paper link: https://ieeexplore.ieee.org/document/9906527

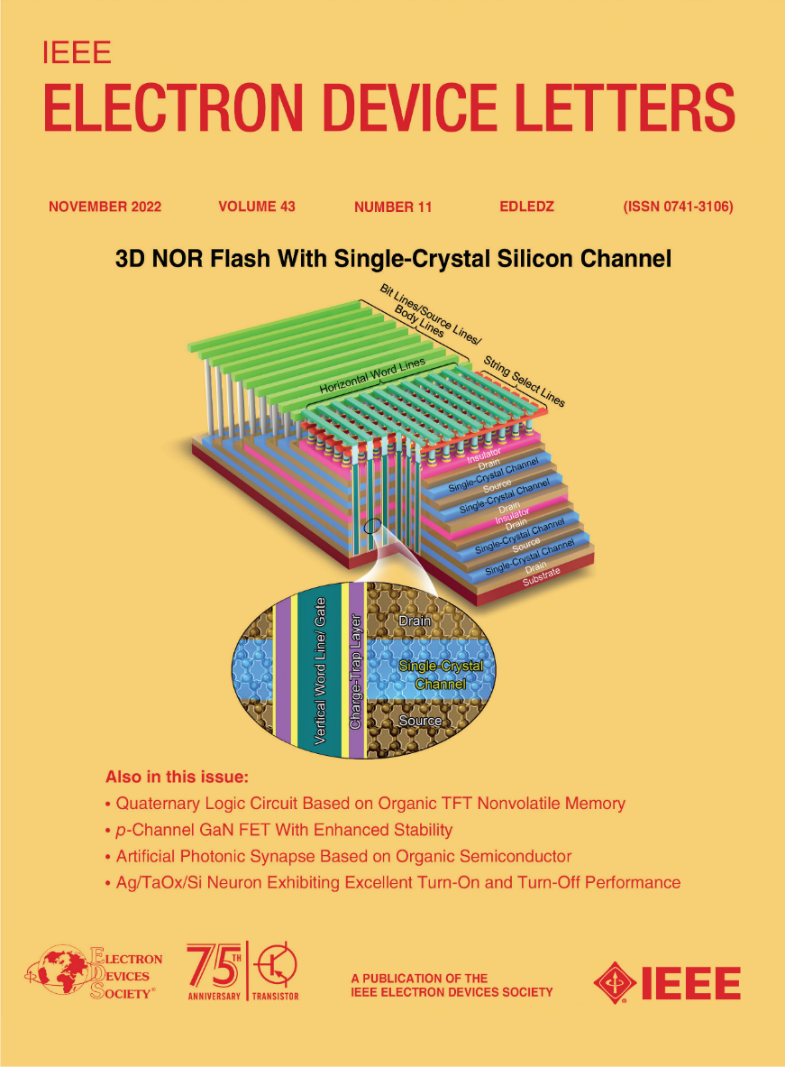

NOR flash memory plays an irreplaceable role in artificial intelligence, automotive electronics, and industrial fields due to its advantages of high speed, reliability, and long lifespan. Currently, the commonly used planar NOR flash faces bottlenecks in size scaling below 50 nanometers, making it difficult to further enhance integration density, optimize device performance, and reduce manufacturing costs. To overcome these bottlenecks, researchers have proposed various three-dimensional NOR (3D NOR) devices based on polycrystalline silicon channels; however, the low mobility and slow read speed of polycrystalline silicon channels affect the overall performance of NOR devices. Recently, Researcher Zhu Huilong from the Integrated Circuit Pilot Process Research Center at the Microelectronics Institute (Note: University of Science and Technology of China, Class of 772) and his team developed a high-performance single-crystal channel 3D NOR flash memory device using a newly developed vertical transistor process. The stacked transistors not only leverage the high-performance advantages of single-crystal silicon channels but also benefit from the low manufacturing costs of three-dimensional integrated structures. This allows for a significant increase in memory integration density and storage capacity without the need to upgrade photolithography equipment, while achieving performance equal to or better than that of planar single-crystal silicon channel NOR flash devices. The team’s 3’3’2 three-dimensional NOR flash array successfully achieved normal read and erase operations, reaching read current and programming/erasing speeds comparable to those of two-dimensional NOR flash devices. Moreover, the new process is compatible with mainstream silicon-based processes, facilitating its application. The related results were published as a cover and “Editors Picks” article titled “A Novel 3D NOR Flash with Single-Crystal Silicon Channel: Devices, Integration, and Architecture” in the prestigious international microelectronics journal IEEE Electron Device Letters. PhD student Huang Weixing is the first author, and Zhu Huilong is the corresponding author. This is also the second time that the vertical nano-device research results from Zhu Huilong’s team have been selected as an “Editors Picks” article. This research was partially funded by the Chinese Academy of Sciences’ independent deployment project (Y7YC01X001). Paper link: https://ieeexplore.ieee.org/document/9906527  Figure 1. The single-crystal silicon 3D NOR circuit architecture (top) and vertical channel transistor structure (bottom) featured on the cover of Electron Device Letters

Figure 1. The single-crystal silicon 3D NOR circuit architecture (top) and vertical channel transistor structure (bottom) featured on the cover of Electron Device Letters Figure 2. Single-crystal silicon channel 3D NOR device and electrical test results: (a) Device TEM screenshot (left) and channel magnified view (right), (b) Programming characteristics and (c) Erasing characteristics

Figure 2. Single-crystal silicon channel 3D NOR device and electrical test results: (a) Device TEM screenshot (left) and channel magnified view (right), (b) Programming characteristics and (c) Erasing characteristics