In power-off modules, it may be required for the register to latch data before power-off or to restore latched data after power-on, which necessitates a special unit known as the Retention Register.

The retention register consists of two sets of registers: the Main Register and the shadow register, where the shadow register is powered by an always-on supply.

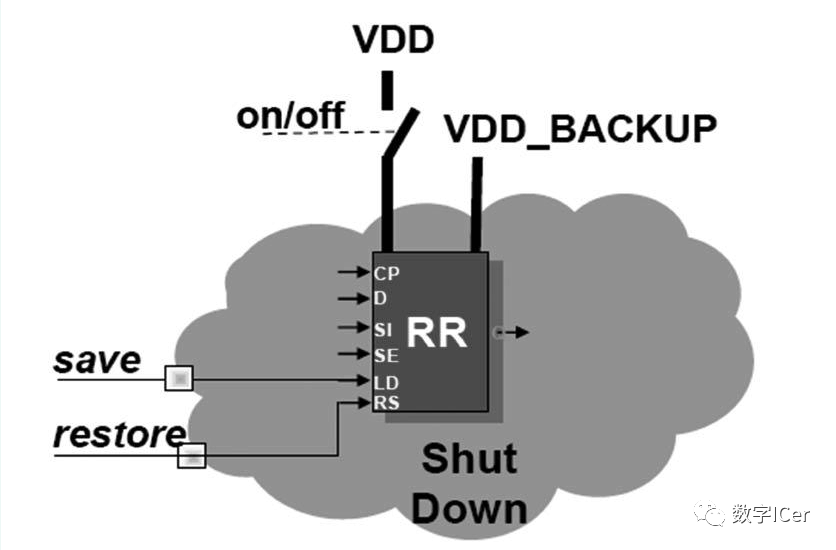

It has two power supplies: one for operational power when the module is not powered off, and another for power when the module is powered off. It also has two control signals, save and restore, used to control whether to latch data or restore data.

As shown in the figure above, this register requires two power supplies: one is the always-on VDD_BACKUP for the shadow register, and the other is the switchable VDD for the Main Register.

When it is necessary to retain the state, enabling the SAVE signal causes the value of the Main Register to be saved to the shadow register, and even if VDD is turned off, the value in the shadow register will be retained. When the module/IP is powered on again, the value from the shadow register can be written back to the Main Register by enabling the RESTORE signal.

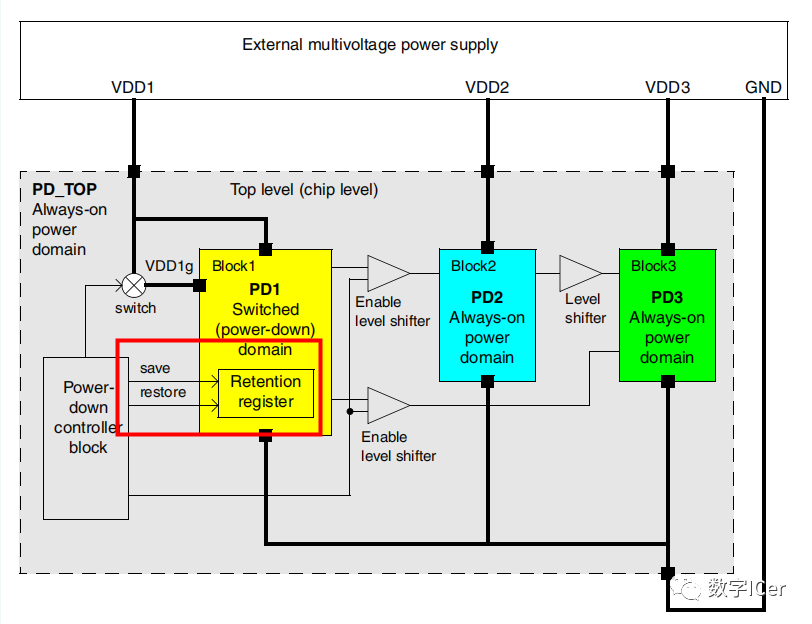

For power domains that can be turned off, as shown in Block1 below with PD1, all internal data is lost after the power is turned off. If it is desired to retain this data after power loss, there are several methods:

- Before power loss, store the internal data in external RAM, and read the data back after power is restored;

- Use a Retention Register within the power domain that can be turned off. Its internal structure is shown in the figure above; this register can save data from the Main Register to the internal Shadow Register before power is turned off using the SAVE signal. After power is restored, the data can be restored from the Shadow Register to the Main Register using the RESTORE signal.

Similar to various low-power cells mentioned earlier, the Shadow Register within the Retention Register is also an Always On Cell, which must have an always-on power supply. The Shadow Register is connected to the always-on power supply to ensure it operates correctly. Since it is always on, to achieve low power goals, high-threshold MOS transistors are often used internally to reduce leakage power in Power Down mode.

Aside from the Shadow Register, all other devices within the Retention Register use switchable power supplies. For high performance and fast data recovery, the Main Register may also use low-threshold transistors.

Compared to conventional registers, the Retention Register has a larger area, generally about 20% larger than a standard register, and if designed with better robustness, it may even exceed 50%. However, compared to other solutions, the speed of data recovery after power-on is very fast, and the operation is simple. Therefore, using a retention register requires special attention to the additional area and power consumption it brings. When the amount of data to be saved during power-off is large, the power consumption from the retention cell may undermine the overall low power effect.

QA1

In low power design, the retention register actually contains two registers, one called the shadow register powered by always-on power for restoring register values. Why not just use a regular register with always-on power? Wouldn’t that save one register?

Theoretically, a regular register could be used, but in practice, isolation must be considered. Just for clock, data, and reset, three isolation cells are needed, which increases power consumption and also affects timing.

The retention register internally considers these factors; as long as the signal entering the retention is always on, both the input and output speeds are very slow, so it does not affect timing.

QA2

What do retention registers refer to? How do they differ from regular registers, and what are their main functions?

The retention register has two sets of registers, one of which is the shadow register powered by always-on power. Before power down, the value of the main register is loaded into the shadow register, and after power up, the value is loaded back into the main register from the shadow register. Since the shadow register is only used to store data, it can be made relatively small, resulting in lower power consumption.

Using retention registers will increase additional leakage and should be used in conjunction with the system’s power-saving schemes, and it will also increase additional area.

QA3

It seems that retention registers have an additional shadow register, which appears to consume more power. How can it achieve power savings?

The key is that the shadow register in the retention registers consumes very little power to retain information, allowing the main register to be completely powered down, thus saving power.

QA4

What are the differences between the main and shadow registers in retention registers?

The main register has a larger area, operates at a higher voltage, and uses low-threshold voltage transistors, resulting in higher operating current, which ensures that the register operates quickly and has strong load capacity during normal operation.

The shadow register is relatively smaller, uses high-threshold voltage transistors, and operates at a lower drive voltage. Therefore, it consumes very little power.

Liberty Retention Register, for Reference Only

The lib description of retention registers specifies the power pins and input signals that control data saving and recovery.

It specifies which power pins are normal and can be powered down, and which are always-on pins used to retain data during power down.

cell(RETENTION_DFF) {

retention_cell:"ret_dff";

area : 1.0;

...

pg_pin(VDDB) {

voltage_name : VDDB;

pg_type : backup_power;

}

...

pin(RETN) {

direction : input;

capacitance : 1.0;

nextstate_type : data ;

related_power_pin :VDDB;

related_ground_pin:VSSG;

retention_pin (save_restore, "1" );

}

pin(Q) {

power_down_function:"!VDD+VSS";

related_power_pin : VDD ;

related_ground_pin : VSS;

direction : output;

...

References

- Synopsys® Low-Power Flow

- https://zhuanlan.zhihu.com/p/104415592

- https://www.shangyexinzhi.com/article/589062.html