Project Introduction

Path

<span>/home/IC_verify/project/opentitan</span>

Simulation Prerequisites and Notes

1.Before running the simulation, execute source ~/source_python to switch the default Python version.2.Do not modify any files in Bazel; only run the simulation. Otherwise, Bazel will determine that dependencies need to be updated, leading to errors when downloading libraries.

Simulation Method

IP Verification

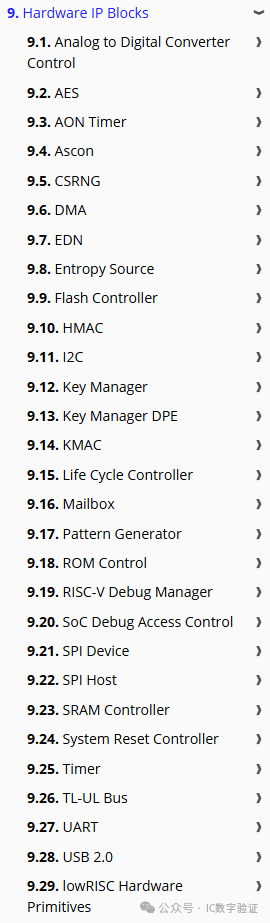

Hardware IP Blocks – OpenTitan Documentation

https://opentitan.org/book/hw/ip/index.html

IP List

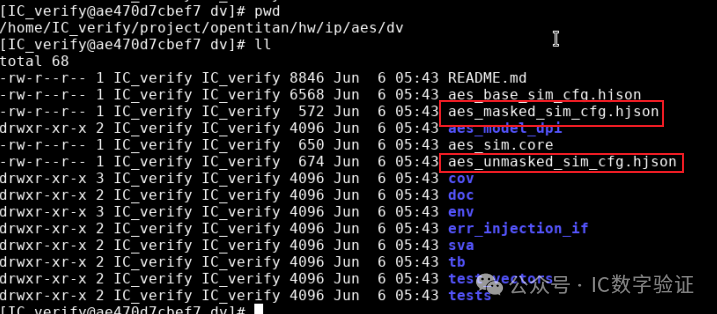

Taking AES as an example Directory:

Taking AES as an example Directory:

/home/IC_verify/project/opentitan/hw/ip/aes/dvCase List: (Find files ending with hjson) Testplan Breakdown for Cases

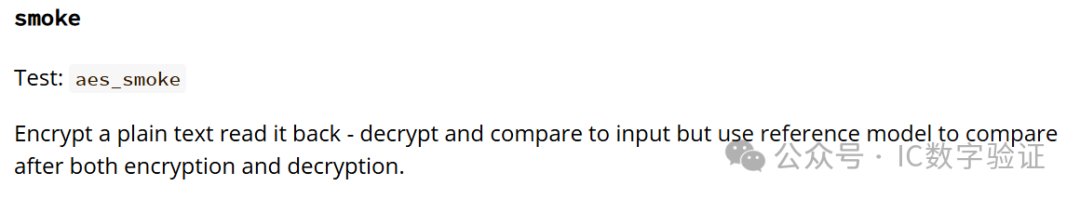

Testplan Breakdown for Cases

Testplan – OpenTitan Documentation

https://opentitan.org/book/hw/ip/aes/data/aes_testplan.html

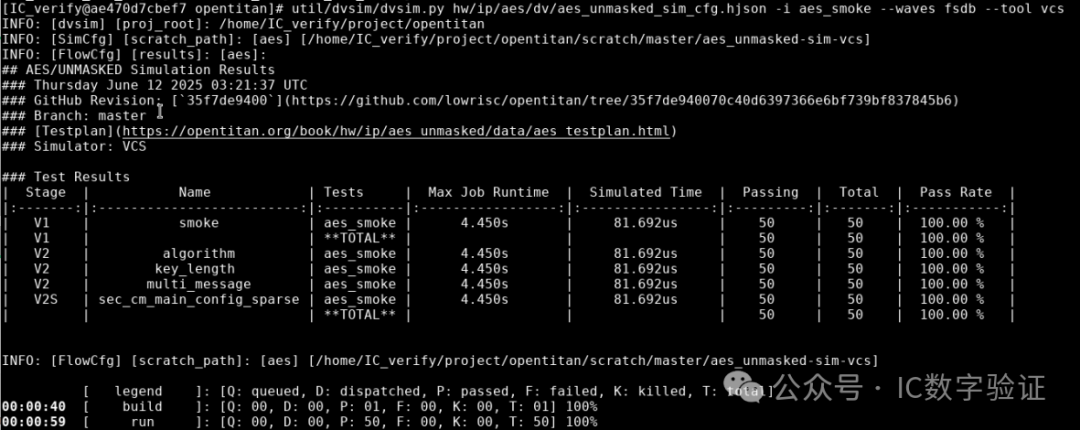

Simulation Command: (Select one of the aes_smoke)

util/dvsim/dvsim.py hw/ip/aes/dv/aes_unmasked_sim_cfg.hjson -i aes_smoke --waves fsdb --tool vcsSimulation Process:

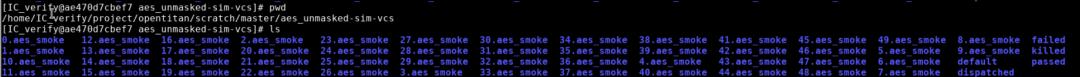

Simulation Directory:

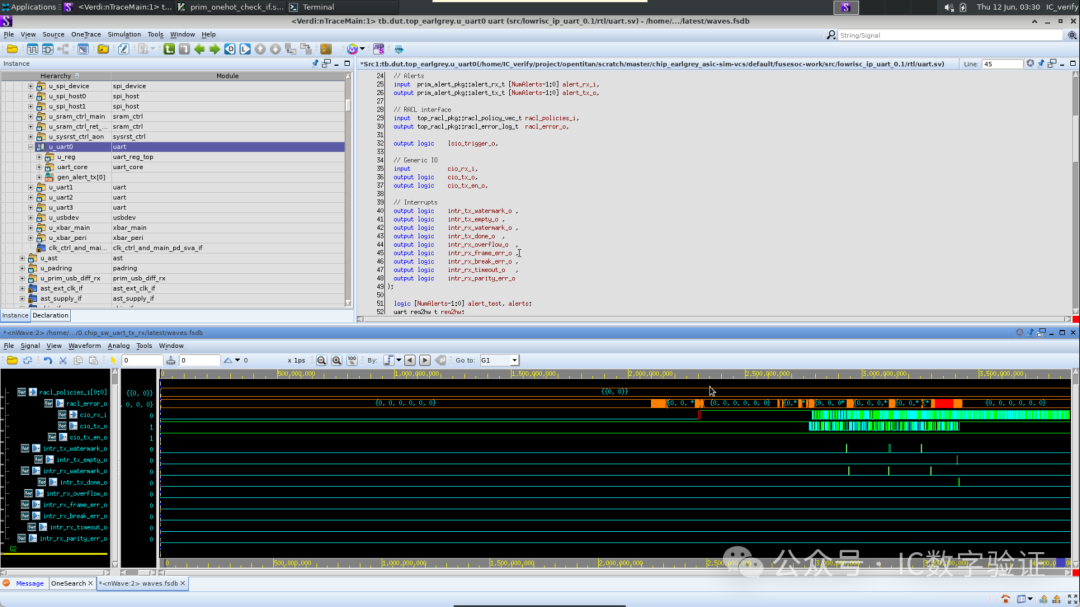

SoC Verification

Top Earlgrey – OpenTitan Documentation

https://opentitan.org/book/hw/top_earlgrey/index.html

Case List

https://opentitan.org/book/hw/top_earlgrey/data/chip_testplan.html

Simulation Command

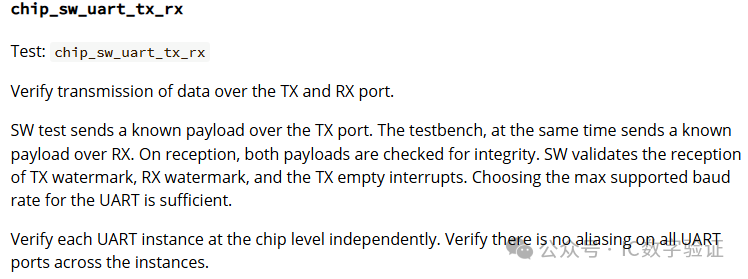

util/dvsim/dvsim.py hw/top_earlgrey/dv/chip_sim_cfg.hjson -i <Select case from the case list> --waves fsdbSelect one case for simulation

util/dvsim/dvsim.py hw/top_earlgrey/dv/chip_sim_cfg.hjson -i chip_sw_uart_tx_rx --waves fsdb

Waveform Debugging