01

Concept of Automotive Semiconductors

What Are Automotive Chips

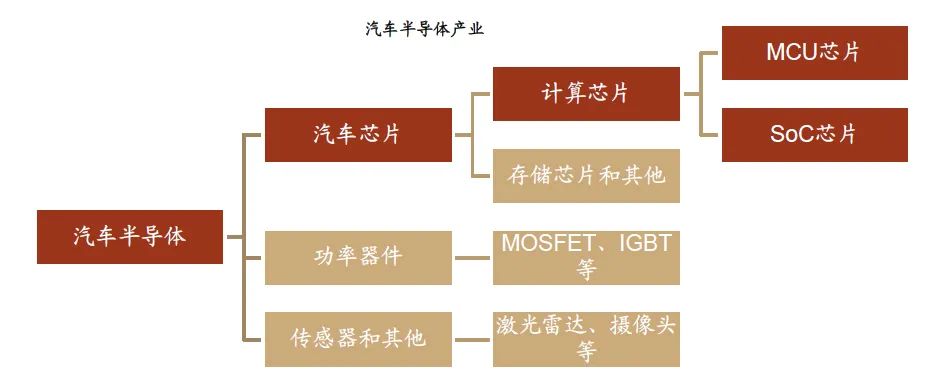

The concept of automotive semiconductors is broad, playing an important role in various fields such as automotive electrification, intelligence, connectivity, and sharing. They are categorized by function into automotive chips, power devices, sensors, etc.

Among them, chips, also known as integrated circuits, have a very high degree of integration; the automotive chips people often refer to are the computing chips in vehicles, which can be divided into MCU chips and SoC chips based on integration scale. Power devices, which have a lower degree of integration, belong to discrete devices, mainly including IGBTs, MOSFETs in electric vehicle inverters and converters. Sensors include radars, cameras, etc., in smart vehicles.

Automotive SoC Chips: Mobileye (Intel), NVIDIA, Qualcomm, Huawei, Horizon Robotics, Black Sesame, etc.;

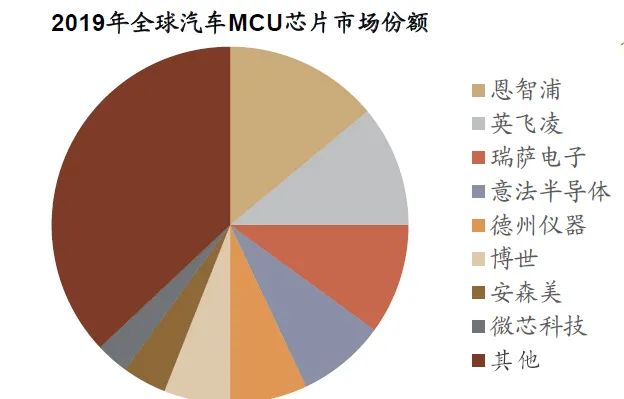

Automotive MCU Chips: NXP, Infineon, Renesas, STMicroelectronics, Texas Instruments, Bosch, ON Semiconductor, Microchip, etc.;

Automotive Power Devices: Infineon, ON Semiconductor, STMicroelectronics, CREE, BYD, CRRC Times Electric, etc.

02

Automotive Chips

Evolution from MCU Chips to SoC Chips

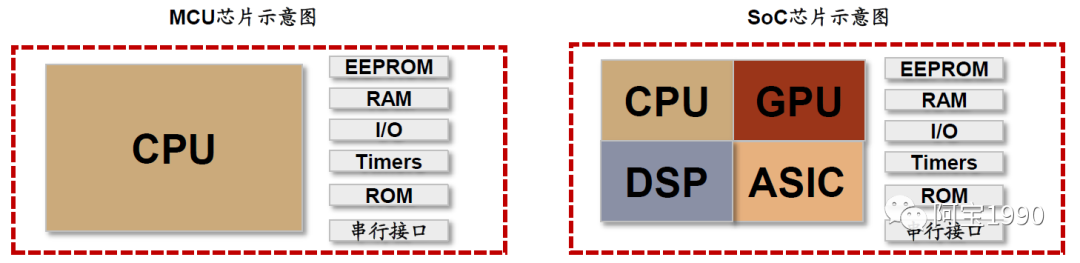

MCU chips refer to microcontroller units, also known as microcontrollers, which generally contain only one processing unit, the CPU; MCU = CPU + memory + interface units; while SoC is a system-on-chip, which generally contains multiple processing units; for example, SoC can be CPU + GPU + DSP + NPU + memory + interface units.

With the global upgrade in automotive consumption, the trend of automotive electrification is rapidly growing, and the number of electronic control units (ECUs) installed in vehicles continues to increase, which are generally MCU chips. The demand for automotive electronics and the pattern of the automotive MCU industry have led to a short-term shortage of automotive MCU chips.

The trend of automotive intelligence has two aspects: smart cockpits and autonomous driving, which brings a significant increase in demand for the smart architecture and algorithm computing power of vehicles, driving automotive chips to quickly transition to more powerful SoC chips.

As automotive electronics accelerate their penetration, the demand for automotive electronic control has rapidly increased, thus automotive MCU chips are still in a supply-demand imbalance, which has become even more pronounced against the backdrop of the pandemic.

Currently, the global automotive MCU chips are in a competitive landscape dominated by NXP, Infineon, Renesas, etc. The deep binding of chips with automakers leads to personalized customization and external foundry, exacerbating the difficulty of supply chain expansion. For example: Renesas with Toyota, Infineon with German automakers, etc.

Currently, there is a shortage of MCU chips in mature processes due to various reasons:

① COVID-19 pandemic + earthquake in Japan + winter storm in Texas + water shortage in Taiwan.

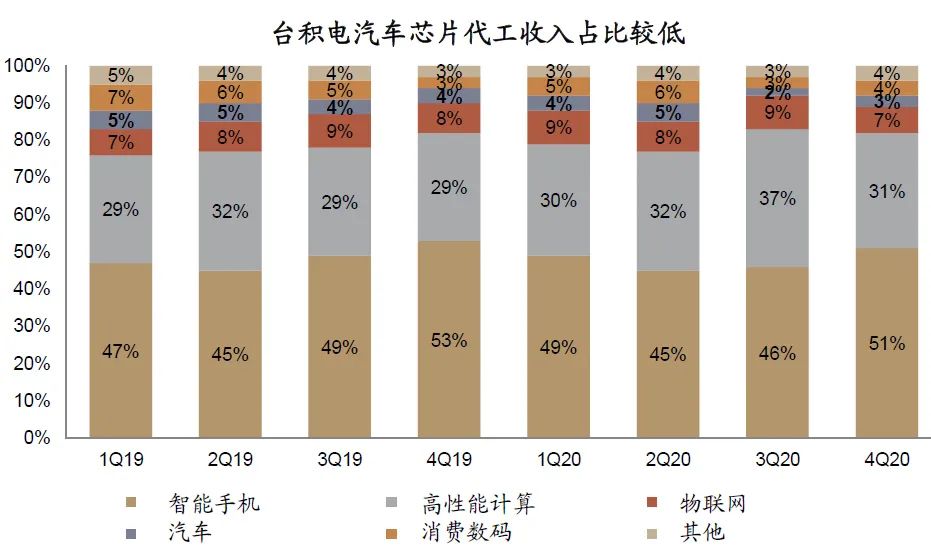

② Over 70% of global automotive MCU production comes from TSMC, while TSMC’s automotive chip foundry revenue accounted for only 3% in 2020. The MCU is in a mature process of 20~45nm (high-end autonomous driving SoC chips require more advanced 7nm processes), with low foundry profits and no motivation for expansion, leading to tight MCU capacity.

③ Upstream equipment manufacturers also produce fewer mature process production equipment due to low profits, making it difficult to supplement production equipment.

④ The explosion in sales of consumer electronics during the pandemic has led to capacity squeeze.

03

Automotive Intelligence

Smart Cockpit Drives SoC Chips Ahead

In vehicles, smart cockpits and autonomous driving are the two major application directions for SoC chips.

Compared to autonomous driving chips, smart cockpit chips are relatively easier to create. Even if the chip completely fails, it does not threaten the life safety of the driver and passengers, and the difficulty of passing vehicle regulations is lower. In the “war” of smart automotive chips, smart cockpit chips are the “outpost battle,” while autonomous driving chips are the “high ground in the war.”

The future integrated experiences represented by smart cockpits, such as “in-vehicle infotainment system + streaming rearview mirror + heads-up display system + full LCD instrument + vehicle networking system + in-vehicle occupant monitoring system,” will all rely on smart cockpit SoC chips.

The main competitors in the smart cockpit chip market include technology companies in the consumer electronics field such as Qualcomm, Intel, MediaTek, etc., mainly targeting the high-end market; in addition, there are traditional automotive chip manufacturers like NXP, Texas Instruments, Renesas Electronics, etc., whose products mainly target the mid-to-low-end market.

Currently, most domestic vehicles are equipped with cockpit domain controller chips based on Texas Instruments’ Jacinto6 and NXP’s i.mx6 and other previous-generation products. New entrants in the domestic market include Huawei (collaborating with BYD to develop Kirin chips for vehicles) and Horizon Robotics (the smart cockpit of Changan UNI-T and Li Auto ONE is based on the Journey 2 chip).

Autonomous Driving Drives “Architectural Transformation + Computing Power Enhancement,” Leading to Explosive Growth of SoC Chips

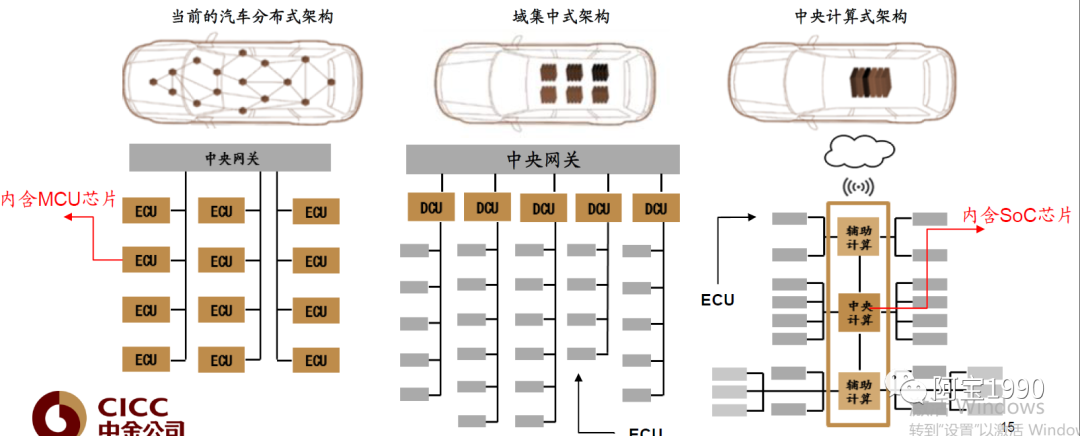

In traditional automotive distributed E/E architecture, the ECU (Electronic Control Unit) controls a single function, which can be satisfied with MCU chips. As the automation level of automotive electronics increases, the number of onboard sensors continues to rise, leading to bottlenecks in the traditional distributed architecture:

1) ECU algorithms can only process data from designated sensors, and computing power cannot be shared;

2) Adding new sensors and ECUs to the distributed architecture requires deploying a large number of communication buses within the vehicle, increasing assembly difficulty and vehicle weight;

3) The ECUs in the vehicle come from different suppliers, and developers cannot achieve unified programming and software upgrades, making it impossible to achieve whole vehicle OTA.

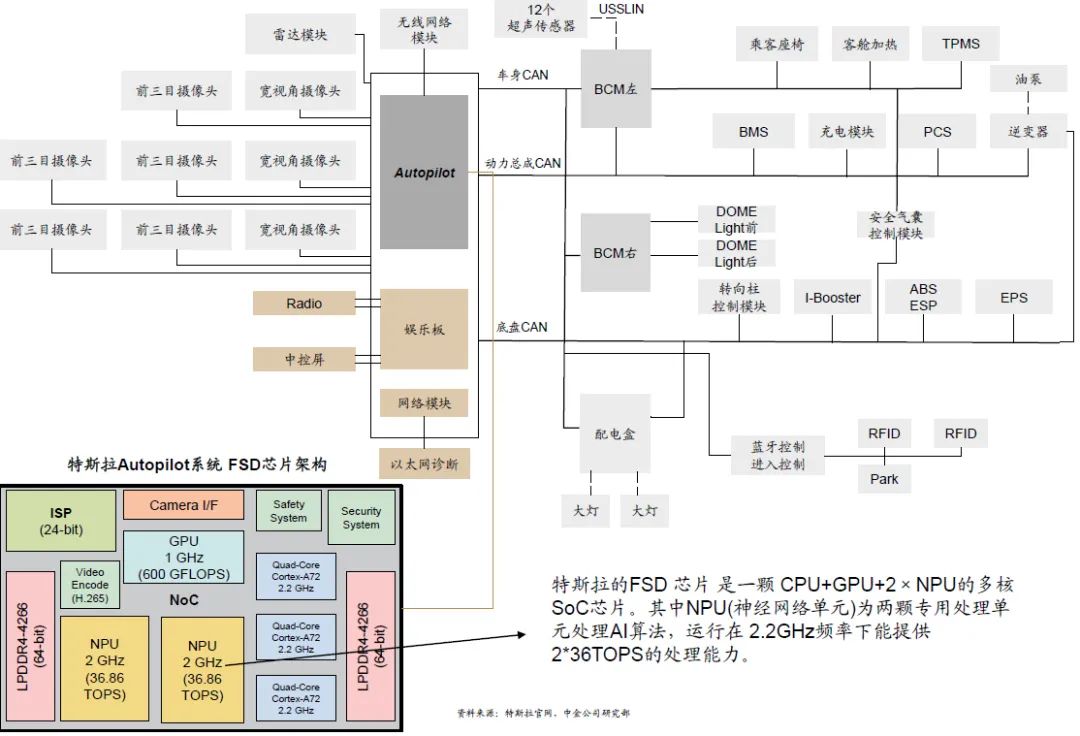

Under the centralized architecture of automotive domains, domain controllers (DCUs) and centralized computers need SoC chips. With the arrival of the era of intelligent connected vehicles, automotive electronic and electrical architecture reform pioneers like Tesla have taken the lead in adopting a centralized architecture, which uses one computer to control the entire vehicle and can effectively implement whole vehicle OTA software upgrades. Major automakers worldwide have recognized the trend towards centralized automotive control, although different automakers have different division schemes for control domains, the direction of architecture is the same towards domain control/centralized control. Domain controllers integrate the computing processor functions of many ECUs from the early stage, thus the demand for chip computing power is greatly enhanced compared to ECUs, and computing chips correspondingly need to use higher-powered SoC chips.

04

Autonomous Driving SoC:

The Pinnacle of Autonomous Driving Competition

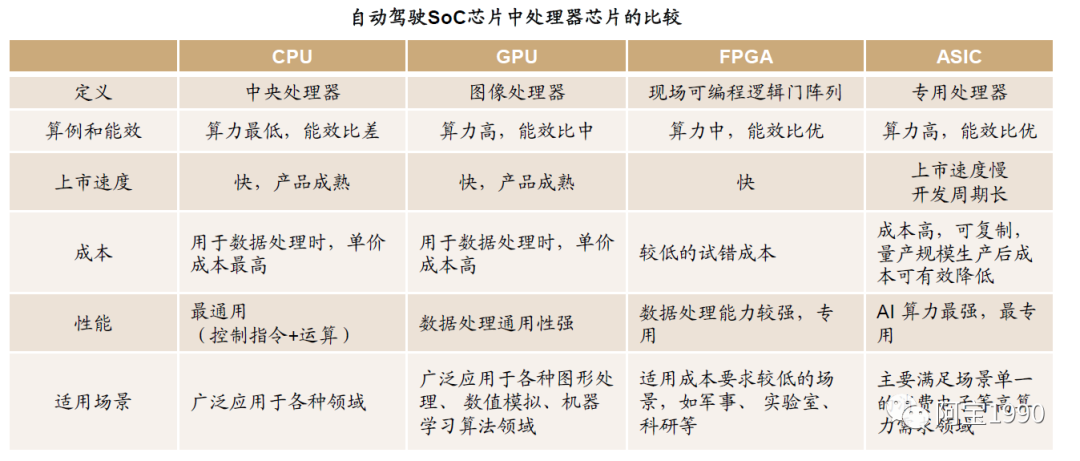

Processor chips are the computing core of MCU/SoC chips: divided into various types such as CPU, GPU, DSP, ASIC, FPGA, etc. Generally, MCU chips only contain a CPU, while SoC chips will have other types of processor chips in addition to the CPU.

CPU, GPU, DSP are all general-purpose processor chips:

CPU is the central processing unit, good at handling logical control. Optimizing and adjusting the CPU has led to the development of GPUs, which are good at processing image signals, and DSPs, which are good at processing digital signals.

ASIC is a dedicated processor chip, while FPGA is a “semi-dedicated” processor chip. Chips like EyeQ (Mobileye), BPU (Horizon Robotics), NPU (Cambricon, etc.) are specifically designed for AI algorithms (also known as AI chips) and fall under the category of dedicated chips (ASIC). FPGA refers to field-programmable gate arrays, which are “semi-dedicated” chips that possess hardware programmability.

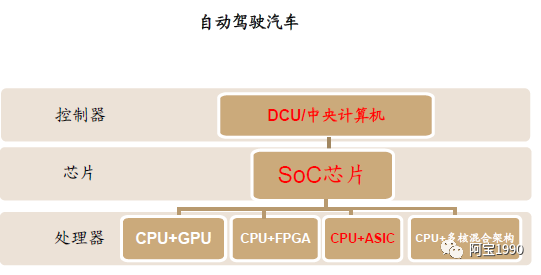

Autonomous Driving SoC Chips: “CPU + XPU” Architecture, with Multiple Choices for XPU

Autonomous driving chips refer to SoC chips that can achieve high-level autonomous driving, usually having a multi-core architecture of “CPU + XPU.” The L3+ level vehicle central computing platform needs to achieve 500+ TOPS of computing power, and chips that only have CPU processors cannot meet the demand. Autonomous driving SoC chips usually need to integrate one or more XPUs for AI computing in addition to the CPU. The XPUs used for AI computing can be GPU/FPGA/ASIC, etc.

GPU, FPGA, and ASIC each have their strengths in the field of autonomous driving AI computing: the CPU is usually the control center on the SoC chip, with strengths in scheduling, management, and coordination, but its computing power is relatively limited. For AI computing, people typically use GPU/FPGA/ASIC for enhancement:

1) GPUs are suitable for data-intensive applications for computing and processing, particularly good at handling CNN/DNN and other graph-based machine learning algorithms that are independent of sequence.

2) FPGAs have significant advantages for sequence-related machine learning algorithms such as RNN/LSTM/reinforcement learning.

3) ASICs are dedicated chips designed for specific user algorithm needs, having advantages such as smaller size, lighter weight, lower power consumption, improved performance, enhanced confidentiality, and reduced costs due to being “tailor-made.”

The mainstream processor architecture solutions (also known as technical routes) for autonomous driving SoC chips in the market are as follows:

① Technology companies represented by NVIDIA and Tesla use a CPU + GPU + ASIC solution for their autonomous driving SoC chips.

② Emerging technology companies like Mobileye and Horizon Robotics focus on developing and selling dedicated AI chips for autonomous driving, using a CPU + ASIC solution.

③ Internet companies represented by Waymo and Baidu adopt a CPU + FPGA (+ GPU) solution for autonomous driving algorithm development.

Solution ①: NVIDIA and Tesla’s “CPU + GPU + ASIC” Solution

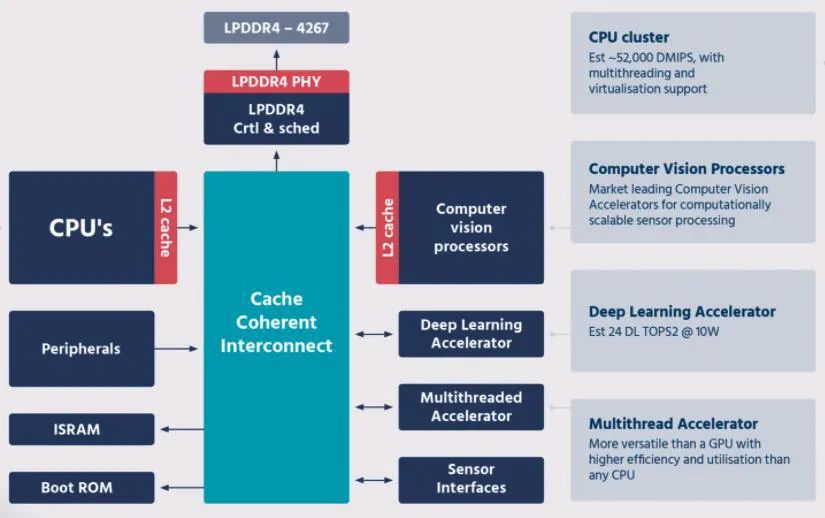

NVIDIA Xavier uses a GPU as the computing core: it mainly has four modules: CPU, GPU, Deep Learning Accelerator (DLA), and Programmable Vision Accelerator (PVA). The largest area is occupied by the GPU, followed by the CPU, and finally supplemented by two ASICs: one for inference (DLA) and another for accelerating traditional CV (PVA).

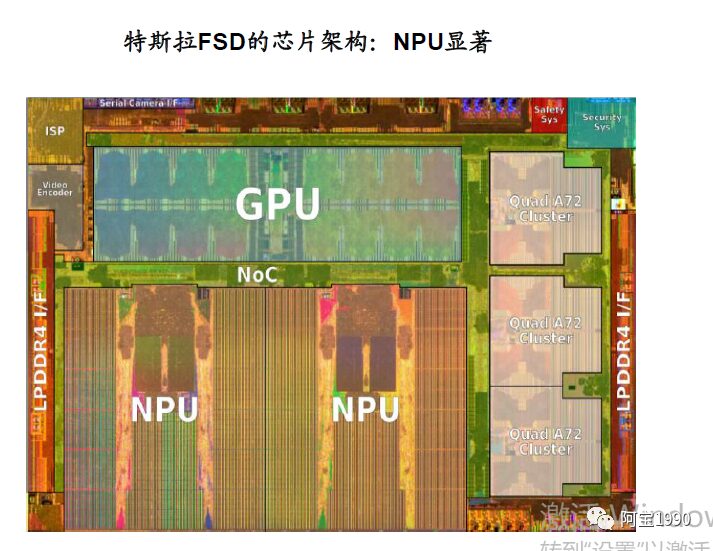

Tesla FSD uses NPU (a type of ASIC) as the computing core: it has three main modules: CPU, GPU, and Neural Processing Unit (NPU). The most important and largest area is the self-developed NPU (which is an ASIC), mainly used to run deep neural networks. The GPU is mainly used to run the post-processing part of the deep neural network.

Solution ②: Mobileye EyeQ5’s “CPU + ASIC” Architecture

EyeQ5 mainly has four modules: CPU, Computer Vision Processors (CVP), Deep Learning Accelerator (DLA), and Multithreaded Accelerator (MA). Among them, CVP is an ASIC designed for many traditional computer vision algorithms. Since its establishment, Mobileye has been known for its CV algorithms and has achieved low power consumption by using proprietary ASICs to run these algorithms.

Horizon Robotics has independently designed and developed AI-specific ASIC chips: Brain Processing Unit (BPU), which can provide embedded AI solutions combining software and hardware at the device end. The Journey 2 chip based on BPU can provide over 4 TOPS of equivalent computing power, with a typical power consumption of only 2 watts, efficiently and flexibly achieving processing of various AI tasks, enabling real-time detection and accurate identification of multiple targets. The Journey 2 fully demonstrates the powerful flexibility of the BPU architecture, empowering automotive intelligence comprehensively.

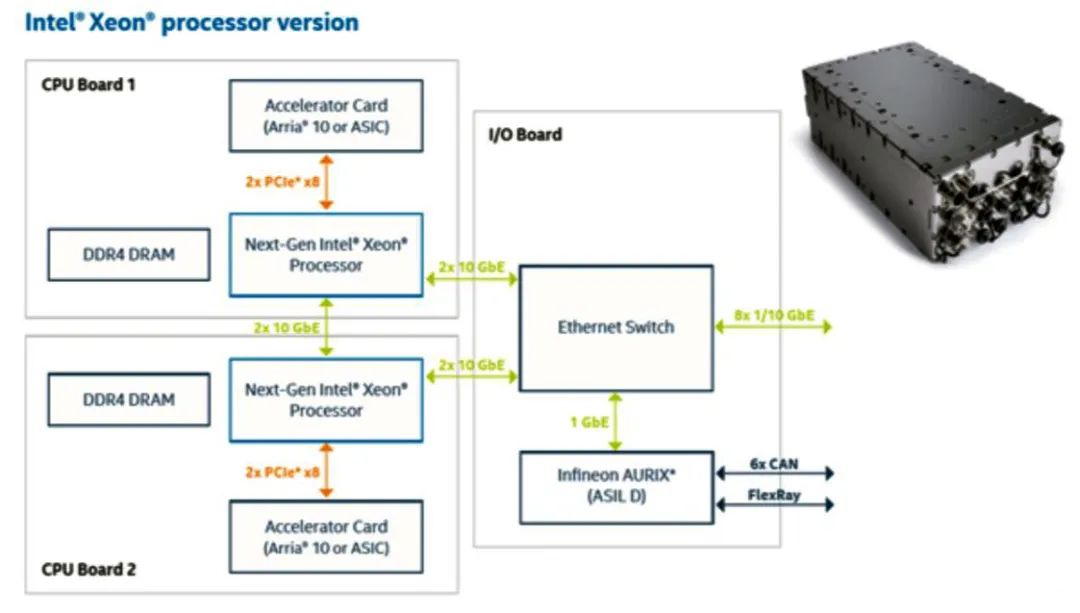

Google Waymo adopts a “CPU + FPGA” solution: Waymo’s computing platform uses Intel Xeon 12-core or higher CPUs, paired with Altera’s Arria series FPGAs, and uses Infineon’s Aurix series MCUs as the communication interface for the CAN/FlexRay network.

Among them, the Arria series FPGAs may be replaced by dedicated ASICs in the future after the autonomous driving algorithms are solidified.

“CPU + ASIC” Solution Will Become the Mainstream of Future Commercialization

Industry insiders believe that until autonomous driving algorithms are fully mature, the CPU + GPU + ASIC architecture will still be mainstream. After autonomous driving algorithms are completely mature, custom low-power, low-cost dedicated autonomous driving AI chips (ASICs) will gradually replace high-power GPUs, and the CPU + ASIC architecture will become mainstream.

GPUs were originally designed to support image processing for large computer games and are suitable for training machine learning neural networks. However, the downside of GPUs is their high power consumption and low energy efficiency ratio. In terms of computing energy efficiency ratio, ASIC > FPGA > GPU > CPU. Dedicated AI chips (ASICs) are specifically designed for AI algorithms, with advantages such as smaller size, lower power consumption, higher reliability, and improved performance. The downside is high initial R&D costs and long cycles.

FPGAs are suitable for algorithm development testing but do not have cost advantages in mass production. AI processors developed using FPGAs have high performance, low energy consumption, and hardware programmability features, but FPGAs do not have cost advantages in large-scale mass production. Therefore, companies that previously adopted the CPU + FPGA solution are mainly those focused on autonomous driving algorithm software development, such as Baidu and Waymo.

References:

China International Capital Corporation Analysis Report

-

In-Depth Interpretation of Automotive Domain Controllers

-

Some Observations on Smart Driving Domain Controllers

-

Focus on Two Sessions | Changes in Trends of Autonomous Driving Proposals

-

Weekly Report of the Autonomous Driving Industry (03.14)

-

February Industry Financing Information Summary | 25 Companies Successfully Raised Funds, Disclosing Amounts Exceeding 16 Billion Yuan

-

Smart Transportation, Perception First

-

New Breakthroughs in Sensor Fusion: No Panic Even If Autonomous Vehicle Cameras Fail

-

Autonomous Driving Enters the Over 10 Trillion Smart Transportation Market!

-

February Industry Focus and Company Dynamics Summary

-

Understand the Eight Major Systems of ADAS in One Article