According to reports from Fast Technology, the semiconductor industry is facing unprecedented technical challenges, with the tape-out success rate for chips dropping to a historic low!

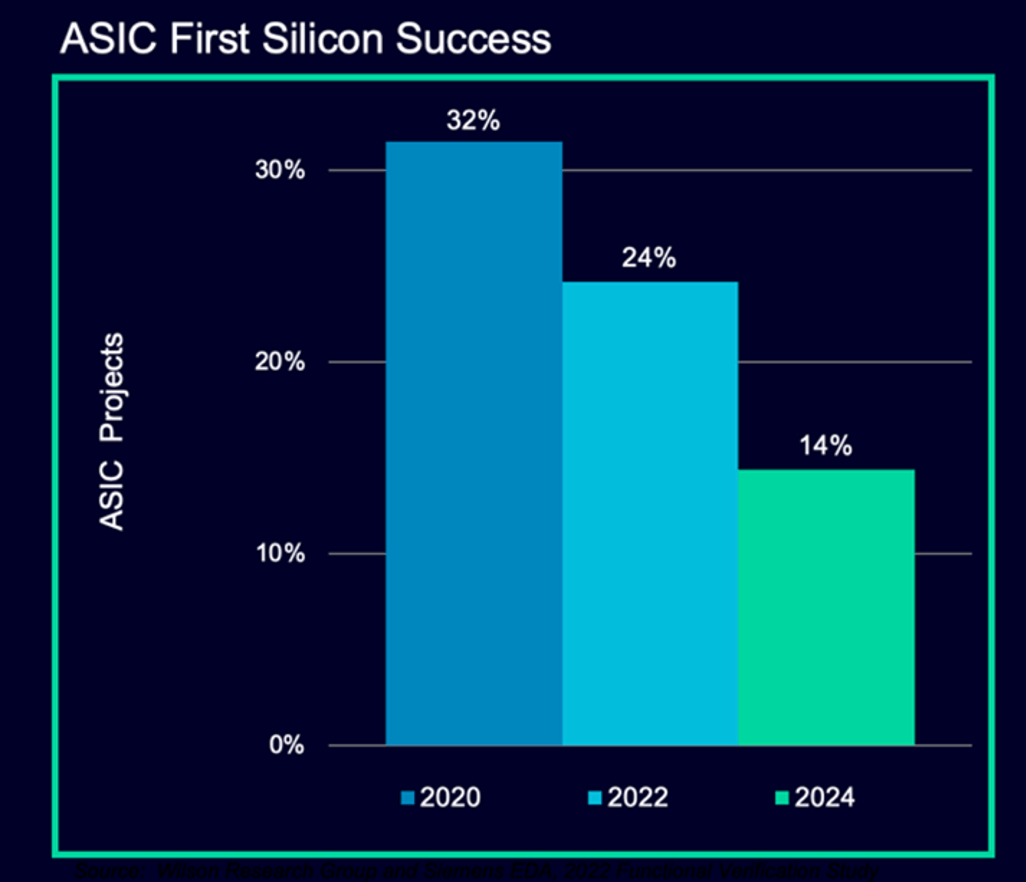

Data from Siemens, an Electronic Design Automation (EDA) company, shows that the success rate of the first tape-out (tape-out) for chips has fallen to a historic low of 14%, a significant decrease from 24% two years ago.

This means that among ten chip design companies, eight will fail at the first tape-out, such a high failure rate is indeed shocking.

The cost of failure is significant: a single tape-out can result in losses of tens of millions, putting small and medium-sized design companies at risk of survival.

Furthermore, with the arrival of 2nm technology, improving chip yield under advanced process technology is also very challenging. The chip industry is facing a major crisis.

IC design professionals analyze that this is mainly due to the increasing complexity of chips and changes in corporate development models; in the future, specialization and outsourcing to ASIC companies will become a trend.

Tape-out is a critical test for chip design, as it refers to handing over the completed chip design to a foundry for sample production to verify whether the design meets expectations; it is a key milestone in chip development.

If it fails, not only will the initial investment of tens of millions in R&D costs be wasted, but it may also result in missing market opportunities.

Additionally, some chip failures occur due to overly casual design processes; not all chip failures are due to functional issues. If the tape-out returns with a speed that is 10% slower than expected or power consumption that is 10% higher than expected, it may lack competitiveness in the market, necessitating a re-tape-out.

Many chip giants have stumbled during tape-out, such as AMD’s Bulldozer architecture chip and Qualcomm’s Snapdragon 810 chip.

So, why is there such a high tape-out failure rate?

First, chips are becoming increasingly complex. As chips need to integrate more functions and transistors, the design difficulty has increased exponentially. Previous chip designs may have only needed to consider a few core modules, but now chips, especially mobile processors and AI chips, need to integrate multiple complex functional units such as CPU, GPU, and NPU, while also considering power consumption, heat dissipation, and performance balance. This places extremely high demands on chip design engineers, and any small design error can lead to tape-out failure.

Second, the verification cycle is out of control. The time for custom design verification has skyrocketed; custom chips are designed for specific data types, algorithms, or application scenarios, making chip design and verification work exceptionally cumbersome, while the market window continues to compress.

Finally, the cost death spiral. The skyrocketing costs of advanced process tape-out fees have trapped failing companies in a vicious cycle of “the more tape-outs, the more losses.” Tape-out is just the beginning of chip production; subsequent production stages are equally challenging, and the issue of low chip yield is also a significant obstacle to the development of the chip industry.

Disclaimer: The content and views are for reference only and do not constitute any investment advice; the information cited in the text comes from public sources.

END

Click the public account below to follow and add “Star Mark”

to receive new content updates in real-time.

Don’t miss out on exciting content.