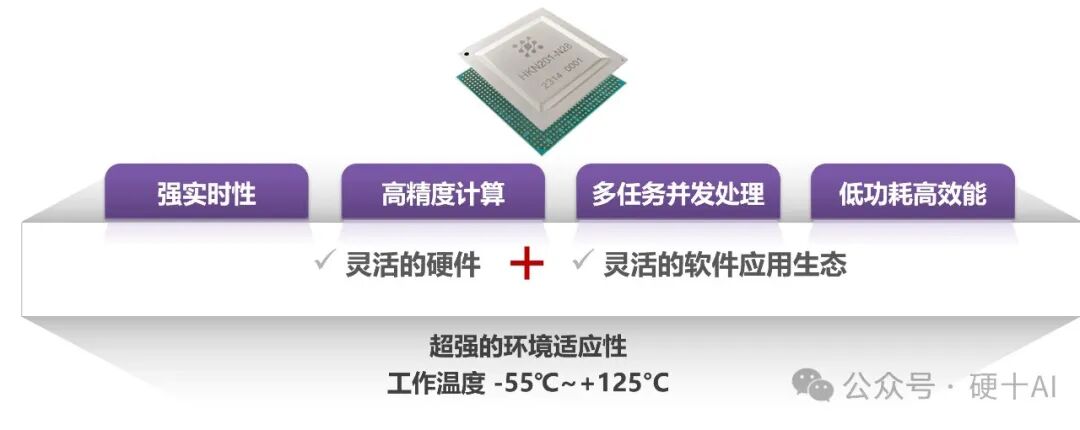

The Xiangteng NPU chip HKN201 is a fully domestic autonomous defined neural network chip, aimed at strong real-time, high-performance, and high-concurrency application scenarios. 1. Chip Specifications

1. Chip Specifications

-

Overview of Chip Specifications

-

Chip Specification List

|

AI Processor |

4-core 2048MAC NPU core Clock frequency 1GHz |

|

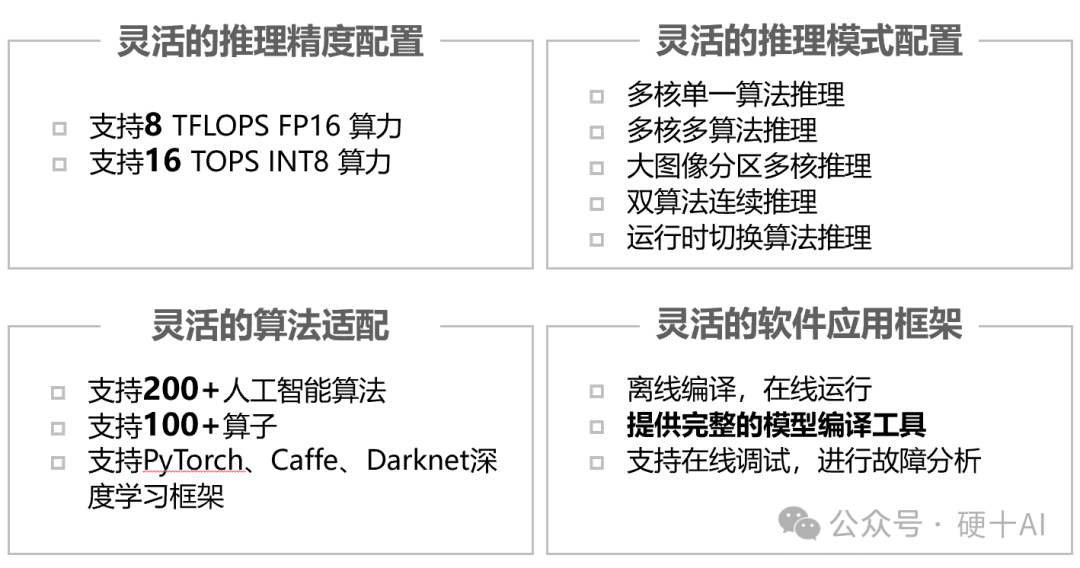

AI Computing Power |

16TOPS INT8 8TFLOPS FP16 |

|

Software Specifications |

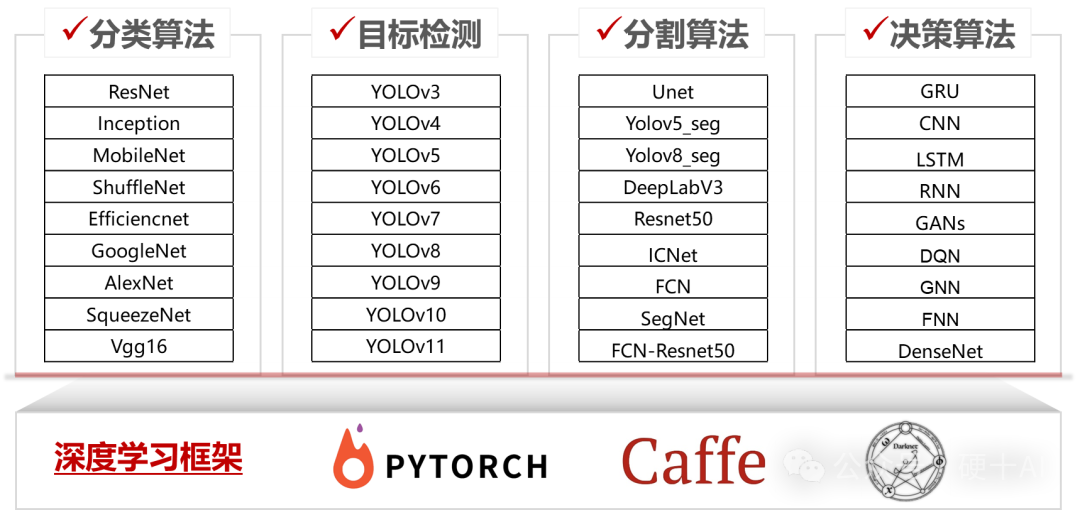

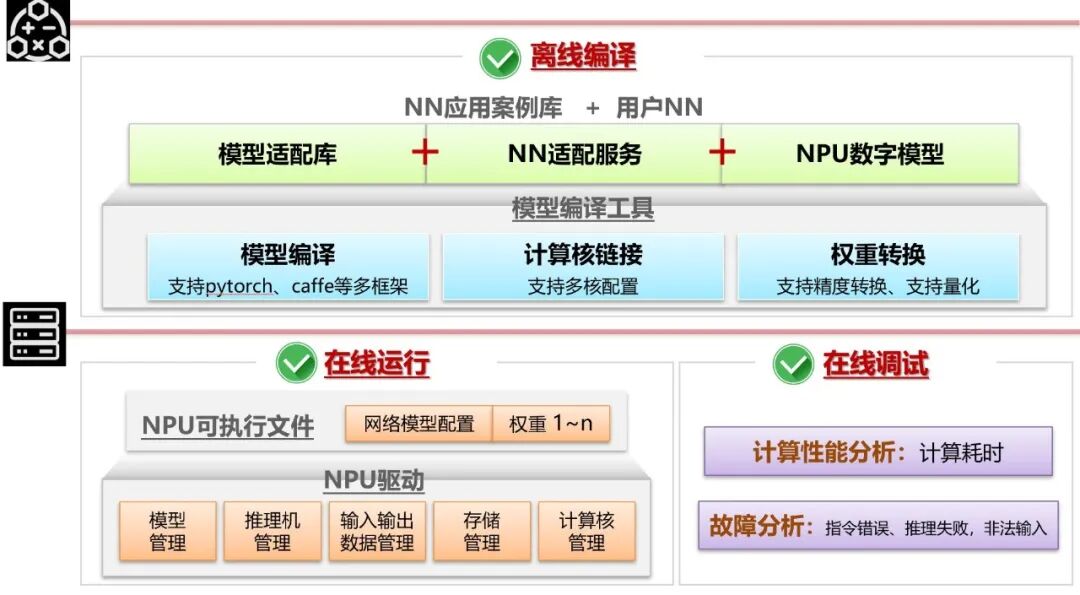

Supports PyTorch, Caffe, Darknet deep learning frameworks Supports over 100 operators Supports over 200 algorithms Supports 5 working modes with flexible runtime switching |

|

Software Compatibility |

Supports Kirin, Tongxin, Linux, Euler, HarmonyOS, etc.,supports running without OS Supports Feiteng, Longxin, Shenwei CPUs, RK3588, T527 SoCs Supports Windows systems |

|

Hardware Specifications |

Package type: FC_PBGA package Pin count: 896 pins Dimensions: 25mm * 25mm Weight: 4.89g |

|

High Speed Interface |

Main interface:supports 1 PCIe, Gen3X4 Storage interface: supports 2 DDR4, single channel width 64bit/2666Mbps |

|

Typical Power Consumption |

Typical scenario < 8W |

|

Operating Temperature |

-55℃ ~ +125℃ |

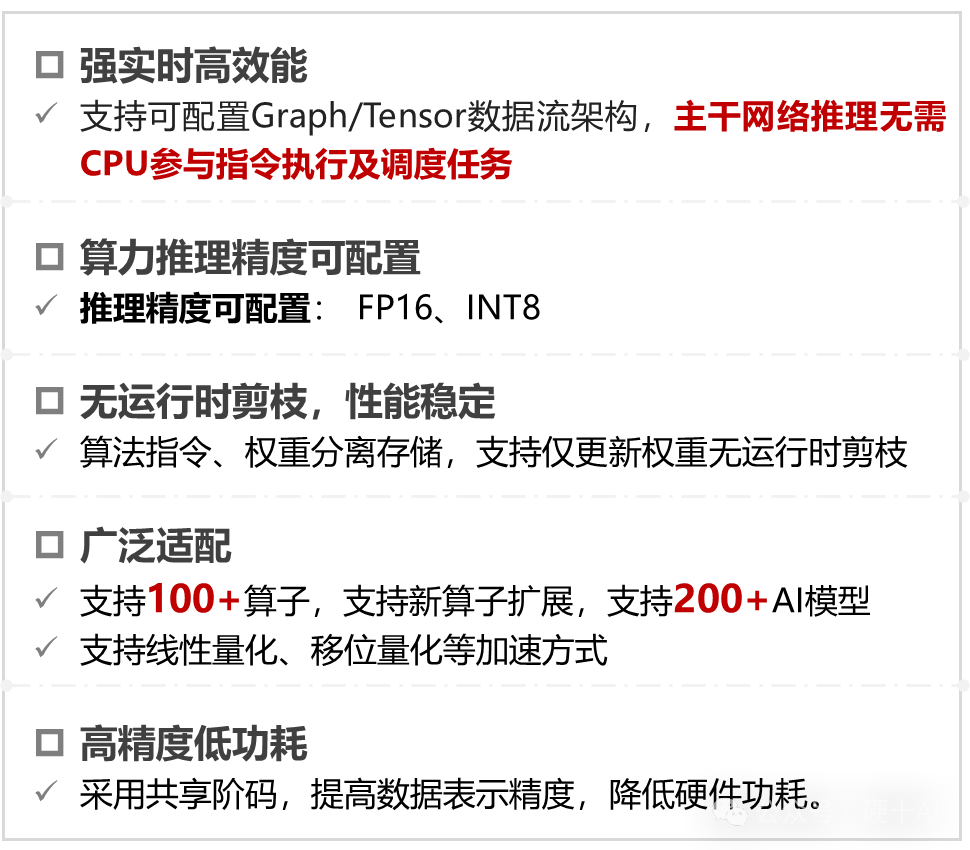

2. Chip Features Feature One:Neural network processor hardware can be flexibly configured

Feature One:Neural network processor hardware can be flexibly configured Feature Two:Supports diverse inference modesMode One:Multi-core single algorithm inference,achieving computing power aggregation, completing single network multi-core inference

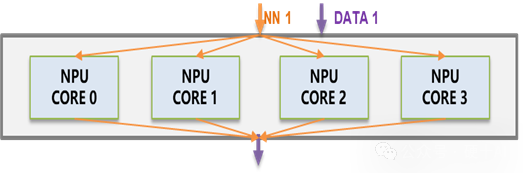

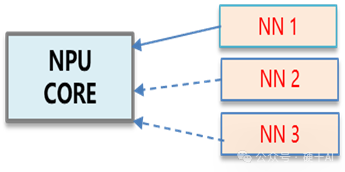

Feature Two:Supports diverse inference modesMode One:Multi-core single algorithm inference,achieving computing power aggregation, completing single network multi-core inference

- Applicable Scenarios:Strong real-time high-performance task requirements

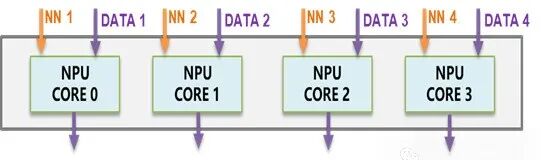

Mode Two:Multi-core multi-algorithm inference,multi-data source multi-network parallel inference

- Applicable Scenarios:Complex scenario multi-task concurrent processing requirements

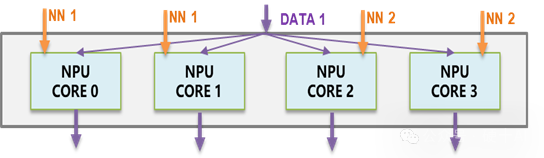

Mode Three:Large image partition multi-core inference,achievinglarge data multi-scale partition inference

- Applicable Scenarios::Ultra-large data chain processing requirements

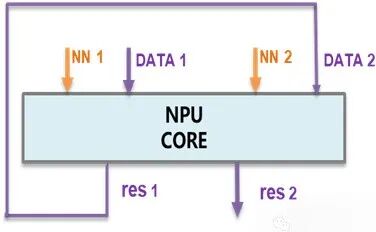

Mode Four:Dual algorithm continuous inference,dual algorithm one-click configuration for continuous inference

- Applicable Scenarios::Complex perception, recognition, detection integrated processing requirements

Mode Five:Runtime inference algorithm switching,both weights and algorithms can be switched

- Applicable Scenarios::High dynamic large deformation scenarios, supporting runtime network switching

Feature Three:Supports over 200 artificial intelligence algorithms, supports over 100 operators Feature Four:Fully domestic software ecosystem, simple and easy-to-use toolchain

Feature Four:Fully domestic software ecosystem, simple and easy-to-use toolchain For detailed information, refer to Hard Ten Classroom, scan the QR code to enterhttps://www.hw100k.com/coursedetail?id=271

For detailed information, refer to Hard Ten Classroom, scan the QR code to enterhttps://www.hw100k.com/coursedetail?id=271

Contact information for chip consultation and procurement