Today, we will introduce the two main characteristics of serial NAND Flash that prevent it from supporting XiP under the i.MXRT FlexSPI.

In the embedded world, when we mention XiP devices (memory that supports code execution in place), the first thing that comes to mind should be NOR Flash. For example, mid-range and low-end MCUs usually integrate small-capacity parallel NOR Flash (generally within 2MB) for storing applications; while high-performance MCUs often do not integrate Flash internally and require an external NOR Flash with a slightly larger capacity (most are serial NOR, generally above 8MB).

The NXP i.MXRT series belongs to high-performance MCUs that need external Flash. The i.MXRT can support four types of devices as boot devices: serial/parallel NOR and serial/parallel NAND, but the recommended models on the official reference design board EVK are all serial NOR Flash. The official recommendation does not include parallel NOR/NAND, which is understandable because parallel interface Flash occupies slightly more pins, which is not favorable for MCU projects with tight I/O resources. So why doesn’t the official recommend serial NAND as a boot device? This is mainly because serial NAND cannot support XiP under i.MXRT, which imposes some limitations on project software design. There are two reasons why NAND cannot XiP, which are related to the characteristics of NAND itself and the characteristics of the FlexSPI peripheral.

1. FlexSPI Support for NAND

We know that in the i.MXRT, the FlexSPI peripheral is responsible for implementing read and write access support for serial NOR/NAND Flash devices. I previously wrote an article titled “Understanding the Lookup Table in the i.MXRT Boot Header FDCB from Scratch,” which detailed how FlexSPI supports serial NOR Flash device XiP booting through the lookup table (mainly read access support).

In the lookup table design, AHB read access is not exclusive to NOR Flash devices; in other words, the FlexSPI peripheral itself does not care what type of device is connected; it simply works according to the command timing filled in by the user in the lookup table.

For four-wire QSPI NOR, only one command timing needs to be filled in the lookup table (there are many types of Read, but all can be implemented in one Sequence) to support AHB read. However, devices like HyperFlash, HyperRAM, and serial NAND require multiple command timings combined to complete a full read operation in the lookup table.

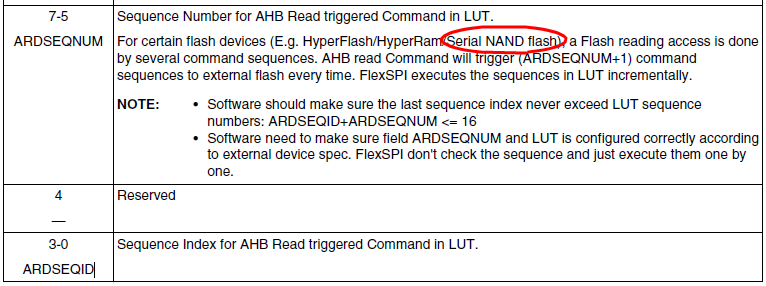

The FlexSPI peripheral supports combining multiple command timings in the lookup table to achieve AHB reads through the following two functional bits in the FlexSPI->FLSHxxCR2 register. The ARDSEQID bit indicates the starting position (index) of the read access timing in the lookup table, while the ARDSEQNUM bit indicates how many command timings the read access occupies (which also means that several command timings must be placed together in order).

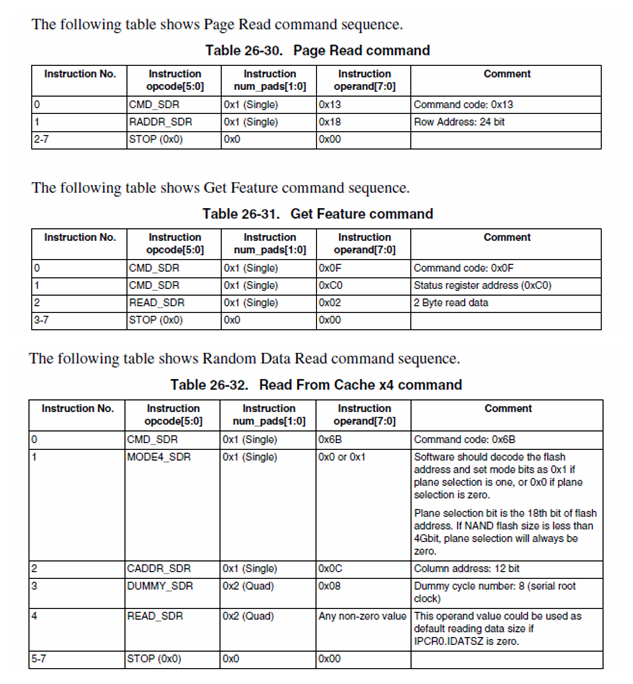

For example, the Micron MT29FxG01 serial NAND series requires the following three command timings (Page Read + Get Feature + Random Data Read) combined to complete the read operation. However, the ideal is very beautiful, but the reality is very skinny; even combining these three command timings cannot achieve NAND XiP under FlexSPI.

In practical applications, for NAND read access, the Page Read and Get Feature commands are manually sent first through IPCMD in the program code, and then the Random Data Read command in the lookup table is used to achieve AHB read of only one page size, which cannot achieve automatic AHB read of the entire NAND space (of course, if you think that AHB read of one page size is too chicken rib, you can directly use IPCMD to read page data).

Note: A detailed explanation about AHB read support for only one Page space in NAND. For example, if the NAND Page size is 2KB, the system only needs to allocate the AHB mapping space from 0x60000000 to 0x600007FF for NAND. Before each AHB read of this space, it is necessary to first send the Page Read and Get Feature commands through IPCMD to ensure that NAND is in the Ready state for Page data output, allowing FlexSPI to complete any AHB read access support within this Page. Once switching to a new Page access, the above process needs to be repeated, so all Page accesses of NAND can be completed within this 2KB mapping space.

2. The Two Characteristics of Serial NAND That Hinder XiP

What characteristics of serial NAND hinder XiP? Before revealing the answer, let’s first look at an old article titled “Introduction to Raw NAND” to gain a preliminary understanding of NAND Flash. Next, we will take the Micron MT29FxG01 model serial NAND as an example to introduce its two characteristics that hinder XiP:

2.1 Non-linear Storage Caused by Bad Blocks

Any NAND Flash cannot avoid the bad block (Bad Block) problem, which is an important characteristic that distinguishes NAND Flash from NOR Flash. NAND technology allows the existence of bad blocks, which reduces the production process requirements for NAND, hence the price per unit capacity of NAND is lower than that of NOR.

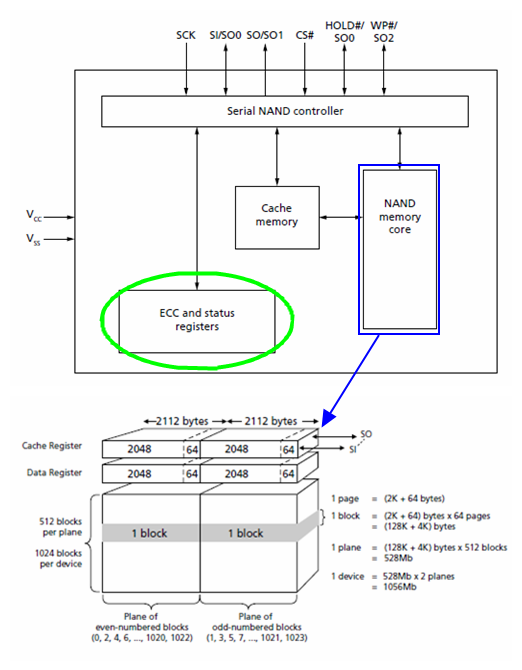

NAND is internally divided into Plane, Block, Page, and Byte by granularity from large to small (as shown in the figure below). Due to bad blocks, some Blocks cannot effectively store data, and these Blocks will be marked as bad. Therefore, from the perspective of the main device access, the data in NAND is not stored continuously by address; the addresses occupied by bad blocks are invalid addresses, which is known as non-linear storage, and non-linear storage devices clearly cannot be used as XiP devices.

For non-linear memory, it cannot guarantee that the application program is placed at the specified linked address (i.e., the corresponding offset address in Flash) during the write operation. When encountering a bad block during the write process, it will skip the bad block, and the invalid addresses occupied by those bad blocks are likely to be the actual linked addresses of the application program.

2.2 ECC Verification Leading to Page Read Wait

Now let’s assume an ideal situation where there are no bad blocks in NAND, and we can force NAND to be treated as a linear storage device. In this case, can it be used as a XiP device? Unfortunately, the FlexSPI peripheral still cannot directly support it (there are alternative methods to support it).

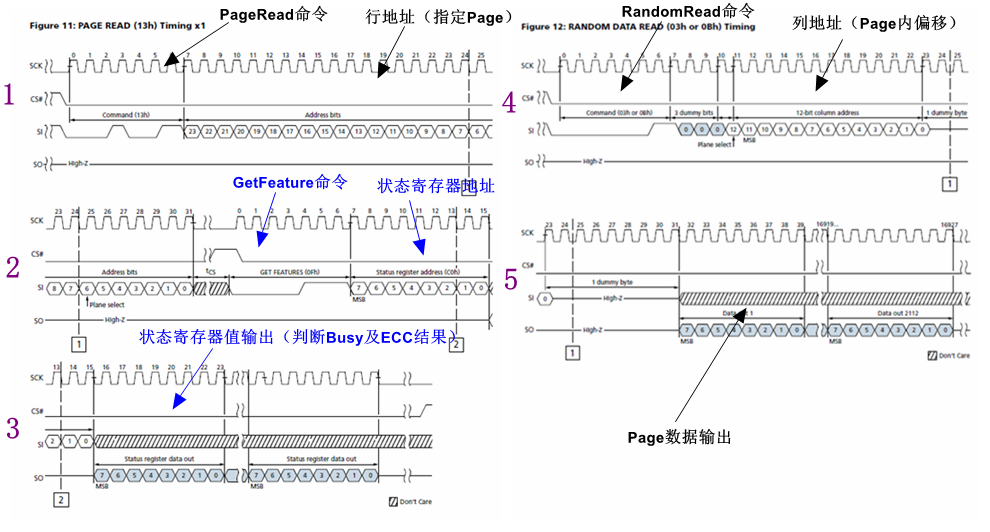

Let’s look at the complete read timing of serial NAND. 0x13 (Page Read) is the first command sent by FlexSPI to notify the NAND main device that it wants to access the Page. Then it sends the column address to specify the Page location to be read, at which point NAND will mark the Busy bit in the internal status register and enter the busy state.

During the busy state, NAND will copy all the specified Page data from the memory block to a temporary cache (Cache memory), perform ECC verification on this entire Page data, and upon completion, will mark the corresponding ECC in the status register and clear the Busy bit, then end the busy state and enter the data output preparation state.

Since it is unknown when NAND will end the busy state, FlexSPI needs to continuously send the 0x0F (Get Feature command) to read the value of the status register until the Busy bit in the status register is cleared before it can read the Page data. This logical judgment behavior cannot be automatically implemented in the lookup table (NOR read timing does not require logical judgment).

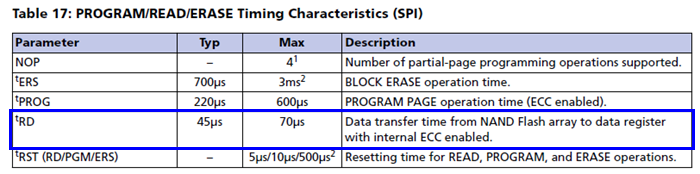

If we deliberately omit the step of reading the status register to avoid logical judgment behavior, can we directly fill in Dummy cycles in the lookup table instead? Theoretically, it is possible. Let’s calculate it. For example, with a typical NAND clock frequency of 50MHz, a Dummy Cycle takes 20ns, and the typical NAND Page Read wait time is 45us, which means 2250 Dummy Cycles. The lookup table has 16 sequences, each supporting 8 instructions, and if each instruction is set to DUMMY_SDR with a maximum parameter of 255, then 9 instructions can meet this wait time.

However, even if this approach barely achieves NAND Flash XiP, the actual execution efficiency of the code is still very low, as it involves long jumps across Pages (not to mention cache factors), requiring a wait of 45us, which is not a short time in the embedded world, and the system’s real-time performance cannot be guaranteed. What is the point?

Thus, the two main characteristics of serial NAND Flash lead to its inability to support XiP under the i.MXRT FlexSPI.

Source: PiZi Heng Embedded

Due to recent changes in the WeChat public platform push rules, many readers have reported not seeing updated articles in a timely manner. According to the latest rules, it is recommended to click “Recommended Reading, Share, Save,” etc., to become a frequent reader.

Recommended Reading:

-

Cash out 1 billion, a well-known domestic company is reported to have stopped paying wages!

-

All employees dismissed! Another electronic factory in Shenzhen announces shutdown and closure

-

Foxconn in Zhengzhou starts recruiting, with a monthly income of 18,600 yuan for screwing screws?

Please click 【View】 to give the editor a boost