1. Overview

Source: https://www.ti.com/lit/an/slva704/slva704.pdf

1. Electrical Characteristics

1.1 Open-Drain for Bidirectional Communication

Source: https://www.ti.com/lit/an/slva704/slva704.pdf

1.1.1 Open-Drain Pulling Low

Source: https://www.ti.com/lit/an/slva704/slva704.pdf

1.1.2 Open-Drain Releasing the Bus

Source: https://www.ti.com/lit/an/slva704/slva704.pdf

2. I2C Interface

2.1 Common Operations of I2C

-

Assuming a master wants to send data to a slave: -

The sending master sends a START condition and addresses the receiving slave -

The sending master sends data to the receiving slave -

The sending master ends the transmission by sending a STOP condition -

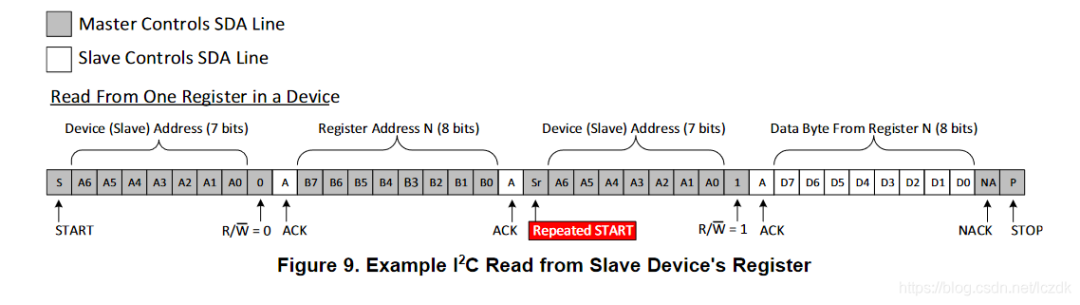

If the master wants to receive/read data from the slave: -

The receiving master sends a START condition and addresses the sending slave -

The receiving master sends the register address to be read from the sending slave -

The receiving master receives data from the sending slave -

The receiving master ends communication by sending a STOP condition

2.1.1 START and STOP Conditions

Source: https://www.ti.com/lit/an/slva704/slva704.pdf

2.1.2 Repeated START Condition

2.2 Data Validity and Byte Format

Source: https://www.ti.com/lit/an/slva704/slva704.pdf

2.3 Acknowledge (ACK) and Not Acknowledge (NACK)

-

The receiver cannot receive or send because it is performing some real-time functions and cannot communicate with the master. -

The receiver received unrecognized data or commands during transmission. -

The receiver cannot receive more data bytes during transmission (i.e., the buffer is full). -

The master, acting as the receiver, has completed data reading and sends a NACK to inform the slave.

Source: https://www.ti.com/lit/an/slva704/slva704.pdf

3. Bus Data

3.1 Writing to a Slave on the I2C Bus

Source: https://www.ti.com/lit/an/slva704/slva704.pdf

3.2 Reading from a Slave on the I2C Bus

Original

Source

At:

Copyright belongs to the original author

or

Platform

All

for learning

reference and academic research

If there is infringement, please contact

to delete ~ thank you

👆 Long press the image, scan the code to apply 👆