Source: Automotive ECU Design

In fact, communication between electronic devices is like communication between humans; both parties need to speak the same language. In electronic products, these languages are called communication protocols. First, we will start with some basic concepts and then explain the working principle of SPI in detail.

01

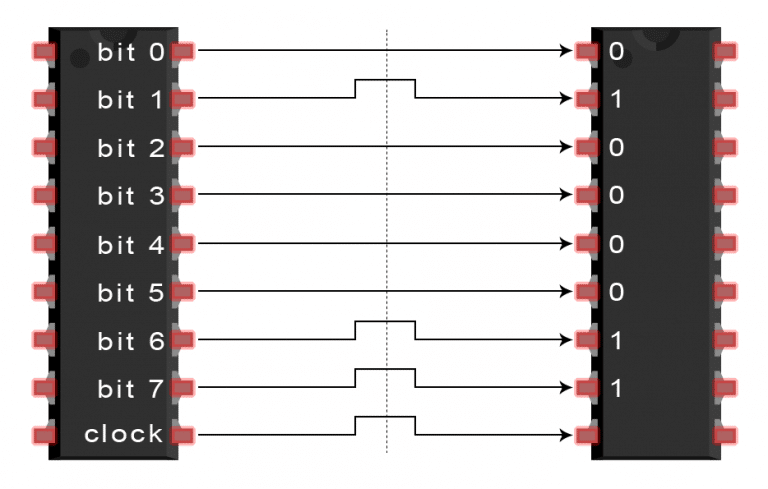

Serial vs Parallel

Electronic devices communicate by sending data bits back and forth. Bits are binary and can only be 1 or 0. Through rapid voltage changes, bits are transmitted from one device to another. In systems operating at 5V, “0” is communicated through a short pulse at 0V, while “1” is communicated through a short pulse at 5V.

02

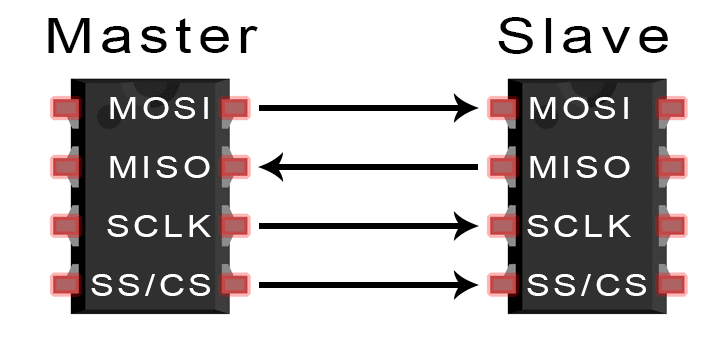

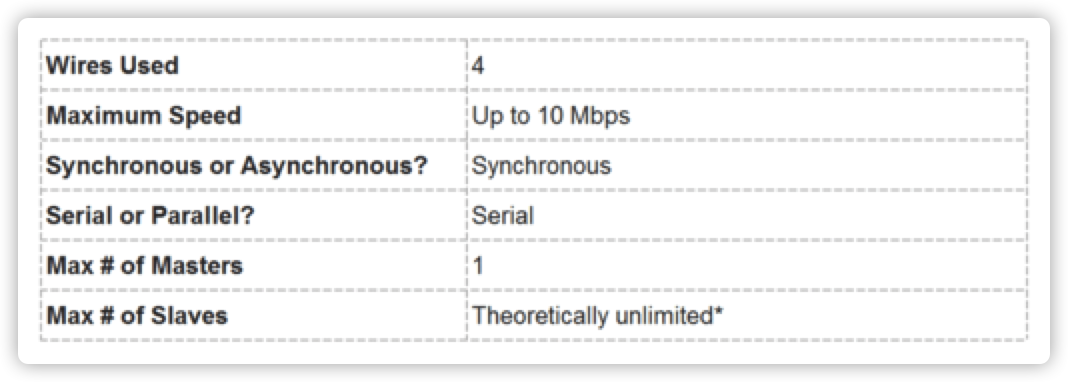

SPI Bus

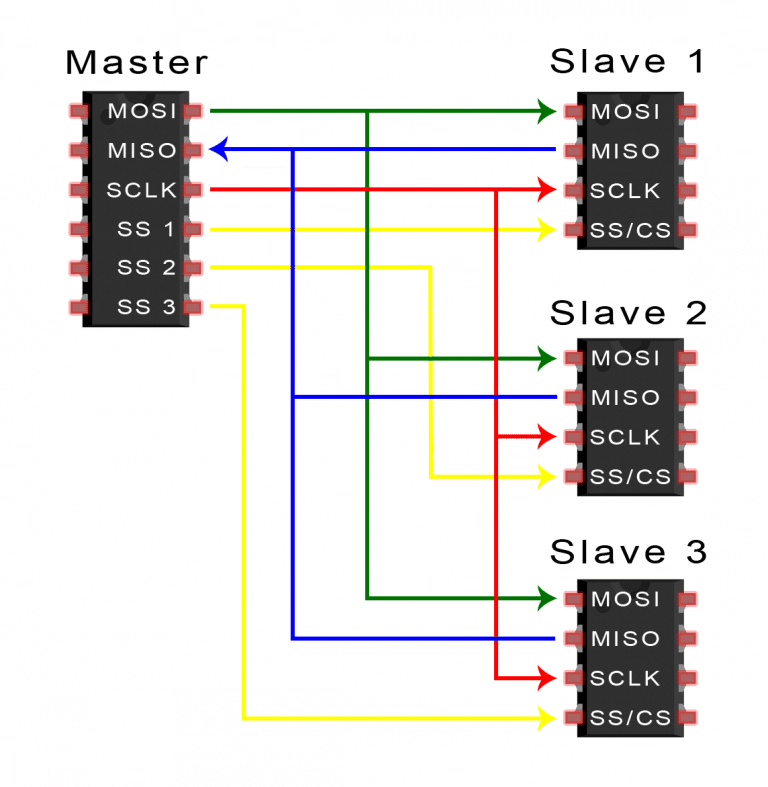

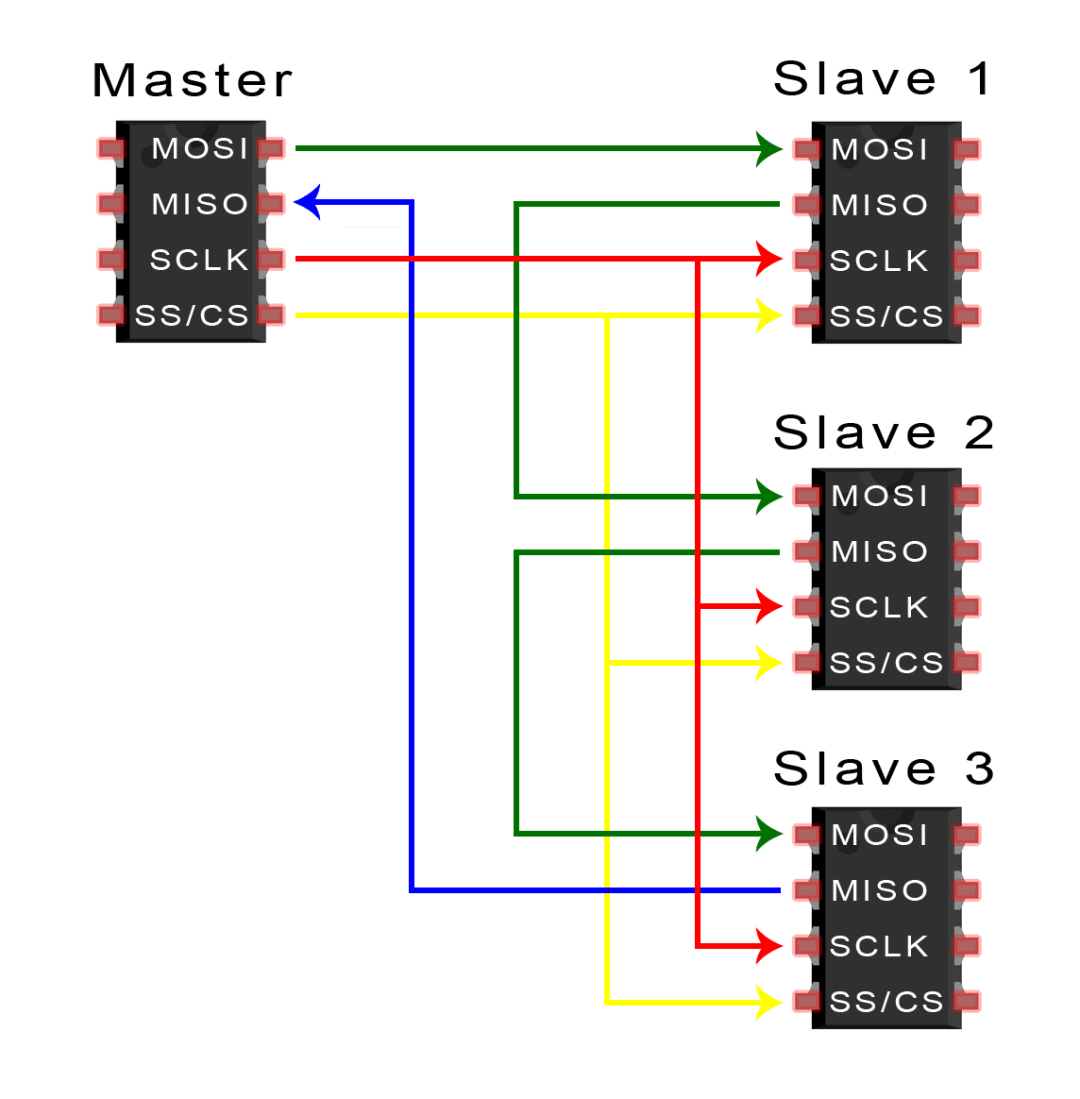

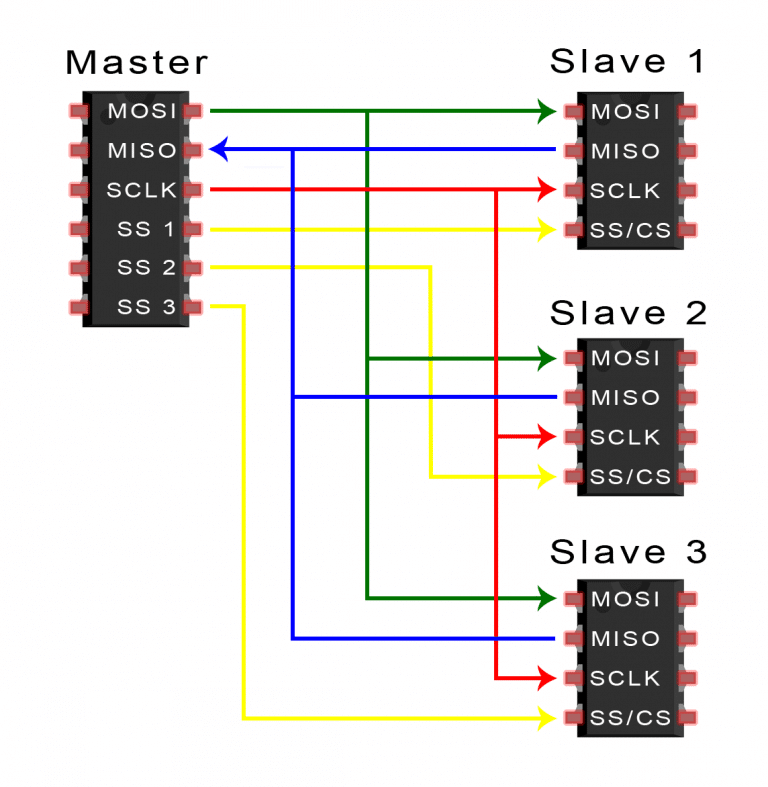

In practice, the number of slaves is limited by the system’s load capacitance, which reduces the master’s ability to switch accurately between voltage levels.

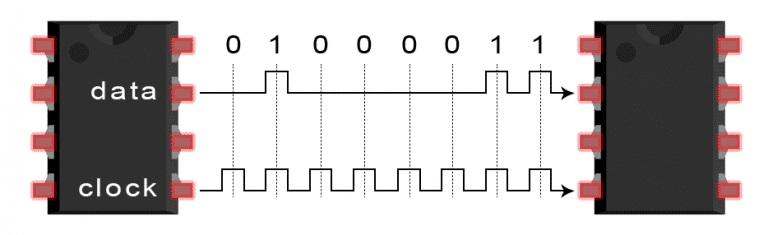

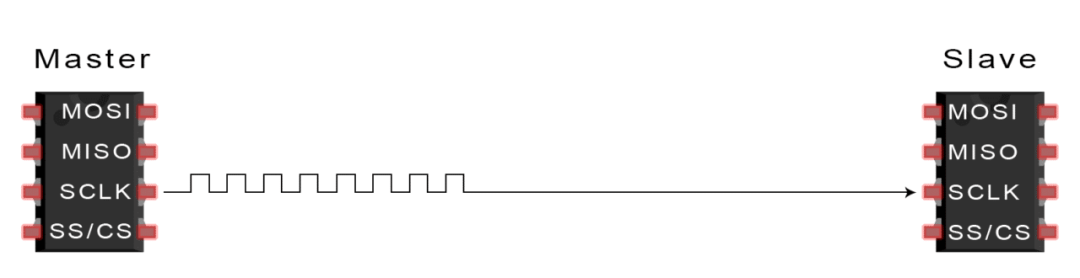

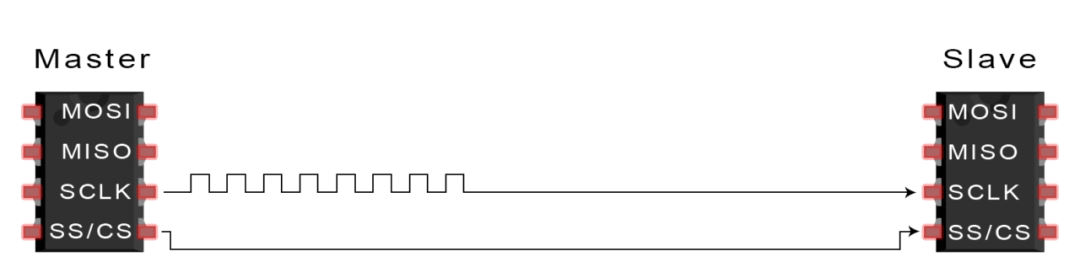

Clock Signal

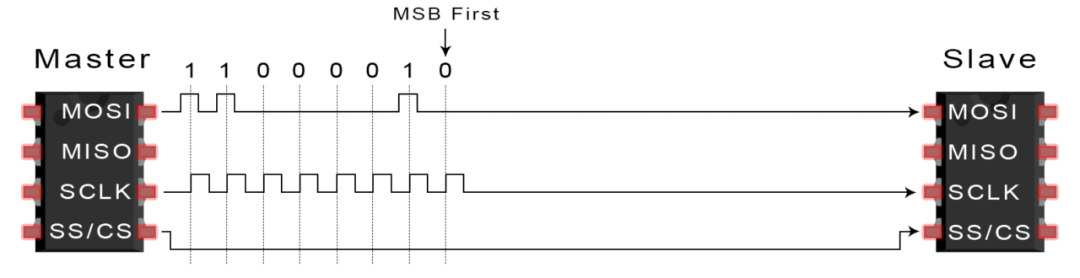

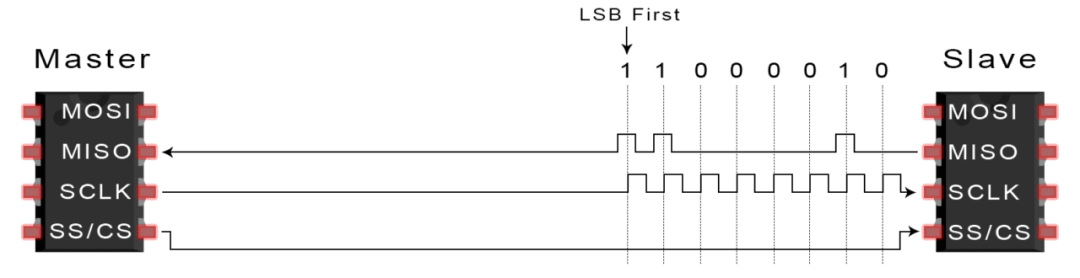

Any communication protocol that shares a clock signal among devices is called synchronous. SPI is a synchronous communication protocol, while some asynchronous communications do not use a clock signal. For example, in UART communication, both sides are set to a pre-configured baud rate, which determines the speed and timing of data transmission.

Chip Select Signal

The master enables communication by pulling the slave’s CS/SS low. In idle/non-transmission state, the chip select line remains high. There can be multiple CS/SS pins on the master, allowing it to communicate with multiple different slaves.

MOSI and MISO

There are some advantages and disadvantages to using SPI, and if choosing between different communication protocols, careful consideration should be given based on project requirements.

Advantages

Disadvantages

SPI uses four lines (while I2C and UART use two), lacks confirmation of successful signal reception (I2C has this feature), and does not have any form of error checking (such as parity bits in UART).

03

UART Communication

When the receiving UART detects the start bit, it reads the bits in the data frame at a specific baud rate. Baud rate is a measure of the speed of data transmission, expressed in bits per second (bps). The two UARTs must operate at approximately the same baud rate, with the baud rate between the sending and receiving UARTs differing by no more than about 10%.

After the sending UART obtains the parallel data from the data bus, it adds a start bit, a parity bit, and a stop bit to form a data packet, which is then serially output bit by bit from the Tx pin. The receiving UART reads the data packet bit by bit on its Rx pin.

UART data consists of 1 start bit, 5 to 9 data bits (depending on UART), an optional parity bit, and 1 or 2 stop bits:

Start Bit

Data Frame

The data frame contains the actual data being transmitted. If a parity bit is used, it can be 5 bits, up to 8 bits. If no parity bit is used, the length of the data frame can be 9 bits.

Parity Bit

The parity bit is a way for the receiving UART to determine if any data changes occurred during transmission. After the receiving UART reads the data frame, it counts the number of bits that are 1 and checks whether the total is even or odd, and whether it matches the data.

Stop Bit

To signal the end of the data packet, the sending UART drives the data transmission line from low voltage to high voltage for at least two bit times.

1. The sending UART receives parallel data from the data bus:

2. The sending UART adds the start bit, parity bit, and stop bit to the data frame:

3. The entire data packet is serially sent from the sending UART to the receiving UART. The receiving UART samples the data line at the pre-configured baud rate:

4. The receiving UART discards the start bit, parity bit, and stop bit from the data frame:

5. The receiving UART converts the serial data back to parallel data and transmits it to the data bus of the receiving end:

Advantages

-

Only two wires are used.

-

No clock signal is required.

-

Parity bit allows for error checking.

-

As long as both sides set up the structure of the data packet.

-

Well-documented and widely used method.

Disadvantages

-

Maximum size of data frame is 9 bits.

-

Does not support multiple slave systems or multiple master systems.

-

The baud rate of each UART must be within 10% of each other.

04

I2C Bus

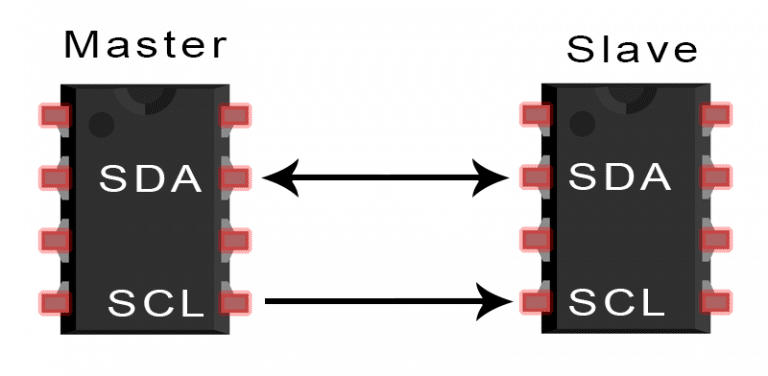

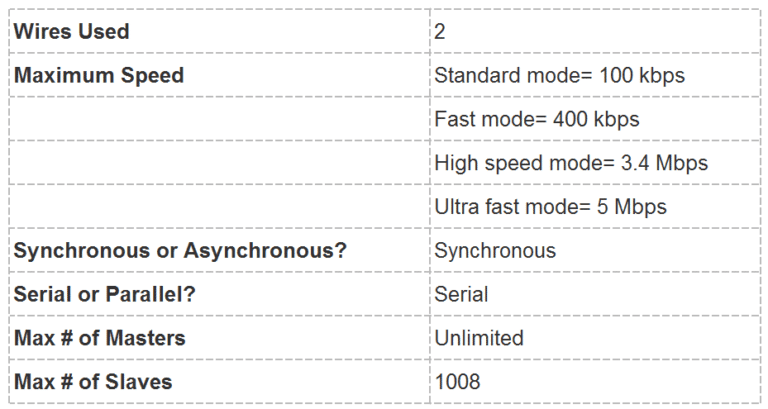

I2C bus is a simple, bidirectional, two-wire synchronous serial bus developed by Philips. It requires only two wires to transmit information. It combines the advantages of SPI and UART, allowing multiple slaves to connect to a single master (like SPI), and also enabling multiple masters to control one or more slaves. This is particularly useful when multiple microcontrollers want to log data to a single storage card or display text on a single LCD.

SDA (Serial Data) – Data line.

SCL (Serial Clock) – Clock line.

I2C data transmission occurs in the form of multiple messages, each containing the binary address frame of the slave, one or more data frames, along with start conditions, stop conditions, read/write bit, and ACK/NACK bit between data frames:

Start Condition: When SCL is high, SDA switches from high to low.

Stop Condition: When SCL is high, SDA switches from low to high.

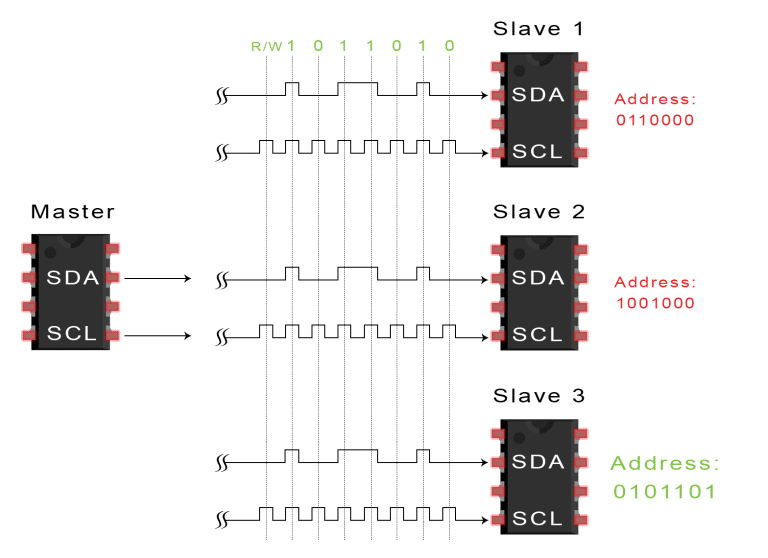

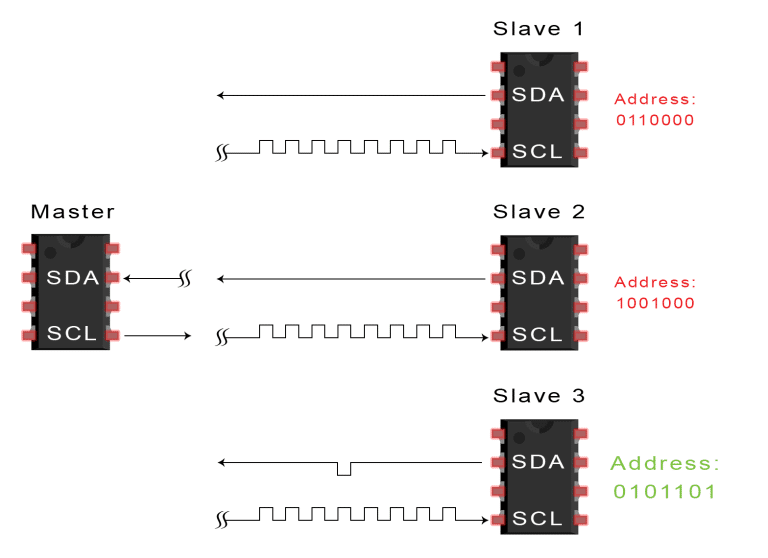

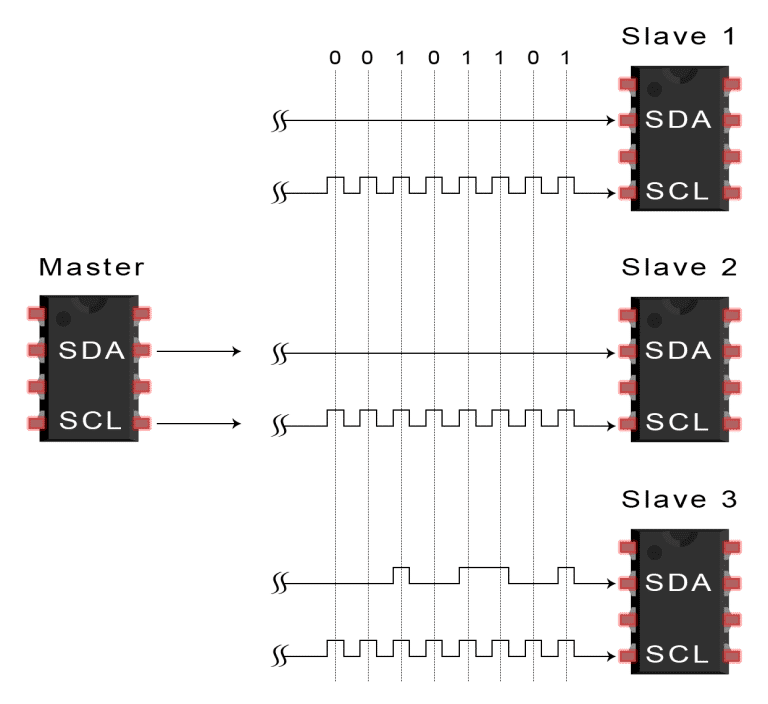

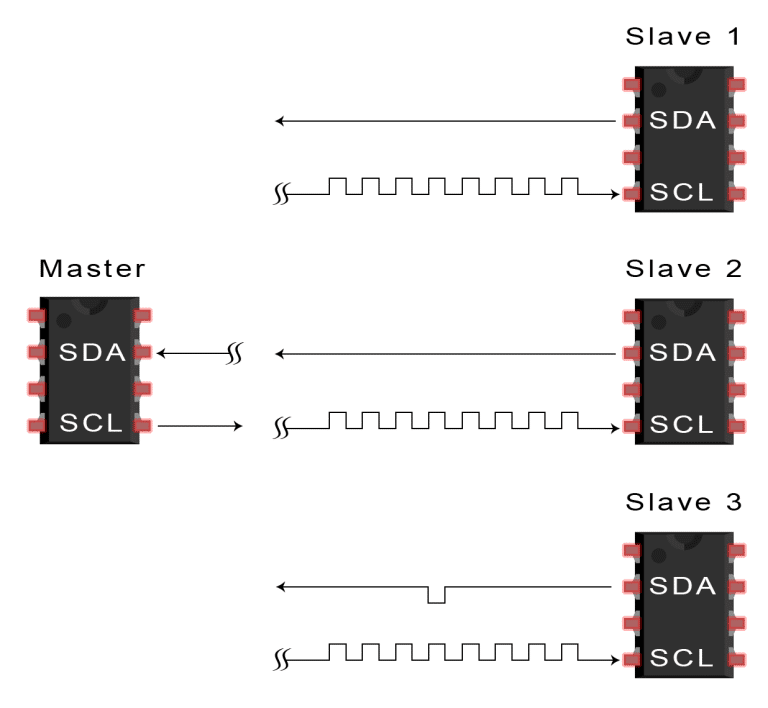

Addressing

The master sends the address of the slave it wants to communicate with to each slave, and each slave compares it with its own address. If the addresses match, it sends a low-level ACK bit back to the master. If they do not match, no action is taken, and the SDA line remains high.

Read/Write Bit

The end of the address frame contains a read/write bit. If the master is sending data to the slave, it is low. If the master is requesting data from the slave, it is high.

Data Frame

3. Each slave compares the address sent by the master with its own address. If the addresses match, the slave returns an ACK bit by pulling the SDA line low. If the master’s address does not match the slave’s address, the slave pulls the SDA line high.

4. The master sends or receives data frames:

5. After each data frame is transmitted, the receiving device returns another ACK bit to the sender to confirm that the frame has been successfully received:

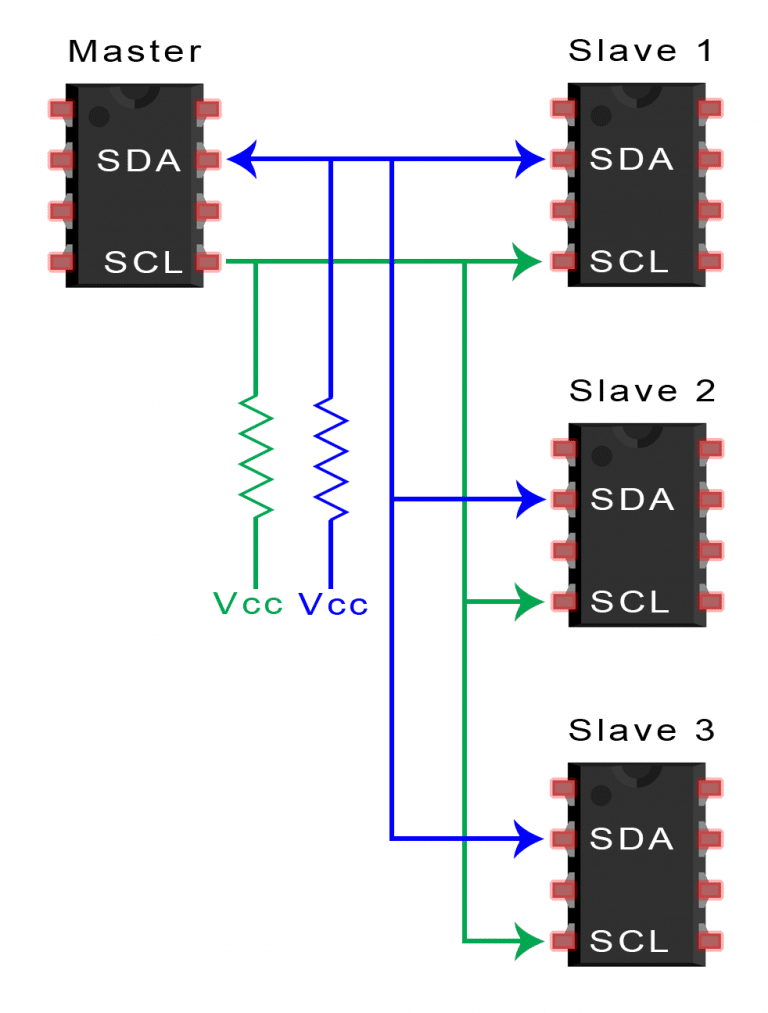

Single Master vs Multiple Slaves

Multiple Masters vs Multiple Slaves

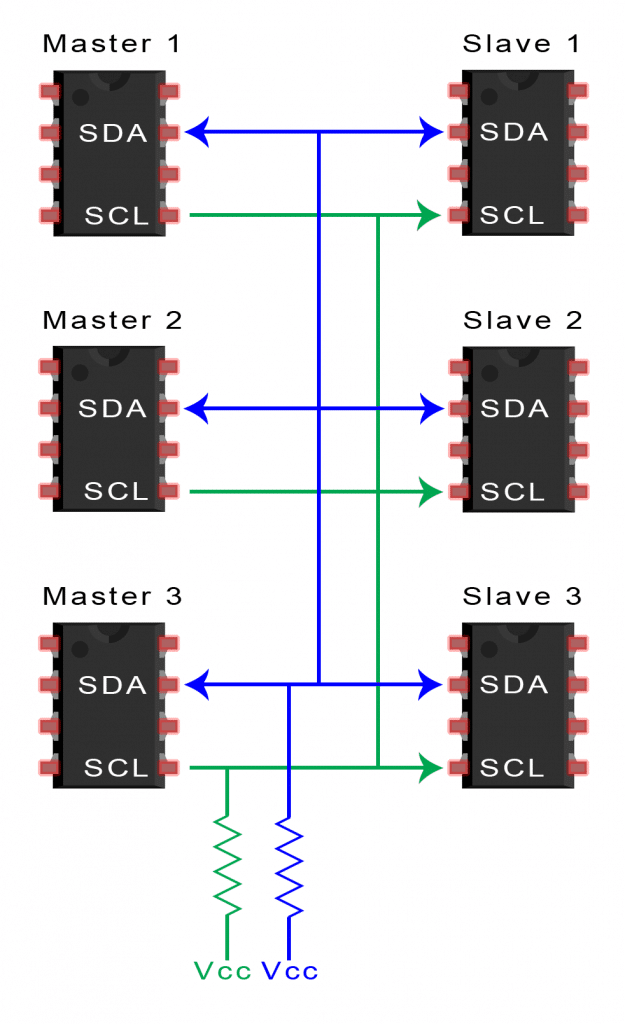

I2C supports multiple masters connected to multiple slaves at the same time. However, issues can arise when two masters try to send or receive data simultaneously via the SDA line. Therefore, each master needs to check whether the SDA line is low or high before sending a message. If the SDA line is low, it means another master is controlling the bus. If the SDA line is high, it is safe to send data. When connecting multiple masters to multiple slaves, use a pull-up resistor of 4.7K ohms to connect the SDA and SCL lines to Vcc:

Advantages

-

Only two wires are used.

-

Supports multiple masters and multiple slaves.

-

ACK/NACK bits are used to confirm that each frame has been successfully transmitted.

-

Hardware is simpler than UART.

-

Well-known and widely used protocol.

Disadvantages

-

Data transmission rate is slower than SPI.

-

Data frame size is limited to 8 bits.

Want to switch to autonomous driving? This article tells you how to start.

Safety challenges in vehicle diagnostic systems.

Understanding ASPICE.

Detailed explanation of automotive Bootloader design.

Research on the safety of Tesla Autopilot system | includes dbc download.

Detailed explanation of functional safety concept phase.

In-depth analysis of the high-voltage system in Volkswagen ID.4.

Battery management system of Tesla Model 3.