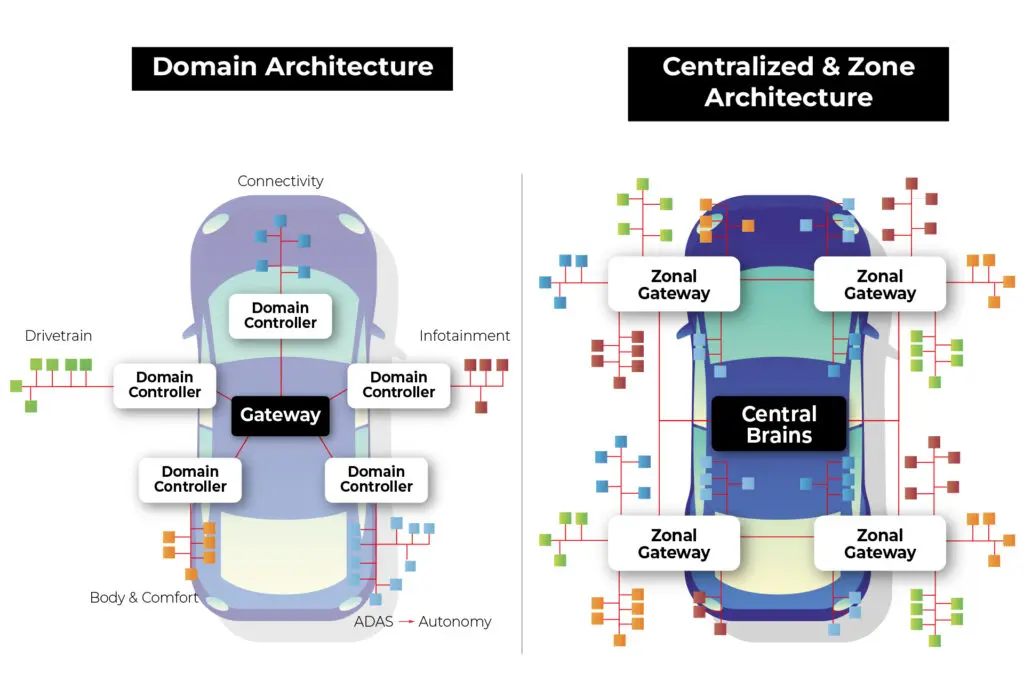

The selection of chips under the integrated architecture (central + regional architecture) has shifted from a single performance competition to a systematic design. Engineers need to break free from traditional thinking, starting from the overall vehicle architecture, balancing the centralization of computing power with the distributed needs of regional control.With the advent of the smart car era, the automotive electronic and electrical architecture is transitioning from traditional distributed systems to a central + regional architecture, achieving the goals of centralized computing power, standardized interfaces, and software-defined vehicles (SDV).Chip selection is no longer limited to a single performance metric but needs to be considered from a systematic design perspective, comprehensively evaluating the high-performance SoC of the central computing platform and the functional safety MCU requirements of regional controllers.

The selection of chips under the integrated architecture (central + regional architecture) has shifted from a single performance competition to a systematic design. Engineers need to break free from traditional thinking, starting from the overall vehicle architecture, balancing the centralization of computing power with the distributed needs of regional control.With the advent of the smart car era, the automotive electronic and electrical architecture is transitioning from traditional distributed systems to a central + regional architecture, achieving the goals of centralized computing power, standardized interfaces, and software-defined vehicles (SDV).Chip selection is no longer limited to a single performance metric but needs to be considered from a systematic design perspective, comprehensively evaluating the high-performance SoC of the central computing platform and the functional safety MCU requirements of regional controllers.

This article will delve into the driving forces behind architectural evolution, the computing power requirements of central computing platforms, the functional integration and safety features of regional controllers, as well as technological trends and challenges, providing a systematic framework and practical reference for chip selection.

01Architectural Evolution:

The Transition from Distributed to Central + Regional

The evolution of automotive electronic and electrical architecture is essentially a redistribution of computing power, data, and functions.

In traditional distributed architectures, dozens of electronic control units (ECUs) operate independently, with functions fixed and tightly coupled with hardware and software, leading to poor system scalability and low development efficiency.However, with the rapid proliferation of intelligent driving, smart cockpits, and vehicle networking functions, single-point computing power is no longer sufficient to meet the demands of multimodal data processing and high-level computing.For example, autonomous driving requires real-time fusion of camera, radar, and LiDAR data, running complex AI inference models, while the decentralized computing layout of traditional architectures is clearly inadequate.

The integrated architecture (central + regional) has emerged, through a layered design of “central computing platform + regional controller”, concentrating high-computing tasks in the central brain (such as AI inference and multi-screen interaction), while regional controllers are responsible for the nearby access and local control of sensors and actuators.

This collaborative model of “computing power elevation and drive decentralization” not only enhances computing efficiency but also reduces overall vehicle costs through interface standardization and harness optimization.For example, in high-end models, the central computing platform can be equipped with NVIDIA Thor (with computing power exceeding 1000 TOPS) or Qualcomm SA8295P chips, paired with 3-4 regional controllers (such as front cabin, left and right sides, rear cabin), forming an efficient system of “brain + nerve center”.In contrast, mid-range and low-end models may adopt a “cockpit-integrated” single-chip solution combined with 2-3 regional controllers to achieve a balance between performance and cost.

The driving forces behind this evolution include the explosive demand for computing power, the trend of software definition, and the optimization of cost and efficiency.

With the development of intelligent driving and cockpit entertainment functions, processing massive amounts of data has become crucial, such as meeting the demands of multiple 4K camera inputs and edge-side large model inference, which directly drives the need for higher computing power.

The trend of software-defined vehicles (SDV) requires hardware platforms not only to support firmware over-the-air updates (FOTA) but also to enable flexible expansion of functions to adapt to ever-changing technologies and user needs.

In terms of cost and efficiency, reducing the number of electronic control units (ECUs) and the length of harnesses can lower costs by 30%-50% and enhance the integration of the entire vehicle, making vehicle design simpler and more efficient. Therefore, when selecting hardware, it is necessary to clarify the computing power allocation strategy based on the positioning of the vehicle model.For example, for high-end models pursuing extreme performance, it is essential to choose system-on-chips (SoCs) that support heterogeneous computing (including CPU, GPU, and NPU); while for entry-level models that focus more on power consumption and cost control, it is preferable to adopt more integrated single-chip solutions to achieve the best cost-effectiveness and performance balance.

02Considerations for Chip Selection:Layered Computing Power and Scene Adaptation

1. Central Computing Platform

The central computing platform serves as the core of computing power for the entire vehicle, undertaking important responsibilities for processing high-level tasks such as intelligent driving, cockpit interaction, and vehicle networking. Its chip selection must comprehensively consider performance, power consumption, communication capabilities, and software ecosystem compatibility.

Specific requirements include multimodal processing capabilities, such as supporting display outputs with resolutions up to 4K@60fps, multiple camera inputs, and AI inference tasks like voice recognition and intent inference; in terms of high-bandwidth communication, it requires equipping with gigabit Ethernet (supporting time-sensitive networking TSN), PCIe interfaces for connecting external accelerators, and low-latency audio buses (such as A2B) to meet efficient data transmission needs; regarding ecosystem support, the selected chip needs to be compatible with mainstream operating systems (such as QNX, Linux), provide open application programming interfaces (APIs), and have FOTA capabilities to ensure system scalability and future upgrade potential.

By comprehensively evaluating these key factors, it can ensure that the central computing platform meets the demands of current complex applications while providing a solid foundation for future functional expansion and technological advancement.

“Central brain chip selection” covers three major areas: intelligent driving chips, smart cockpit chips, and high-performance chips, categorized by year (2021-2027) and performance (low, mid, high-end):

Intelligent driving chips: with TOPS as the performance metric. Low-end includes the 2021 TDA4 (30 TOPS); mid-range includes the 2022 A1000 (100 TOPS), 2023 Orin-N, etc.; high-end includes the 2022 Ascend 610 (200 TOPS), 2021 Orin-X (500 TOPS), with Ascend 620/Pro, J6P expected to launch in 2025.

Smart cockpit chips: with DMIPS as the metric. Mid-range includes the 2021 SA8155, 2022 Chipone SE1000 series; high-end includes the 2021 SA8295 (300K DMIPS), 2024 SA8255, etc., with the 2023 MT2715 series expected to launch.

High-performance chips: mid-range SA8775 expected to launch in 2023, 2024 SM8650; high-end includes the Thor series (ThorS 500 TOPS, ThorU 700 TOPS, ThorX 1000 TOPS), with SA8397 and ZTE A1 expected to launch in 2026, meeting higher computing power demands.

Chip selection must closely align with scene requirements to avoid computing power redundancy. For instance, cloud gaming scenarios require CPU computing power of 16K DMIPS and GPU floating-point computing capability of 60 GFLOPS, while basic entertainment functions only require 2K DMIPS. Overly pursuing high computing power may lead to cost waste and excessive power consumption.

Therefore, engineers should develop differentiated strategies based on vehicle model positioning (such as entry-level, mid-range, high-end) and functional configurations (such as whether to support L3+ intelligent driving). At the same time, software ecosystem compatibility is crucial; Qualcomm and NVIDIA hold advantages with mature development toolchains and third-party support, while domestic chips need to further improve their IDE and API ecosystems.

2. Regional Controller Chip Selection: Emphasizing I/O Drive and Functional Safety

Regional controllers are responsible for localized control and functional integration, with chip selection focusing on I/O resources, safety, and real-time performance. For example, a rear cabin regional controller needs to integrate functions such as electric tailgate, seat heating/ventilation, and suspension control, imposing the following requirements on the chip:I/O Density: supporting multiple CAN (12 channels), LIN (8 channels), GPIO (50+ channels), and high/low side drive capabilities;Storage and Safety: under SOA architecture, Flash requirements increase to 14.34KB (non-SOA is 8.8KB), RAM increases from 0.533KB to 0.963KB; needs to integrate HSM modules and A/B partition flashing capabilities;Computing Power and Functional Safety: basic scenarios use Cortex-M33 (120MHz, ASIL-B), while high-end scenarios require dual-lockstep Cortex-M7 (300MHz, ASIL-D).

“Regional controller chip selection” includes parameters and characteristics of multiple regional controller chips, divided into several parts:

Infineon TC389: equipped with 4 TriCore™ cores, running at 300MHz (also includes 2 check cores), providing 2700 DMIPS, using LFBGA-516 packaging, with 10MB Flash, 1568KB SRAM, 1 Gbit Ethernet, 12x CAN FD, and eVita full HSM.

Renesas RH850U2A8~16: 2*400MHz, reaching 3000 DMIPS, LFBGA-373~516 packaging, 8~16MB Flash, 1792 KB SRAM, 1 Gbit Ethernet, 16x CAN FD, and eVita full HSM.

Chipone: FC4150F2M (in mass production): Cortex M4 core, up to 150MHz, 2MB P-Flash + 256K D-Flash, 256K SRAM. FC7300F8MDT (in mass production): Cortex M7 core, 2*LS+1, 300MHz, 8MB P-Flash (supports A/B swap), 256K D-Flash, Flash overlay, up to 1216K SRAM, packaged in 176LQFP-EP or BGA320.

Yuntong: YTM32B1M: M33 core, 120MHz, 64-144LQFP packaging, 256K-1MB Flash, compliant with AEC-Q100 G1, ASIL-B. YTM32B1H: M7 core, 300MHz, with 2 Lockstep, 257/289BGA packaging, 2M-8MB Flash, compliant with AEC-Q100 G1, ASIL-D.

Zhixin: Z20K14x series: based on ARM CORTEX M4F, main frequency 160MHz, 2M P Flash + 128K D Flash, 8-channel CANFD, 6-channel UART/LIN, meeting ASIL-B. Z20K3xx series (under development): based on high-end ARM core, main frequency 320MHz, providing dual-core to six-core options, meeting ASIL-B/D.

Huawei Chitu SoC: aimed at VDC and next-generation regional controllers, expected to enter mass production in Q1 2025, the world’s first vehicle control-specific 4-in-1 SoC (MCU + MPU + Switch + PHY), integrating 6R52 core + 4 ARM A55 cores, powerful computing capabilities, supporting CAN/LIN/Ethernet (up to 50Gbps switching capability), fully supporting TSN technology, with an integrated NP network processor to address communication load issues.

Currently, mainstream MCUs for regional controllers are Infineon’s Aurix series and Renesas’ RH850 series, capable of achieving S2S service proxy (computing power), A/B partition flashing (storage), and rich IO resources (driving) requirements.

Domestic MCUs such as Chipone’s FC7300 and Huawei’s Chitu SoC have strong performance. The Huawei Chitu SoC series is planned for mass production in Q1 2025, considering replacing the S32G3 VAVE solution; if the next-generation architecture involves nearby access and processing of cameras, this series can also be considered.

With the popularity of high-pressure actuators such as steer-by-wire and active suspension, regional controllers need to support 48V power input and high-voltage drive interfaces, putting traditional 12V MCUs under upgrade pressure. For example, Infineon’s AURIX TC4x series has optimized power management and driving capabilities for 48V systems, becoming a future trend. Domestic chips need to accelerate their layout in the high-voltage MCU field to seize market opportunities.

03

Conclusion

The chip selection under the integrated architecture (central + regional architecture) has shifted from a single performance competition to systematic design. Engineers need to break free from traditional thinking, starting from the overall vehicle architecture, balancing the centralization of computing power with the distributed needs of regional control.

The central computing platform pursues high computing power and ecosystem compatibility, while regional controllers emphasize I/O density and functional safety. The two achieve efficient division of labor through dynamic computing power collaboration, with data security (hardware encryption), functional safety (ASIL-D), and cost efficiency becoming key constraints in selection.

The Ministry of Industry and Information Technology’s “Guidelines for the Construction of National Automotive Chip Standard System” clearly states that by 2025, more than 30 key automotive chip standards will be formulated, establishing key product and application technical specifications for control, computing, storage, power, and communication chips, forming matching test methods for vehicles and key systems to meet the basic needs for the safe and reliable application and pilot demonstration of automotive chip products. This will promote the large-scale development of domestic automotive chips, ushering in an accelerated development period for domestic automotive chips.

Source | Zhizhi Smart Chip