In increasingly complex wireless communication systems, achieving high performance and low power consumption in digital signal processing (DSP) under process-constrained environments has become a significant challenge for chip architects. At the fifth RISC-V China Summit’s Frontier Innovation Technology Sub-Forum, Li Gaoshan, a senior expert from ChipRise Technology and a top talent from China Mobile, delivered a report titled “The Latest RISC-V Instruction Set in the DSP Field and Innovative Applications of DSA in Wireless Domains,” deeply analyzing the evolution of RISC-V in the DSP field and the breakthrough value of Domain-Specific Architecture (DSA) in communication applications.

1. Background: The Conflict Between DSP and Communication Chips

Li Gaoshan pointed out that with the advancement of 5G/6G communication standards, the computational intensity of wireless signal processing has significantly increased, while the process technology remains constrained by external limitations, stuck at mid-to-low-end nodes. Faced with the “dual squeeze” of standardized protocols and homogenized processes, communication chip manufacturers find it challenging to achieve effective differentiation under traditional architectures. In this context, the RISC-V platform, with stronger instruction-level customization capabilities and a more open architecture, provides an ideal soil for innovation in communication DSP.

2. RISC-V DSP-W: An Instruction Set Extension Born for Wireless

He stated that ChipRise Technology, in collaboration with ChipRise Technology, has jointly promoted a new generation DSP instruction set named RISC-dsp-W, which is deeply customized based on the RISC-V architecture and is one of the standard candidates for the DSP Task Group (TG) being prepared by the RISC-V Foundation RVV SIG. Its core advantages are reflected in the following points:

1. Enhanced Fixed-Point Arithmetic Support

Introducing mechanisms such as saturation and rounding/clipping;

Providing a wider dynamic range and higher precision to adapt to complex signal characteristics.

2. Native Complex Arithmetic Capability

Supporting mainstream complex data types like SC16;

Built-in basic operation instructions for complex addition, multiplication, and accumulation, enhancing FFT and filtering efficiency.

3. Data Type Conversion Optimization

Achieving fast conversions between integers, decimals, and complex numbers; providing a strongly consistent hardware acceleration interface (such as the SFT instruction set family).

4. Fast Non-Linear Function Support

Built-in piecewise function implementations of commonly used AI activation functions such as exponentials, logarithms, tanh, and sigmoid;

Adapting to the efficient computing needs in AI/DSP hybrid scenarios.

Data presented by Li Gaoshan indicates that in wireless signal processing, RISC-dsp-W can achieve a performance improvement of 4 to 5 times over the RVV architecture under the same hardware resources, especially excelling in core DSP operators such as dot products and convolutions.

3. DSA Architecture: RISC-V Practice Born for Customization

He pointed out that DSA (Domain Specific Architecture) aims to design the optimal architectural solutions for specific domains. The modular and open characteristics of RISC-V naturally align with the needs of DSA, providing a precise breakthrough path for the wireless communication field.

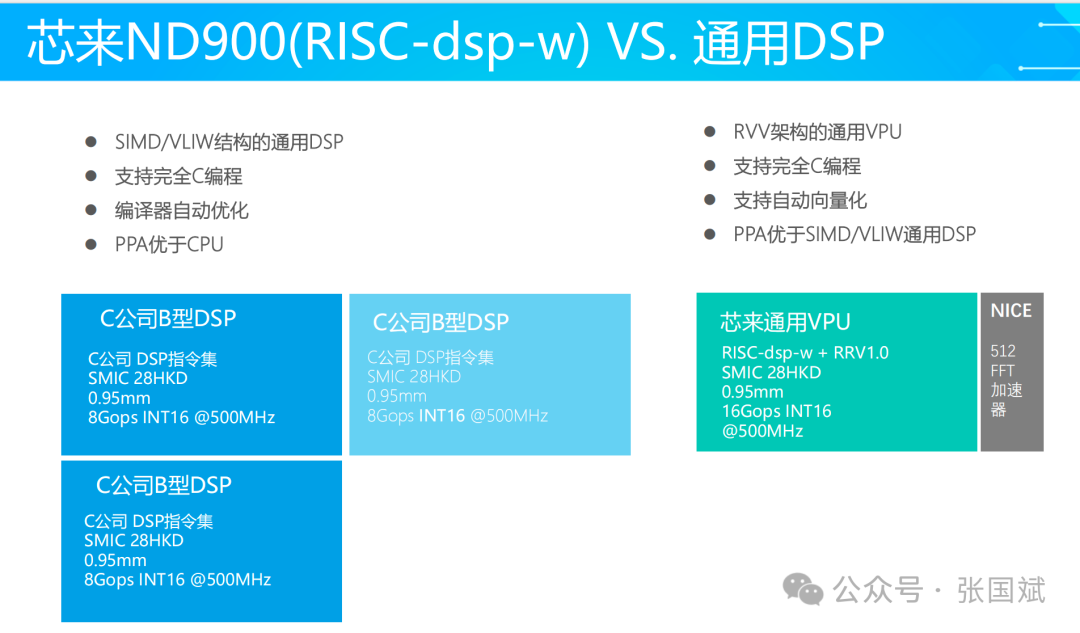

He pointed out the current issues with baseband chip architecture: fixed standard protocols that cannot differentiate; general DSPs (such as SIMD/VLIW) have low efficiency and high power consumption; ACCE-type hardware solutions lack flexibility and can only compete at lower levels. The breakthrough point of DSA is to build customized accelerators for wireless signals based on RISC-dsp-W—comparable in area and power consumption to ACCE solutions, but with instruction-level flexibility; it can also optimize algorithms and operators based on actual scenarios, making it more suitable for non-standard requirements.

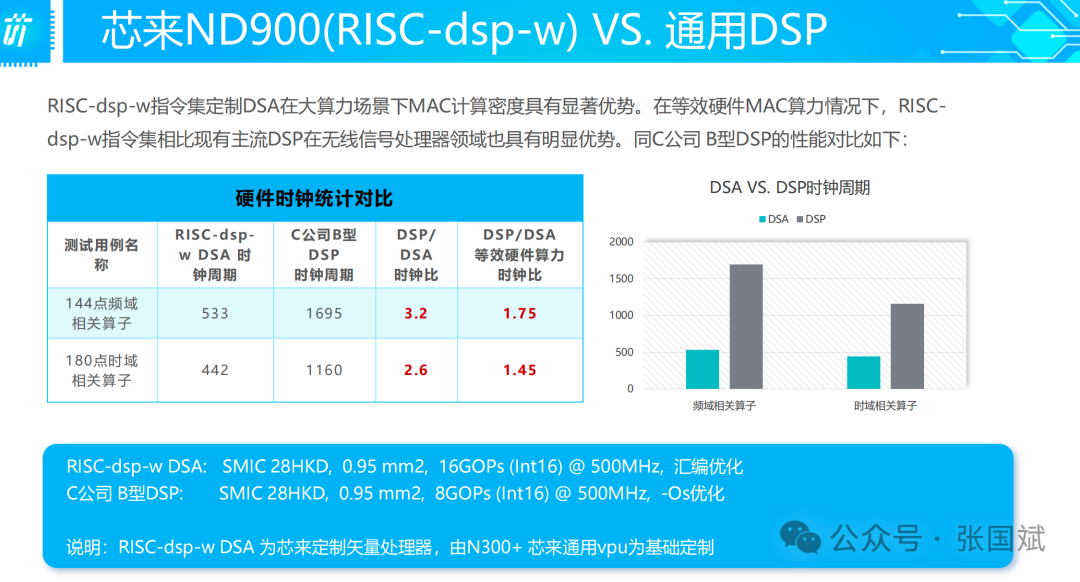

Under this architectural guidance, the ND900 processor developed in collaboration with ChipRise has become the first DSP core to support the RISC-dsp-W instruction set, demonstrating significant advantages over traditional DSPs in power density, instruction efficiency, and flexibility.

4. Self-Developed High-Performance DSP: Unlocking the Potential of Domestic Architectures

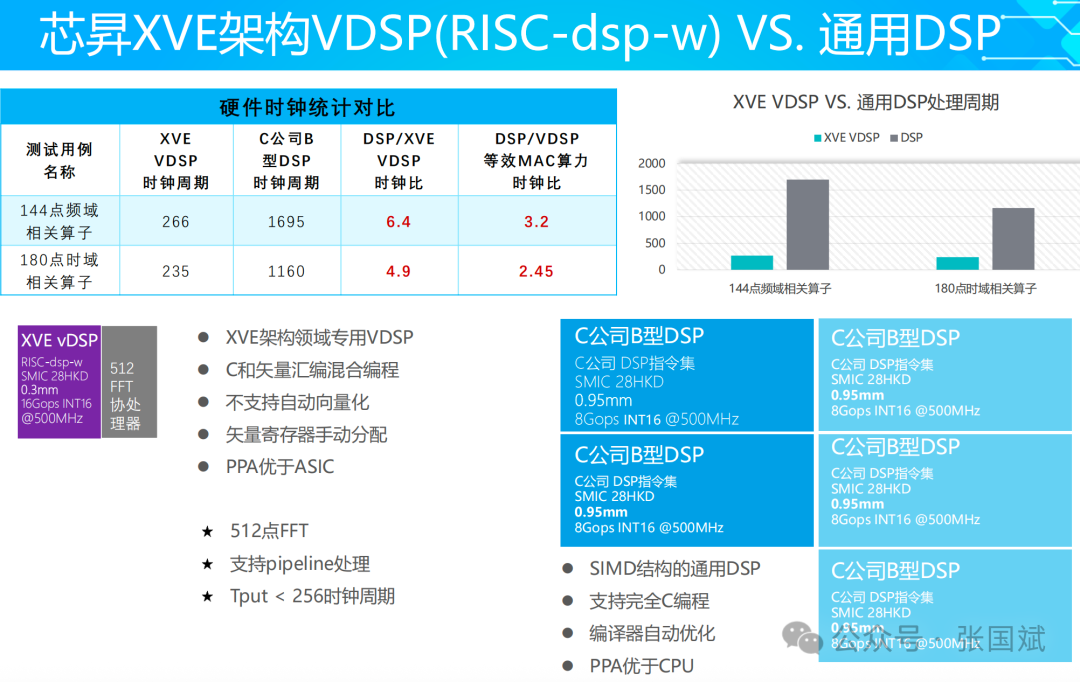

At the end of his speech, Li Gaoshan introduced a newly released self-developed DSP architecture based on RISC-dsp-W. Its core features are as follows:

Hybrid programming model: Combining C language with vector assembly, balancing ease of use and extreme performance;

Automatic vectorization adaptation: Flexibly configuring the VPU (Vector Processing Unit) for target algorithms;

High instruction efficiency: Reducing area to one-third under the same computing power, significantly lowering power consumption;

Minimalist design philosophy: Eliminating unnecessary instructions and functional units to maximize PPA compression.

As Li Gaoshan metaphorically stated: “General DSPs are like sedans, while customized RISC-V DSPs are more like race cars—stripped of redundancy, lightweight, with the goal of achieving extreme performance in specific domains.”

5. RISC-V + DSP + DSA = The Key to Breaking Through Communication Chips

Faced with the impasse of “homogenization and price wars” in communication chips,Li Gaoshan pointed outthat the architectural path centered on RISC-V, directed by DSA, and implemented through RISC-dsp-W is providing the industry with a new solution to achieve the optimal balance between performance and flexibility. The promotion by leading companies like ChipRise marks a critical juncture for domestic DSP technology to move towards autonomous control and high-performance development in the wireless communication field.

Author’s Note: The RISC-dsp-W related standards are actively being promoted in the DSP TG of the RISC-V Foundation and may be officially released in the future as Z extensions (such as Zvspw), which are expected to have a profound impact on domestic and international communication and AI chip design. It is recommended to keep an eye on the latest developments of this instruction set in the open-source community and industry.

Recommended Exciting Articles

1. Another semiconductor giant in Shanghai is about to “fall”? Huawei and BYD have invested in it.

2. Why did Huada Jiutian terminate the acquisition of Xinheng Semiconductor?

3. Starting from Plato’s Allegory of the Cave, how does Honor Magic V5 reconstruct the narrative of technology and humanities in the AI era?

4. History! Global leader! The unmanned mining truck based on the Dapeng Liyang TerraSight chip successfully demonstrated.

5. How should Chinese EDA break through?

6. Heavyweight! Unisoc is about to go public!

7. Who is the real competitor of Hongmeng Zhixing?

8. Foldable phones have reached their limits; it’s time to focus on experience.

9. Breaking the monopoly of ADI and TI! The first internationally leading, Chengdu Huamai releases a new generation of high-speed, high-precision RF direct sampling ADC!

10. In response to the US’s supply cut of EDA and IP, the “Enlightenment” system released by the Chinese Academy of Sciences has shocked American netizens, saying “another market is lost!”

11. Countering the heavens! Taiwan Province of China has actually listed Huawei and SMIC in the export control list!

12. Smart glasses are selling like hotcakes! Revealing the smart glasses industry chain!

13. Foreign media: Ren Zhengfei said that with open-source and chip packaging technology, China can cope with US technology restrictions.