Inphi is a leader in high-speed data movement interconnects, dedicated to rapidly transferring large data sets globally, between data centers and within data centers.

We have adopted Tempus ECO and Tempus Signoff across all advanced process node projects. Due to the large scale of the designs, we chose to run flattened static timing analysis (STA) and fully leverage Tempus’s DSTA and CMMMC features. This enables our designers to complete signoff faster, meeting time-to-market requirements. Due to high correlation, the Tempus solution also converges faster with Innovus Implementation, achieving better PPA (Power, Performance, Area). Our designers can confidently use Tempus ECO and Signoff for signoff.

—— WEIKAI SUN

Vice President of Engineering

Challenges

●Need to perform full-chip flattened signoff on a machine with 500GB of memory.

●On the same machine, STA nearly exhausts all memory to complete the analysis for a single process corner.

●Need to run multiple modes and multiple process corners simultaneously, rather than just a single process corner.

Advantages

●Integrating Tempus ECO into the Innovus Implementation system and combining it with the Quantus parasitic extraction solution reduced the number of iterations.

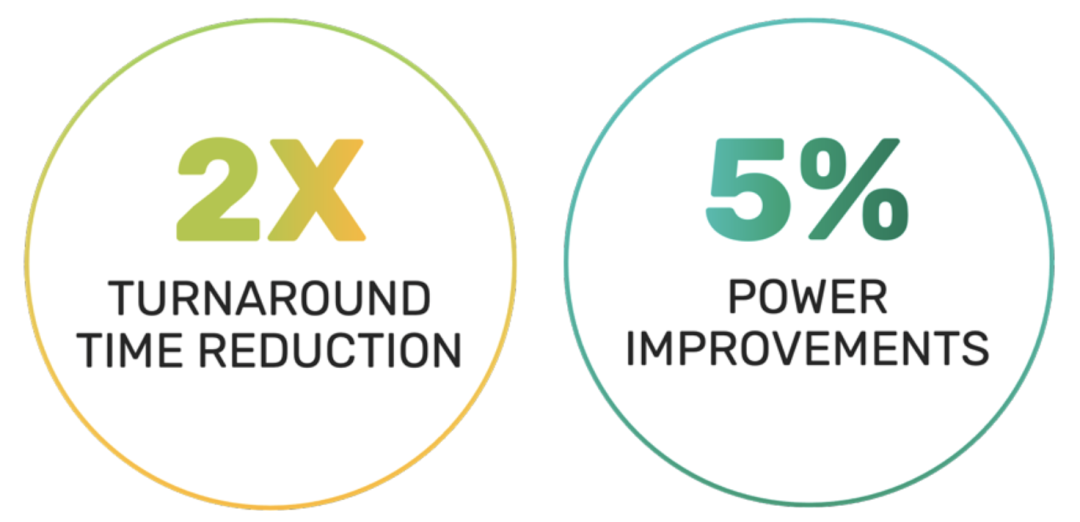

●Although most power optimizations were completed in the Genus Synthesis solution, an additional 5% power reduction was still achieved.

●Using DSTA, the CMMMC flattening was completed in a reasonable time.

▶CMMMC has about 25 views for establishing setup and hold time analysis, greatly improving our efficiency in completing tape-out on schedule.

▶Compared to single process corner STA, the runtime was reduced by 50% (DSTA CMMMC took about 10 hours to run and generate reports; single process corner STA took over 20 hours).

●Due to the shared signoff engine among Innovus, ECO, and Signoff, there is better correlation, which minimizes design convergence time.

●With top-level scope and ease of use, it allows for faster fixes to top-level interfaces and reduces the number of licenses required.

●Throughout the entire process from design cycle start to tape-out completion, Cadence engineers provided exceptional support.

Design

●7nm

●Using SOCV

●Using 16 CPUs

More Information

For more information about Tempus Timing Solution, please click below to “Read the Original”.

© 2025 Cadence Design Systems, Inc. All rights reserved. Cadence, the Cadence logo, and other Cadence marks listed at www.cadence.com/go/trademarks are trademarks or registered trademarks of Cadence Design Systems, Inc.

<<< Swipe to see more