IC engineers must have seen the requirement for low power design experience in job descriptions. So, what is low power design?

For backend engineers, this involves introducing multiple power lines and providing power to different power domains (PDs) based on the different voltage domains and global power network designs. To address potential issues during the power network supply process for multiple power/multiple voltage domains, low power cells need to be introduced. For simple voltage domain designs, IC engineers can manually global connect and then detail route, without needing to pay attention to the placement of low power cells or the setting of islands. However, for complex power networks, IC engineers need to introduce Power Intent files, such as CPF (Common Power Format) and UPF (Unified Power Format), to implement complex multi-voltage domain designs, voltage domain shutdowns, and even dynamic voltage scaling (DVFS) to control voltage variations across different voltage domains.

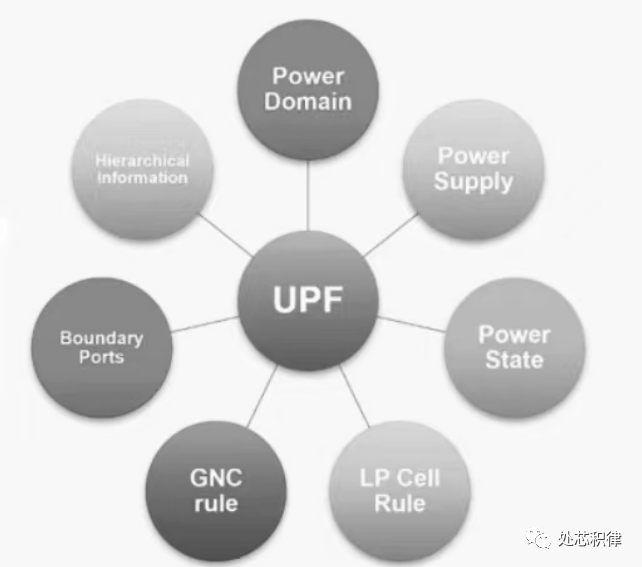

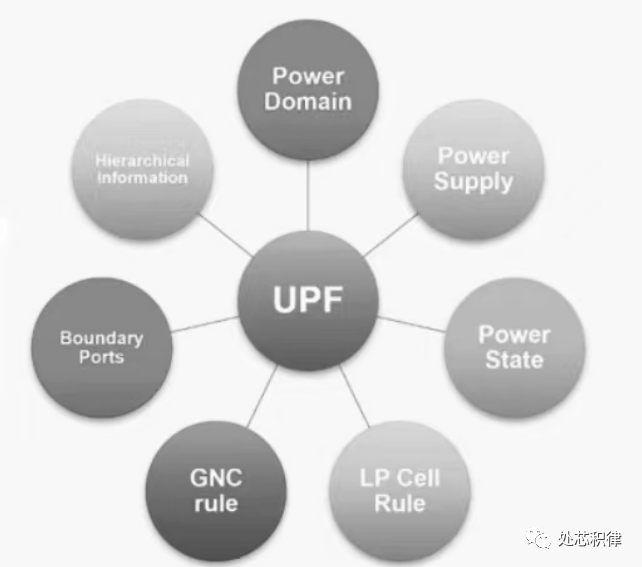

Figure 1 UPF files include/define the content of low power design

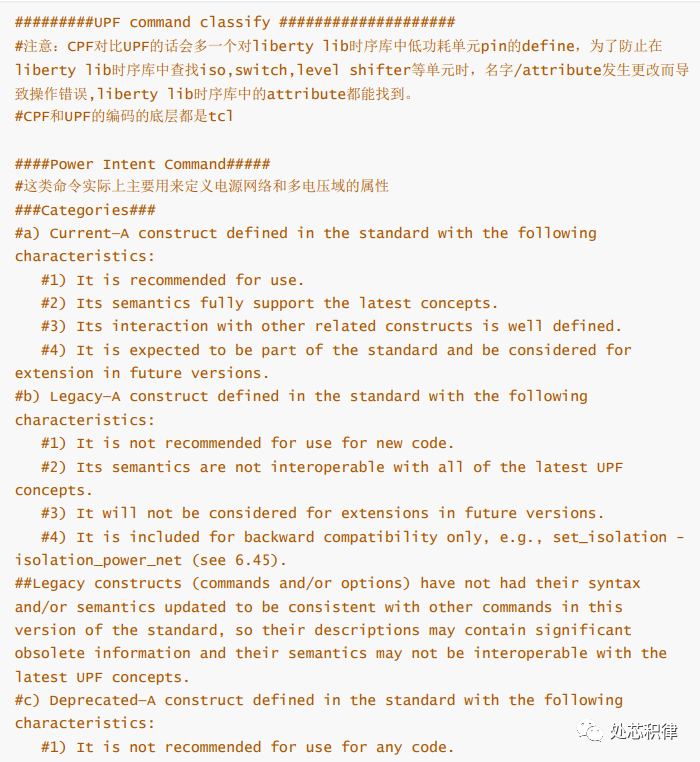

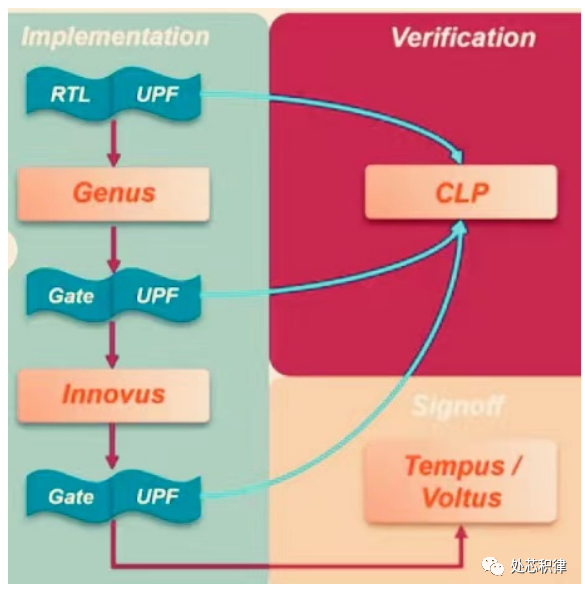

In fact, UPF focuses on describing the power architecture of the chip (such as the definition of voltage sources, power state definitions, connections of low power cells ISO, MTCMOS (PSW), LVL, ELS cells, power supply relationships, and layout information). The UPF file, like the SDC file, has its own writing style. UPF has long been recognized as a standard protocol. Backend engineers who have done low power design should know that when importing UPF 3.0 into Innovus, the file is not named UPF, but IEEE 1801. The following figure shows the usage standard of UPF, which is the IEEE low power design standard, including the man page of UPF instructions and usage notes.

Basics of UPF Coding (Content: power network definition, multi-voltage domain design, low power modes, low power cell rules, chip edge power definitions, IP power descriptions).

In fact, UPF runs through the entire backend design. Different voltage domains have their corresponding library cells (including various .lib libraries). For example, 1.0V uses the 1.0V library, while 2.0V uses the 2.0V library. In synthesis, ISO, ICG, and LEVEL SHIFT are generally added, while SWITCH cells (MTCMOS four-pin chains) are added in physical design.

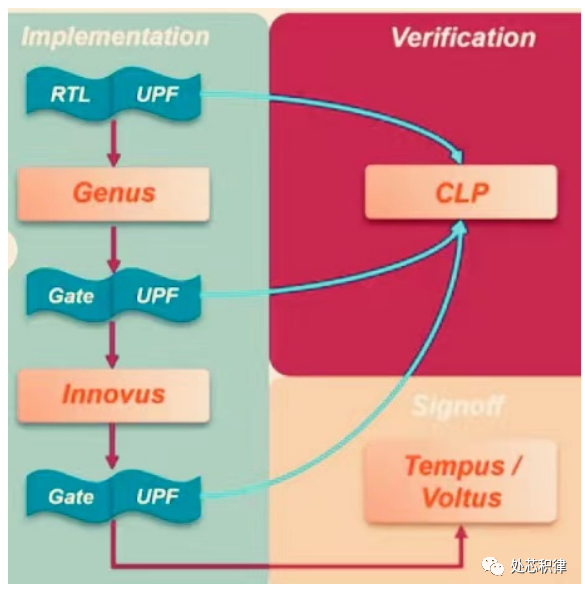

It is also worth noting that low power cells are generally added at the boundary of power domains. However, if some low power cells (ISO, level shifter) are added on the pins of macros, they cannot be placed at the voltage domain boundary. CLP verification mainly checks whether the UPF architecture (the contents) is written correctly, achieved through Cadence’s conformal tools. Tempus and Voltus are Cadence’s signoff tools for PT and PI.

Figure 2 UPF backend full process and signoff CLP, PI verification process

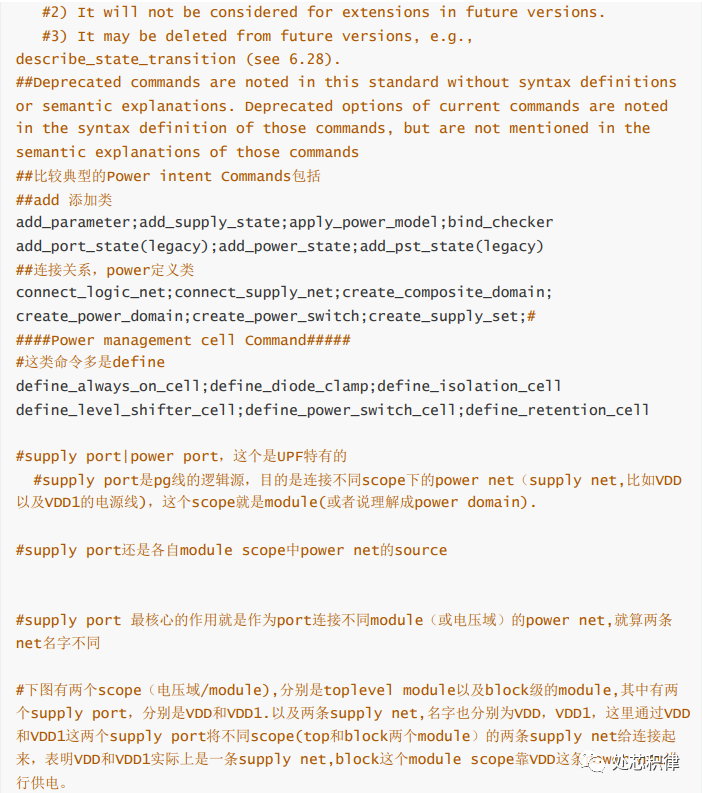

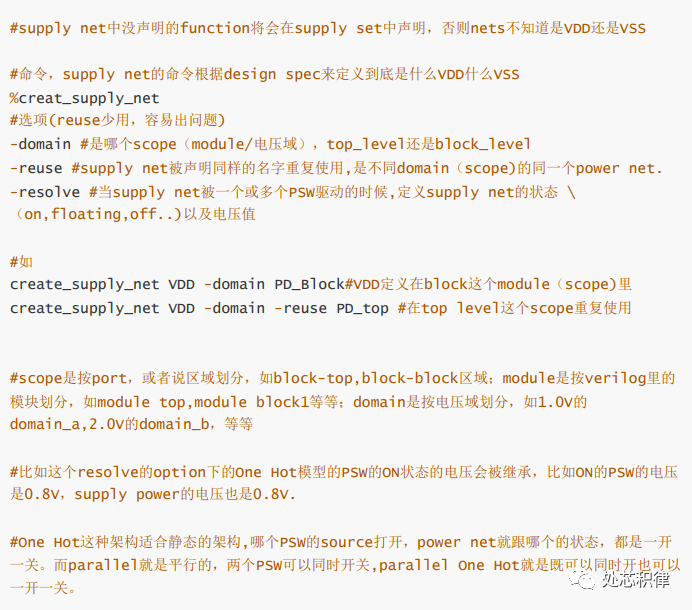

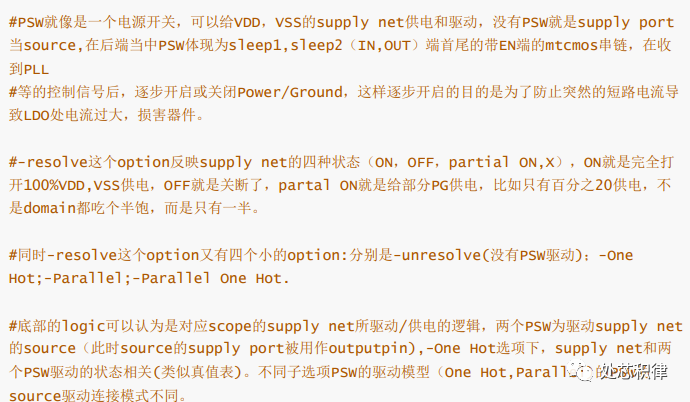

UPF power network definition supply net:

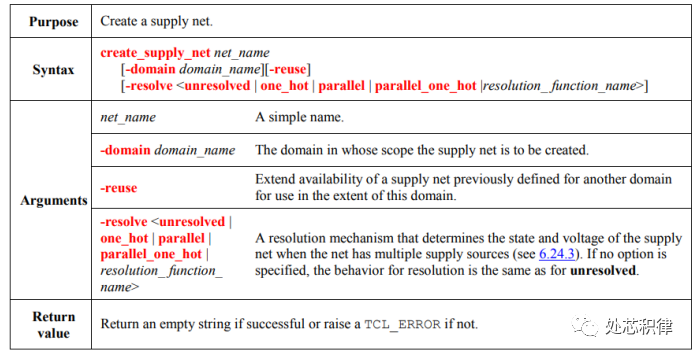

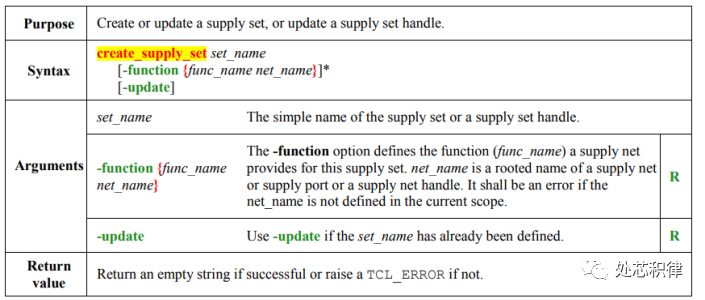

UPF power network definition supply set:

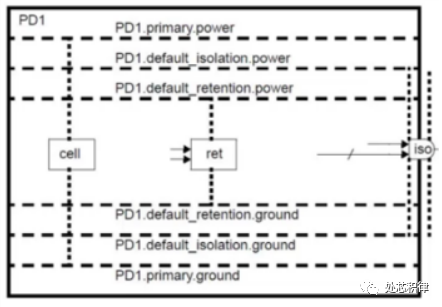

The figure shows that PD1’s supply set includes primary power to supply internal elements and a constant power grid for ISO and retention.

At this point, I have introduced the general content of UPF coding and its application process in the backend, as well as the two important UPF create commands: supply_net and supply_set. In the next article, I will take a UPF example for a multi-PD module and explain the UPF writing rules step by step, making it easier for IC engineers to create power network and voltage domain supply plans for their project modules.

Copyright belongs to the original author. If there is any infringement, please contact for deletion.

Does the university still use Protel 99 SE and 51 microcontroller teaching?

State Machine – The Universal Language of Microcontrollers (with Code)

What do C language pointers p, *p, &p, *&p, and &*p represent?

→ Follow to avoid getting lost ←