IntroductionLet’s discuss the aspects of chip design, tapeout, verification, manufacturing, and costs; tapeout is like taking a major exam for chip design.The importance of tapeout lies in its ability to verify whether the chip design is successful; it is a critical step in chip manufacturing, where the finalized design is handed over to the chip manufacturing plant to produce samples. This process checks whether the designed chip meets the design requirements or if further optimization is needed; if a chip that meets the requirements can be produced, then mass production can commence. The input of the above process is the chip project design, and the output is the completed chip wafer.1. Wafer Terminology

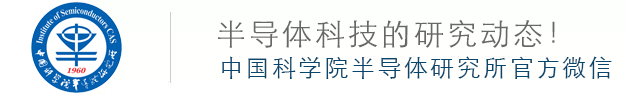

The input of the above process is the chip project design, and the output is the completed chip wafer.1. Wafer Terminology 1. Chip (chip, die), device (device), circuit (circuit), microchip (microchip), or bar: all these terms refer to the microchip patterns that occupy most of the surface area of the wafer;2. Scribe line (scribe line, saw line) or street (street, avenue): these areas are used to separate the spacing between different chips on the wafer. Scribe lines are usually blank, but some companies place alignment marks or test structures in the spacing areas;3. Engineering die and test die: these chips differ from formal chips or circuit chips. They include special devices and circuit modules used for electrical testing of the wafer production process;4. Edge die: chips located at the edge of the wafer that have incomplete mask coverage, resulting in area loss. More edge waste caused by larger individual chip sizes can be compensated by using larger diameter wafers. One of the driving forces for the semiconductor industry to develop larger diameter wafers is to reduce the area occupied by edge chips;5. Wafer crystal plane: the cross-section shown in the image indicates the lattice structure beneath the device, and the orientation of the device edge relative to the lattice structure is determined;6. Wafer flats/notches: the illustrated wafer has major flats and minor flats, indicating that this is a P-type <100> crystal orientation wafer. Both 300mm and 450mm diameter wafers use notches as lattice orientation markers. These flats and notches also assist in wafer alignment in some wafer production processes.2. Chip Tapeout Methods (Full Mask, MPW)Full Mask and MPW are both methods of tapeout for integrated circuits (handing over design results for production). Full Mask means that all masks in the manufacturing process serve a specific design; MPW stands for Multi Project Wafer, which means multiple projects share a single wafer, allowing multiple IC designs to be manufactured in the same process.1. Full Mask means that all masks in the manufacturing process serve a specific design; a Full Mask chip can produce thousands of dies from a single wafer; then it is packaged into chips to support large-scale customer demand.

1. Chip (chip, die), device (device), circuit (circuit), microchip (microchip), or bar: all these terms refer to the microchip patterns that occupy most of the surface area of the wafer;2. Scribe line (scribe line, saw line) or street (street, avenue): these areas are used to separate the spacing between different chips on the wafer. Scribe lines are usually blank, but some companies place alignment marks or test structures in the spacing areas;3. Engineering die and test die: these chips differ from formal chips or circuit chips. They include special devices and circuit modules used for electrical testing of the wafer production process;4. Edge die: chips located at the edge of the wafer that have incomplete mask coverage, resulting in area loss. More edge waste caused by larger individual chip sizes can be compensated by using larger diameter wafers. One of the driving forces for the semiconductor industry to develop larger diameter wafers is to reduce the area occupied by edge chips;5. Wafer crystal plane: the cross-section shown in the image indicates the lattice structure beneath the device, and the orientation of the device edge relative to the lattice structure is determined;6. Wafer flats/notches: the illustrated wafer has major flats and minor flats, indicating that this is a P-type <100> crystal orientation wafer. Both 300mm and 450mm diameter wafers use notches as lattice orientation markers. These flats and notches also assist in wafer alignment in some wafer production processes.2. Chip Tapeout Methods (Full Mask, MPW)Full Mask and MPW are both methods of tapeout for integrated circuits (handing over design results for production). Full Mask means that all masks in the manufacturing process serve a specific design; MPW stands for Multi Project Wafer, which means multiple projects share a single wafer, allowing multiple IC designs to be manufactured in the same process.1. Full Mask means that all masks in the manufacturing process serve a specific design; a Full Mask chip can produce thousands of dies from a single wafer; then it is packaged into chips to support large-scale customer demand. 2. MPW, or Multi Project Wafer, is similar to PCB panel prototyping, where multiple integrated circuit designs using the same process are placed on the same wafer for tapeout. After manufacturing, each design can obtain dozens of chip samples, which is sufficient for experiments and testing during the prototype design phase. This operation can reduce tapeout costs by 90%-95%, significantly lowering chip R&D costs.

2. MPW, or Multi Project Wafer, is similar to PCB panel prototyping, where multiple integrated circuit designs using the same process are placed on the same wafer for tapeout. After manufacturing, each design can obtain dozens of chip samples, which is sufficient for experiments and testing during the prototype design phase. This operation can reduce tapeout costs by 90%-95%, significantly lowering chip R&D costs. Wafer fabs have fixed MPW opportunities each year, called Shuttle, which departs at scheduled times. Different companies share wafers, and there are rules; MPW locks the area by SEAT, where a SEAT is generally a 3mm*4mm area. To ensure that different chip companies can participate in MPW, the number of SEATs reserved for each company is limited (more SEATs would increase costs, negating the significance of MPW). The advantage of MPW is that the tapeout cost is low, generally just a few hundred thousand, which effectively reduces risk; however, it is important to note that from a production perspective, MPW is still a complete production process, so it still takes time; an MPW typically requires 6 to 9 months, which delays chip delivery times.Since it is a shared wafer, the number of chips obtained through MPW will be limited, mainly used for internal verification testing by chip companies, and may be provided to a very small number of top customers. From this, it can be understood that MPW is an incomplete, non-mass-producible tapeout.3. Introduction to MPW from the perspective of wafer productionChip processing is still a relatively complex process. I believe many friends, after reading the wafer structure understood by the first and second parties, think it is as shown in the image below, where a box belongs to a chip company.

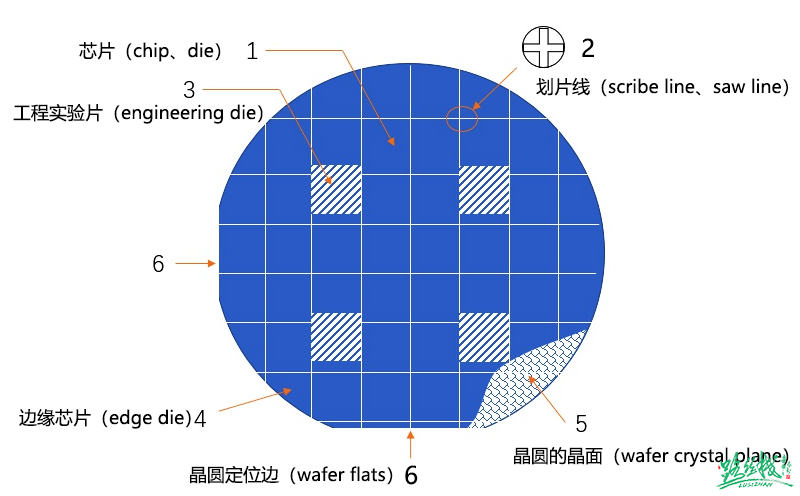

Wafer fabs have fixed MPW opportunities each year, called Shuttle, which departs at scheduled times. Different companies share wafers, and there are rules; MPW locks the area by SEAT, where a SEAT is generally a 3mm*4mm area. To ensure that different chip companies can participate in MPW, the number of SEATs reserved for each company is limited (more SEATs would increase costs, negating the significance of MPW). The advantage of MPW is that the tapeout cost is low, generally just a few hundred thousand, which effectively reduces risk; however, it is important to note that from a production perspective, MPW is still a complete production process, so it still takes time; an MPW typically requires 6 to 9 months, which delays chip delivery times.Since it is a shared wafer, the number of chips obtained through MPW will be limited, mainly used for internal verification testing by chip companies, and may be provided to a very small number of top customers. From this, it can be understood that MPW is an incomplete, non-mass-producible tapeout.3. Introduction to MPW from the perspective of wafer productionChip processing is still a relatively complex process. I believe many friends, after reading the wafer structure understood by the first and second parties, think it is as shown in the image below, where a box belongs to a chip company. However, this is not the case; it needs to be related to the photolithography technology in the wafer production process. Currently, photolithography technologies such as DUV/EUV mostly use reduction methods for exposure, as shown in the image below:

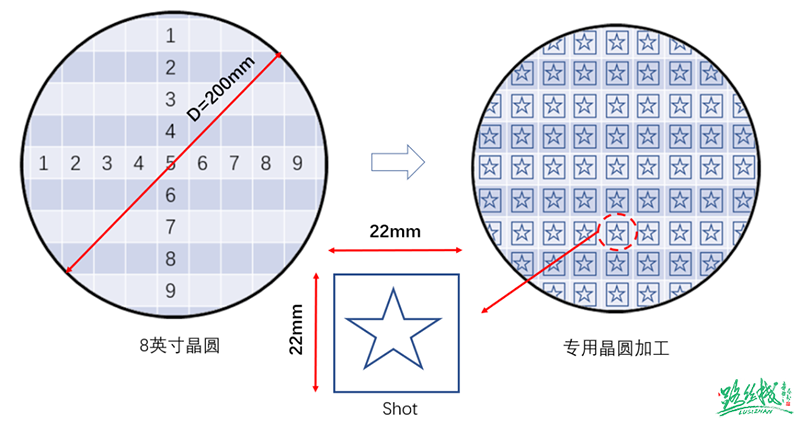

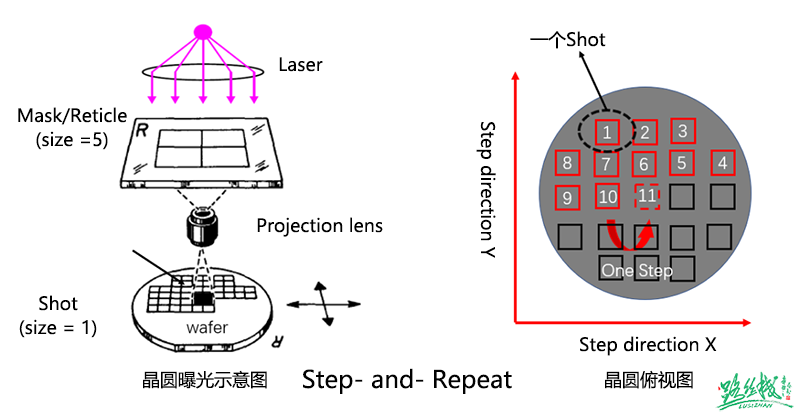

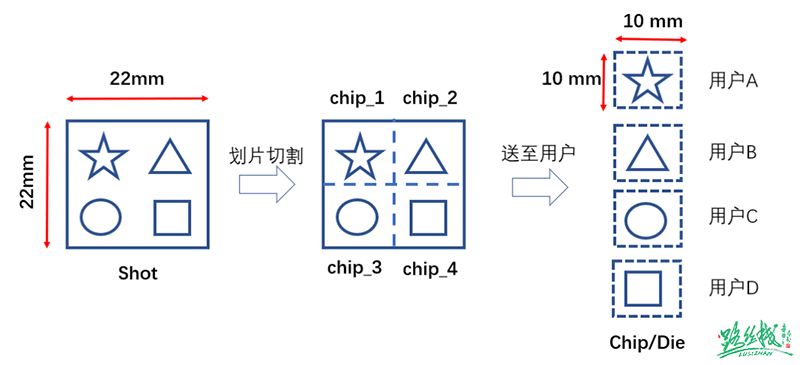

However, this is not the case; it needs to be related to the photolithography technology in the wafer production process. Currently, photolithography technologies such as DUV/EUV mostly use reduction methods for exposure, as shown in the image below: Using a 1:5 magnified mask for wafer exposure, the rectangular area exposed at one time is usually called a shot. After exposure, the photolithography machine automatically adjusts the wafer position for the next shot, and this cycle continues (Step-and-Repeat) until the entire wafer is completed. The area of one shot is the area shared by all users;As shown in the diagram below, one shot is divided into four small grids, each grid assigned to a vendor’s design, with MPW wafers generally accommodating fewer than 20 users.

Using a 1:5 magnified mask for wafer exposure, the rectangular area exposed at one time is usually called a shot. After exposure, the photolithography machine automatically adjusts the wafer position for the next shot, and this cycle continues (Step-and-Repeat) until the entire wafer is completed. The area of one shot is the area shared by all users;As shown in the diagram below, one shot is divided into four small grids, each grid assigned to a vendor’s design, with MPW wafers generally accommodating fewer than 20 users. 3. Chip ECO ProcessECO stands for Engineering Change Order. ECO can occur before, during, or after Tapeout; ECO after Tapeout may require minor changes to a few Metal layers or significant changes to dozens of Metal layers, or even a complete tapeout. The implementation process of ECO is shown in the diagram below:

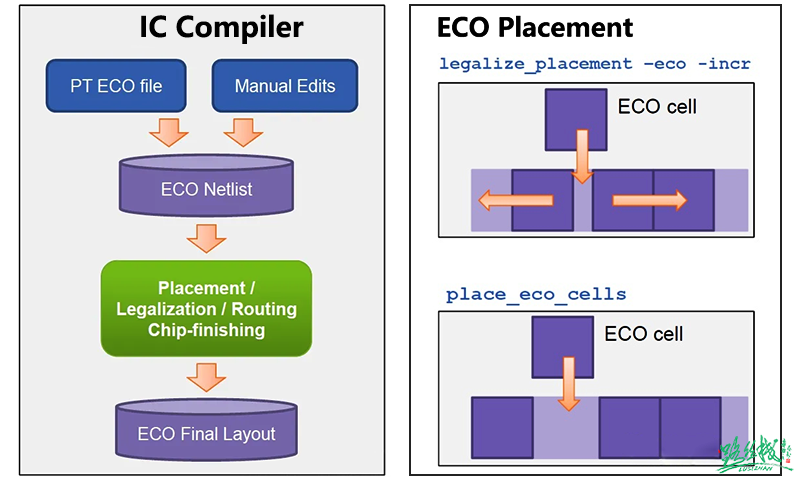

3. Chip ECO ProcessECO stands for Engineering Change Order. ECO can occur before, during, or after Tapeout; ECO after Tapeout may require minor changes to a few Metal layers or significant changes to dozens of Metal layers, or even a complete tapeout. The implementation process of ECO is shown in the diagram below: If the chips from MPW or Full Mask have functional or performance defects, adjustments can be made to the circuit and standard cell layout through ECO, making small-scale optimizations while keeping the original design layout and routing results largely unchanged, ultimately achieving the chip’s sign-off standards. Violations cannot be fixed through the backend layout and routing process (repeating the process is too time-consuming) but must be optimized through the ECO process for timing, DRC, DRV, and power consumption.4. Tapeout Corners1. Corners in chip manufacturing are a physical process, subject to process variations (including doping concentration, diffusion depth, etching degree, etc.), leading to differences between batches, between different wafers of the same batch, and between different chips on the same wafer.

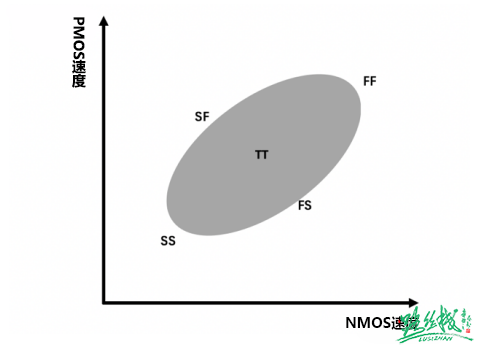

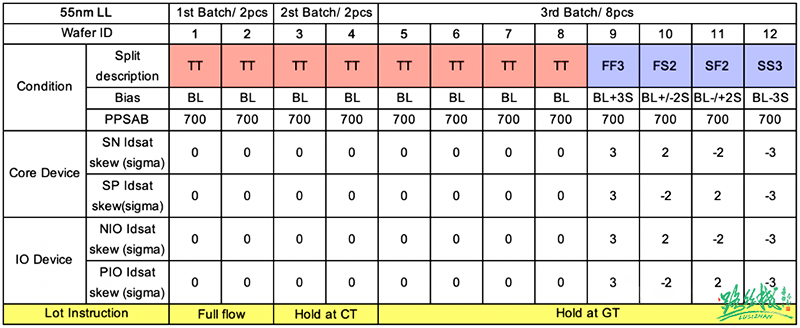

If the chips from MPW or Full Mask have functional or performance defects, adjustments can be made to the circuit and standard cell layout through ECO, making small-scale optimizations while keeping the original design layout and routing results largely unchanged, ultimately achieving the chip’s sign-off standards. Violations cannot be fixed through the backend layout and routing process (repeating the process is too time-consuming) but must be optimized through the ECO process for timing, DRC, DRV, and power consumption.4. Tapeout Corners1. Corners in chip manufacturing are a physical process, subject to process variations (including doping concentration, diffusion depth, etching degree, etc.), leading to differences between batches, between different wafers of the same batch, and between different chips on the same wafer. On a wafer, it is impossible for the carrier drift velocity at every point to be the same; as voltage and temperature vary, their characteristics will also differ, leading to classifications known as PVT (Process, Voltage, Temperature), with Process further divided into different corners: TT: Typical N Typical P FF: Fast N Fast P SS: Slow N Slow P FS: Fast N Slow P SF: Slow N Fast P The first letter represents NMOS, and the second letter represents PMOS, referring to different concentrations of N-type and P-type doping. NMOS and PMOS are manufactured independently in the process and do not affect each other, but for circuits, NMOS and PMOS operate simultaneously, leading to situations where NMOS is fast while PMOS is also fast or slow, resulting in the four cases of FF, SS, FS, and SF. Adjustments made through Process simulate the speed of devices, and different levels of FF and SS are set based on the magnitude of deviations. Under normal circumstances, most are TT, and the above five corners can cover about 99.73% of the range within +/-3 sigma, which conforms to normal distribution.2. The significance of corner wafers during engineering tapeout is that the FAB will perform inline variation adjustments on key layers, and some may also use backup wafers to ensure that the shipped wafer devices are on target, i.e., near the TT corner. If the sole purpose is to produce some samples, corner verification may not be necessary, but if preparing for subsequent mass production, it must be considered. Due to process deviations during production, corners are estimates of normal fluctuations in the production line, and the FAB will have corner verification requirements for mass-produced chips. Therefore, corners must be satisfied during the design phase, and circuits must be simulated under various corner and extreme temperature conditions to ensure they operate normally across all corners, which will lead to higher yield in the final produced chips.3. Corner Split Table Strategy For products, generally achieving specifications at corners is normal; specifications typically have 6 sigma, such as FF2 (or 2FF) indicating a shift of 2 sigma towards the fast direction, and SS3 (or 3SS) indicating a shift of 3 sigma towards the slow direction. Sigma mainly represents the fluctuation of Vt; larger fluctuations lead to larger sigma. Here, 3 sigma is within the spec line of the process devices, allowing for slight exceedance, as fluctuations on the line cannot be perfectly aligned with the spec.Below is an example of a 55nm Logic process chip’s proposed corner split table:

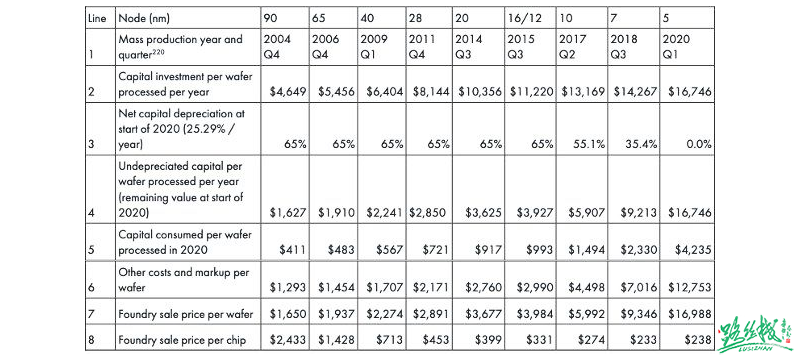

On a wafer, it is impossible for the carrier drift velocity at every point to be the same; as voltage and temperature vary, their characteristics will also differ, leading to classifications known as PVT (Process, Voltage, Temperature), with Process further divided into different corners: TT: Typical N Typical P FF: Fast N Fast P SS: Slow N Slow P FS: Fast N Slow P SF: Slow N Fast P The first letter represents NMOS, and the second letter represents PMOS, referring to different concentrations of N-type and P-type doping. NMOS and PMOS are manufactured independently in the process and do not affect each other, but for circuits, NMOS and PMOS operate simultaneously, leading to situations where NMOS is fast while PMOS is also fast or slow, resulting in the four cases of FF, SS, FS, and SF. Adjustments made through Process simulate the speed of devices, and different levels of FF and SS are set based on the magnitude of deviations. Under normal circumstances, most are TT, and the above five corners can cover about 99.73% of the range within +/-3 sigma, which conforms to normal distribution.2. The significance of corner wafers during engineering tapeout is that the FAB will perform inline variation adjustments on key layers, and some may also use backup wafers to ensure that the shipped wafer devices are on target, i.e., near the TT corner. If the sole purpose is to produce some samples, corner verification may not be necessary, but if preparing for subsequent mass production, it must be considered. Due to process deviations during production, corners are estimates of normal fluctuations in the production line, and the FAB will have corner verification requirements for mass-produced chips. Therefore, corners must be satisfied during the design phase, and circuits must be simulated under various corner and extreme temperature conditions to ensure they operate normally across all corners, which will lead to higher yield in the final produced chips.3. Corner Split Table Strategy For products, generally achieving specifications at corners is normal; specifications typically have 6 sigma, such as FF2 (or 2FF) indicating a shift of 2 sigma towards the fast direction, and SS3 (or 3SS) indicating a shift of 3 sigma towards the slow direction. Sigma mainly represents the fluctuation of Vt; larger fluctuations lead to larger sigma. Here, 3 sigma is within the spec line of the process devices, allowing for slight exceedance, as fluctuations on the line cannot be perfectly aligned with the spec.Below is an example of a 55nm Logic process chip’s proposed corner split table: ① #1 & #2 Two pilot wafers, one blind sealed, one for CP measurement;② #3 & #4 Two wafers held at Contact, reserved for later revision engineering wafers, which can save ECO tapeout time;③ #5~#12 Eight wafers held at Poly, waiting for pilot results to see if adjustments to device speed are needed and to verify corners;④ In addition to reserving enough chips for testing and verification, Metal Fix, as many wafers as possible should be reserved for mass production shipping based on project needs.4. Confirming Corner ResultsFirst, most should fall within the window range determined by the four corners; if there are significant deviations, it may indicate a process shift. If the yield of each corner is unaffected and meets expectations, it indicates that the process window is sufficient. If individual conditions have low yield, the process window needs to be adjusted. The purpose of corner wafers is to verify design margins and assess whether yield is compromised. Generally, chips exceeding the performance range defined by this corner constraint are discarded.Corner verification is benchmarked against WAT test results, generally led by the FAB, but the costs of corner wafers are borne by the design company. Generally, for mature and stable processes, chips on the same wafer, from the same batch, or even from different batches have very similar parameters, and the range of deviations is relatively small. Process corners (Process Corner) PVT (Process Voltage Temperature) process errors differ from bipolar transistors; MOSFET parameters vary significantly between different chips and batches.To alleviate the difficulties of circuit design tasks to some extent, process engineers must ensure that device performance remains within a certain range. Generally, they strictly control expected parameter variations by discarding chips that exceed this performance range.① The speed of MOS transistors refers to the threshold voltage levels; fast corresponds to low threshold voltage, slow corresponds to high threshold voltage. GBW=GM/CC, under the same conditions, the lower the vth, the higher the gm value, thus the larger the GBW and the faster the speed. (Specific situations require specific analysis)② The speed of resistors. Fast corresponds to small square resistance, slow corresponds to large square resistance.③ The speed of capacitors. Fast corresponds to minimum capacitance, slow corresponds to maximum capacitance.5. Tapeout Costs and Wafer PricesThe tapeout mask cost for 40nm is approximately $800,000 to $900,000, and the wafer cost per piece is around $3,000 to $4,000, plus IP merge, totaling around 7 to 8 million RMB.Tapeout for 28nm process requires $2 million; for 14nm process, it requires $5 million; for 7nm process, it requires $15 million; for 5nm process, it requires $47.25 million; and for 3nm process, it may exceed $100 million; among the main tapeout costs, the mask is the most expensive.The more advanced the process node, the more mask layers are required; each layer of “mask” corresponds to one application of photoresist, exposure, development, etching, etc., involving material costs and equipment depreciation costs, all of which must be borne by fabless customers!28nm requires about 40 layers, 14nm requires 60 masks; 7nm requires 80 or even over a hundred masks; one layer of mask costs $80,000, thus chips must be mass-produced to lower costs!For example, in the case of 40nm MCU process: if producing 10 wafers, the cost per wafer is (900,000 + 4,000*10)/10 = $94,000; if producing 10,000 wafers, the cost per wafer is (900,000 + 4,000*10,000)/10,000 = $4,090. (The larger the wafer quantity, the cheaper it becomes; different manufacturers also have different quotes.)

① #1 & #2 Two pilot wafers, one blind sealed, one for CP measurement;② #3 & #4 Two wafers held at Contact, reserved for later revision engineering wafers, which can save ECO tapeout time;③ #5~#12 Eight wafers held at Poly, waiting for pilot results to see if adjustments to device speed are needed and to verify corners;④ In addition to reserving enough chips for testing and verification, Metal Fix, as many wafers as possible should be reserved for mass production shipping based on project needs.4. Confirming Corner ResultsFirst, most should fall within the window range determined by the four corners; if there are significant deviations, it may indicate a process shift. If the yield of each corner is unaffected and meets expectations, it indicates that the process window is sufficient. If individual conditions have low yield, the process window needs to be adjusted. The purpose of corner wafers is to verify design margins and assess whether yield is compromised. Generally, chips exceeding the performance range defined by this corner constraint are discarded.Corner verification is benchmarked against WAT test results, generally led by the FAB, but the costs of corner wafers are borne by the design company. Generally, for mature and stable processes, chips on the same wafer, from the same batch, or even from different batches have very similar parameters, and the range of deviations is relatively small. Process corners (Process Corner) PVT (Process Voltage Temperature) process errors differ from bipolar transistors; MOSFET parameters vary significantly between different chips and batches.To alleviate the difficulties of circuit design tasks to some extent, process engineers must ensure that device performance remains within a certain range. Generally, they strictly control expected parameter variations by discarding chips that exceed this performance range.① The speed of MOS transistors refers to the threshold voltage levels; fast corresponds to low threshold voltage, slow corresponds to high threshold voltage. GBW=GM/CC, under the same conditions, the lower the vth, the higher the gm value, thus the larger the GBW and the faster the speed. (Specific situations require specific analysis)② The speed of resistors. Fast corresponds to small square resistance, slow corresponds to large square resistance.③ The speed of capacitors. Fast corresponds to minimum capacitance, slow corresponds to maximum capacitance.5. Tapeout Costs and Wafer PricesThe tapeout mask cost for 40nm is approximately $800,000 to $900,000, and the wafer cost per piece is around $3,000 to $4,000, plus IP merge, totaling around 7 to 8 million RMB.Tapeout for 28nm process requires $2 million; for 14nm process, it requires $5 million; for 7nm process, it requires $15 million; for 5nm process, it requires $47.25 million; and for 3nm process, it may exceed $100 million; among the main tapeout costs, the mask is the most expensive.The more advanced the process node, the more mask layers are required; each layer of “mask” corresponds to one application of photoresist, exposure, development, etching, etc., involving material costs and equipment depreciation costs, all of which must be borne by fabless customers!28nm requires about 40 layers, 14nm requires 60 masks; 7nm requires 80 or even over a hundred masks; one layer of mask costs $80,000, thus chips must be mass-produced to lower costs!For example, in the case of 40nm MCU process: if producing 10 wafers, the cost per wafer is (900,000 + 4,000*10)/10 = $94,000; if producing 10,000 wafers, the cost per wafer is (900,000 + 4,000*10,000)/10,000 = $4,090. (The larger the wafer quantity, the cheaper it becomes; different manufacturers also have different quotes.) Wafer foundry prices sourced from the internetTaiwan Semiconductor Manufacturing Company (TSMC) provided the latest quote this year: the most advanced process at 3nm costs $19,865 per wafer, approximately 142,000 RMB.ConclusionThere are several important stages from chip design to finished product: design -> tapeout -> packaging -> testing, but the cost composition of chips varies significantly, generally comprising 20% labor costs, 40% tapeout, 35% packaging, and 5% testing.

Wafer foundry prices sourced from the internetTaiwan Semiconductor Manufacturing Company (TSMC) provided the latest quote this year: the most advanced process at 3nm costs $19,865 per wafer, approximately 142,000 RMB.ConclusionThere are several important stages from chip design to finished product: design -> tapeout -> packaging -> testing, but the cost composition of chips varies significantly, generally comprising 20% labor costs, 40% tapeout, 35% packaging, and 5% testing.

Tapeout is a high-risk endeavor, with risks ranging from 15% to 35%; different teams and chip types have different probabilities. Some analog chip companies, even with complete teams and clear ideas, took 8 years and 18 tapeouts to finally complete the verification of sensor analog computing IP, creating the ideal ultra-low power, ultra-close transmission chip.

END

The reproduced content only represents the author’s viewsand does not represent the position of the Institute of Semiconductors, Chinese Academy of SciencesEditor: Xiao ShuaiEditor: Liu Kuai Qian’s Fish Submission email: [email protected]