Column Introduction

“Automotive Controller Disassembly” column will share the disassembly analysis of intelligent automotive controllers, presenting the latest reference designs and selection schemes for mass-produced controllers.

This article will decode the design scheme of the SAIC Roewe RX5 MAX domain controller. The Tier1 of this scheme is the joint venture company Chuangshi Intelligent Driving established by SAIC and TTTech. The Roewe RX5 MAX is equipped with 3 millimeter-wave radars, 6 full HD cameras, and 12 ultrasonic radars, enabling approximately 20 intelligent assisted driving functions.

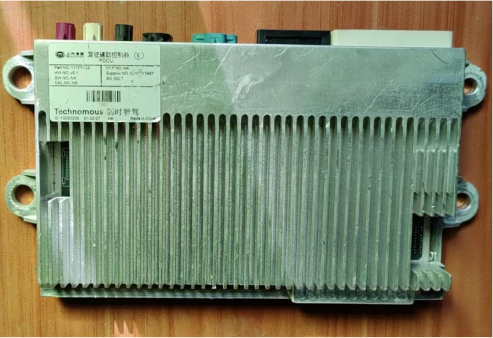

Front View of the Autonomous Driving Domain Controller Shell

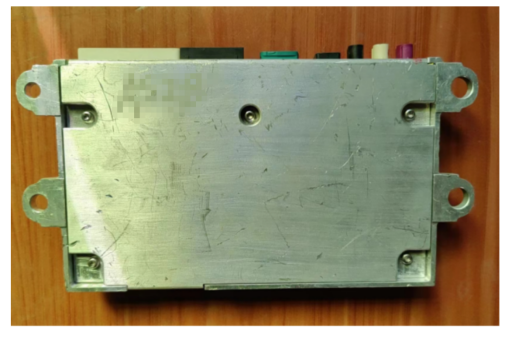

Back View of the Autonomous Driving Domain Controller Shell

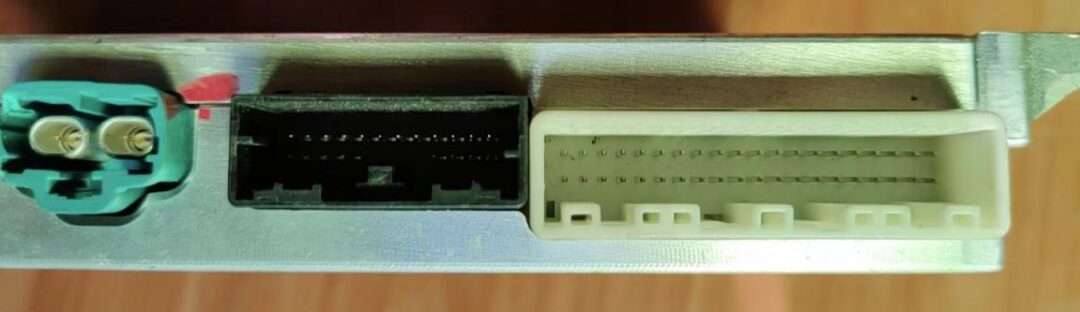

The above image shows the power, CAN, GPIO, and Gigabit Ethernet terminal interfaces of the Chuangshi Intelligent Driving Domain Controller

The above image shows the camera and antenna terminal of the Chuangshi Intelligent Driving Domain Controller

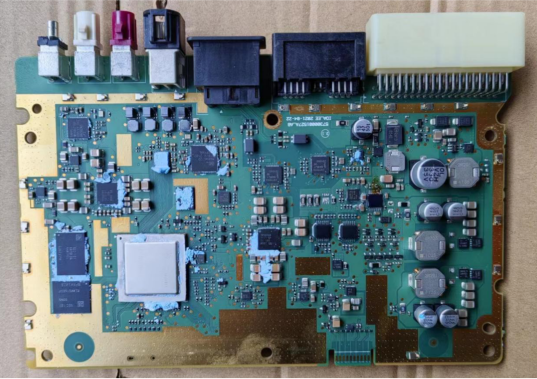

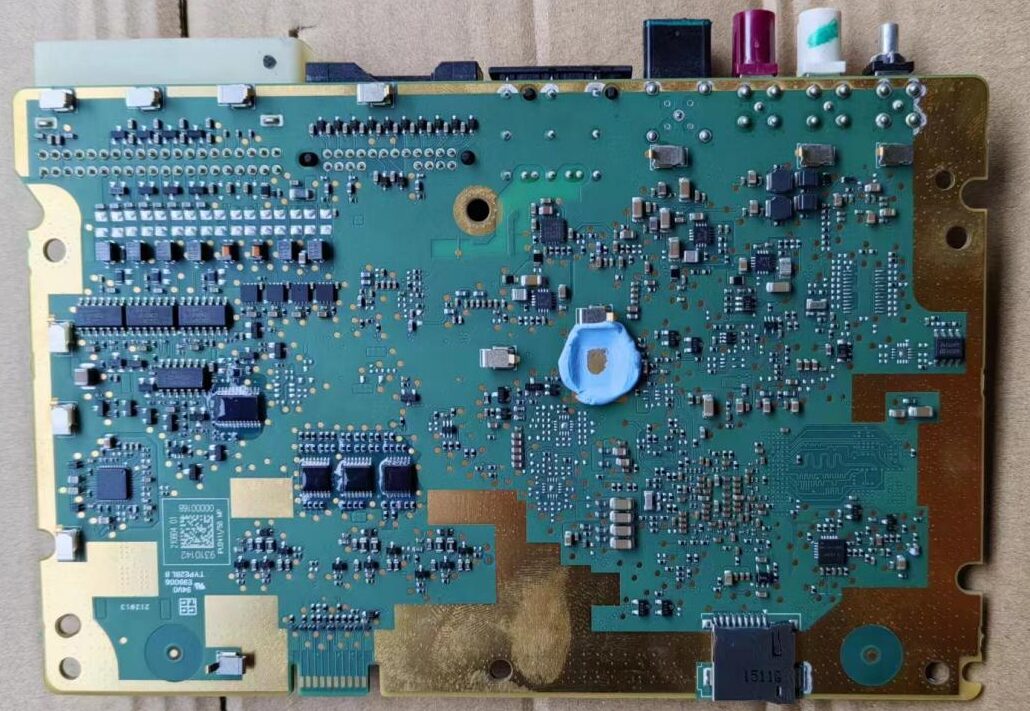

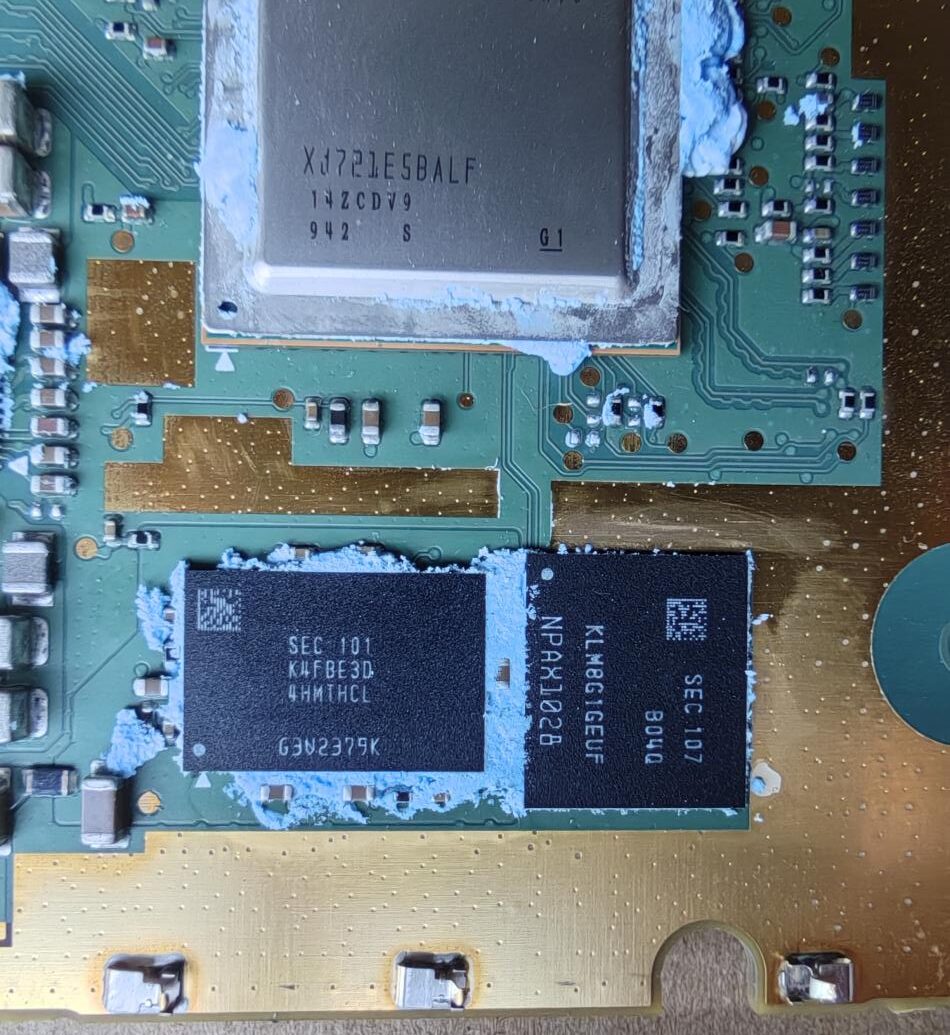

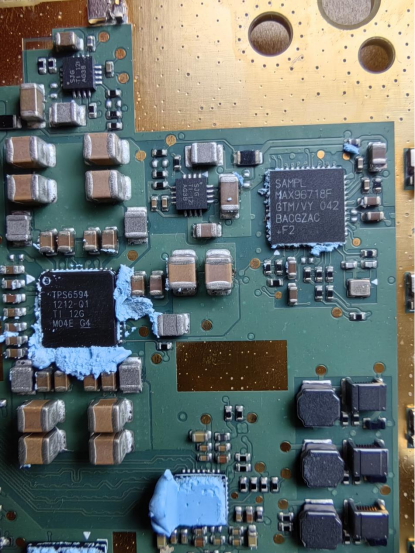

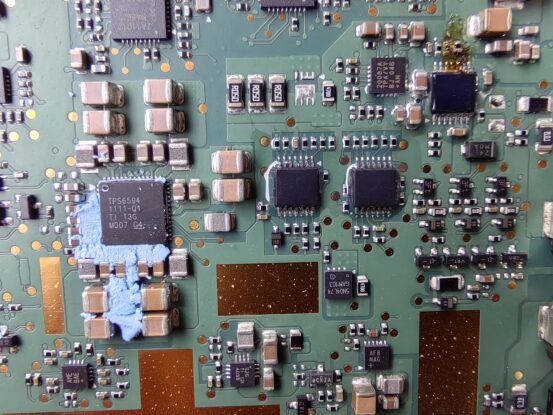

PCB Front View

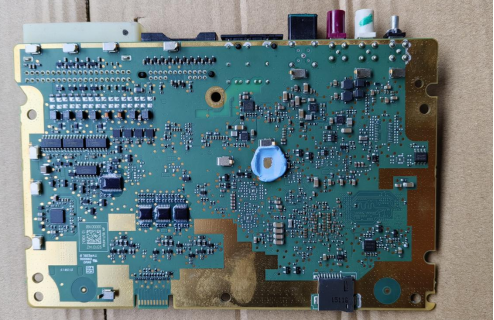

PCB Back View

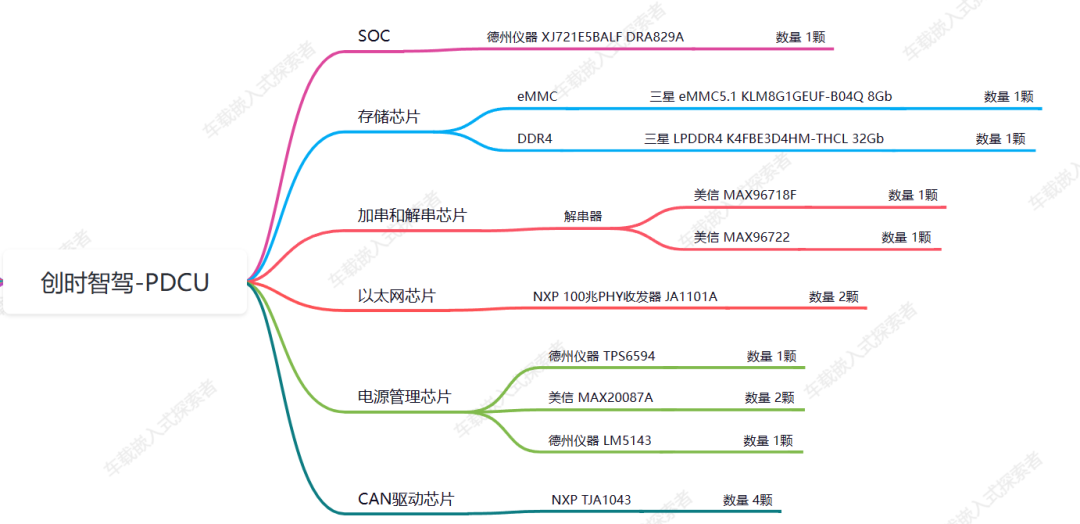

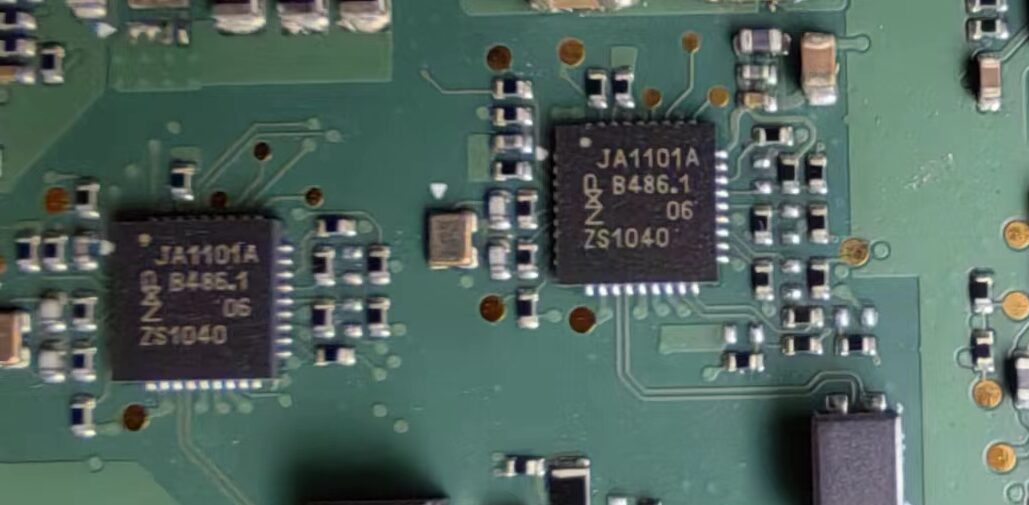

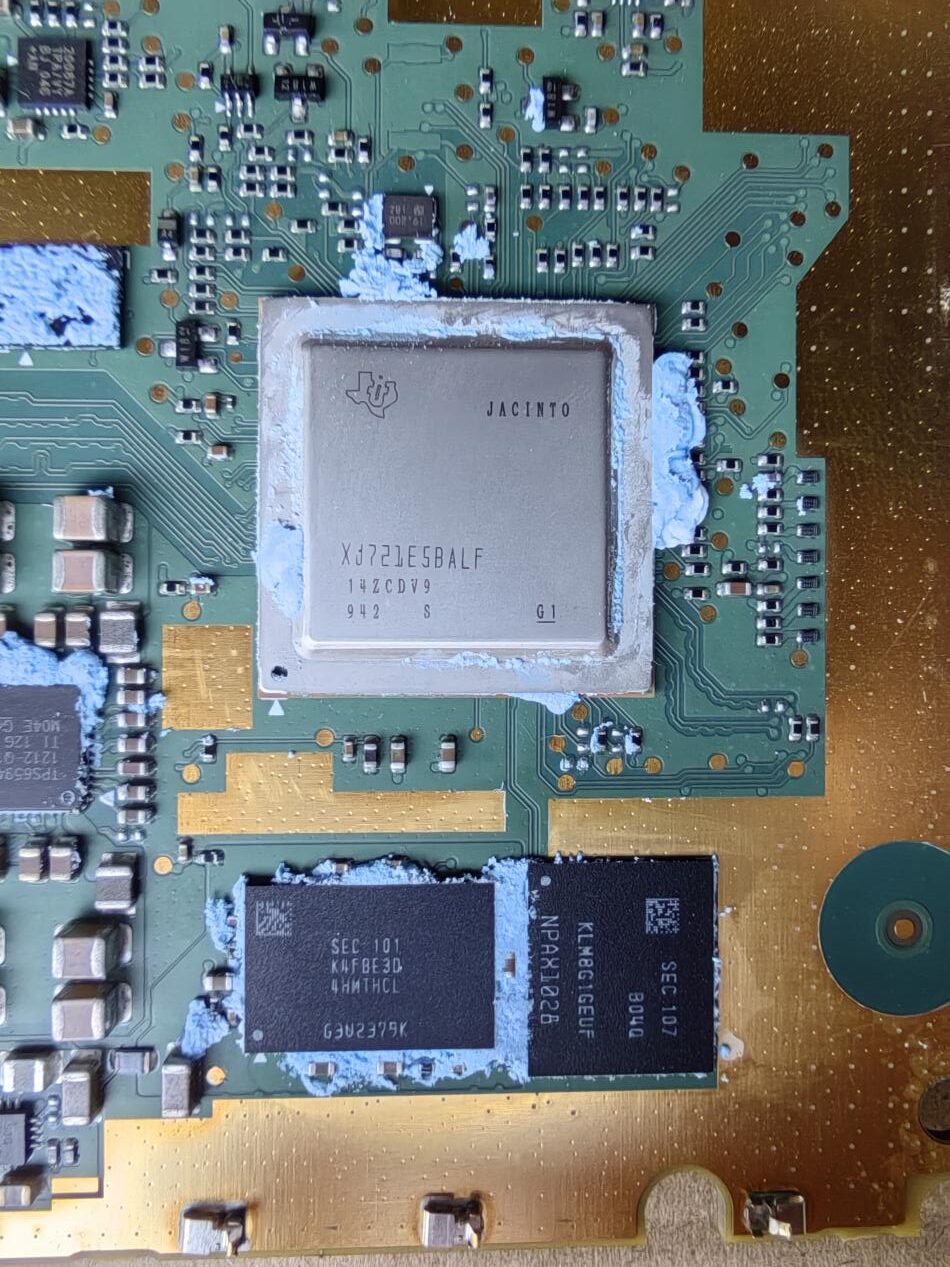

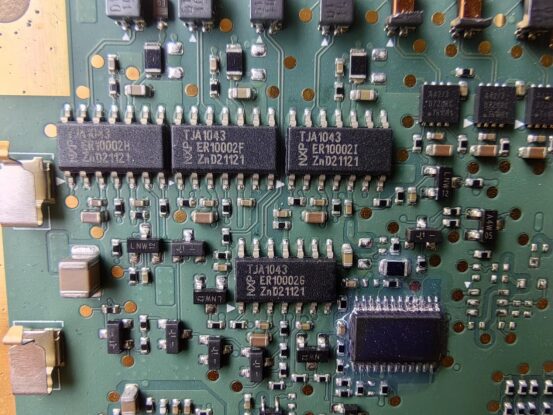

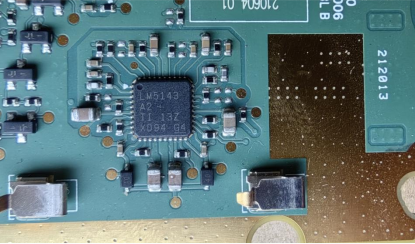

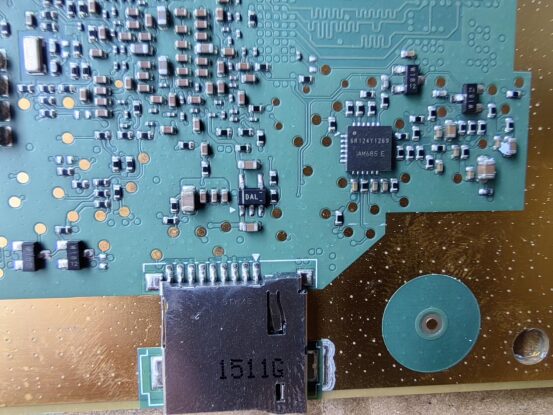

The Chuangshi Intelligent Driving domain controller uses a Texas Instruments DRA829 as the main control SOC, responsible for the implementation of perception and planning algorithms; the storage chip consists of a Samsung EMMC chip and a DDR4 chip; the deserializer uses a Maxim MAX96718 and MAX96722; the Ethernet chip is an NXP JA1101A; the power management chip includes a Texas Instruments TPS6594, two Maxim MAX20087, and a Texas Instruments LM5143; the CAN bus driver chip is an NXP TJA1043. The following will explain the characteristics and functions of each chip in detail.

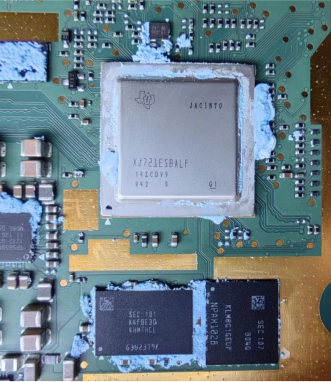

4.1, SOC Chip

4.1.1, Introduction to DRV829

The DRV829 processor is based on the evolving Jacinto™ 7 architecture, aimed at ADAS and autonomous vehicle (AV) applications, built on TI’s extensive market knowledge accumulated over more than a decade in the ADAS processor market. In an architecture aimed at meeting functional safety standards, the unique combination of high-performance computing, deep learning engines, and dedicated signal and image processing accelerators makes the DRA829 device very suitable for various industrial applications, such as robotics, machine vision, radar, etc. The DRA829 provides high-performance computing for traditional and deep learning algorithms with industry-leading power/performance ratios, ensuring scalability and lower costs for advanced automotive platforms supporting centralized ECUs or multiple sensor modes in standalone sensors. Key cores include next-generation DSPs with scalar and vector cores, dedicated deep learning and traditional algorithm accelerators, the latest Arm and GPU processors for general computing, integrated next-generation imaging subsystems (ISP), video codecs, Ethernet hubs, and isolated MCU islands. All of these are protected by automotive-grade safety hardware accelerators.

4.1.2, Role of DRA829 in the Domain Controller

①, Perception Processing: The DRA829 can achieve real-time processing and fusion of multi-sensor data through integrated high-performance processors and digital signal processors (DSPs), used for functions such as object detection, object recognition, lane departure warning, and pedestrian recognition. It can process data from various sensors such as cameras, millimeter-wave radars, and ultrasonic sensors.

②, Data Transmission and Storage: The DRA829 has high-speed data transmission and storage capabilities, supporting multi-channel high-speed data interfaces such as Ethernet, USB, and CAN for real-time reception and transmission of sensor data. Additionally, the TDA4 also supports high-capacity storage devices, capable of storing a large amount of vehicle data for offline analysis and post-processing.

③, Decision Making and Planning: The DRA829 is equipped with high-performance AI processors for real-time decision-making and planning. It can predict and analyze the environment through deep learning models, generating safe and efficient path planning and dynamic decisions for the navigation and driving control of autonomous vehicles.

④, Safety Assurance: The DRA829 features multiple safety mechanisms, including hardware encryption, cellular communication security, and system integrity checks. It ensures the secure transmission and storage of sensitive data, enhancing the safety performance of autonomous driving systems.

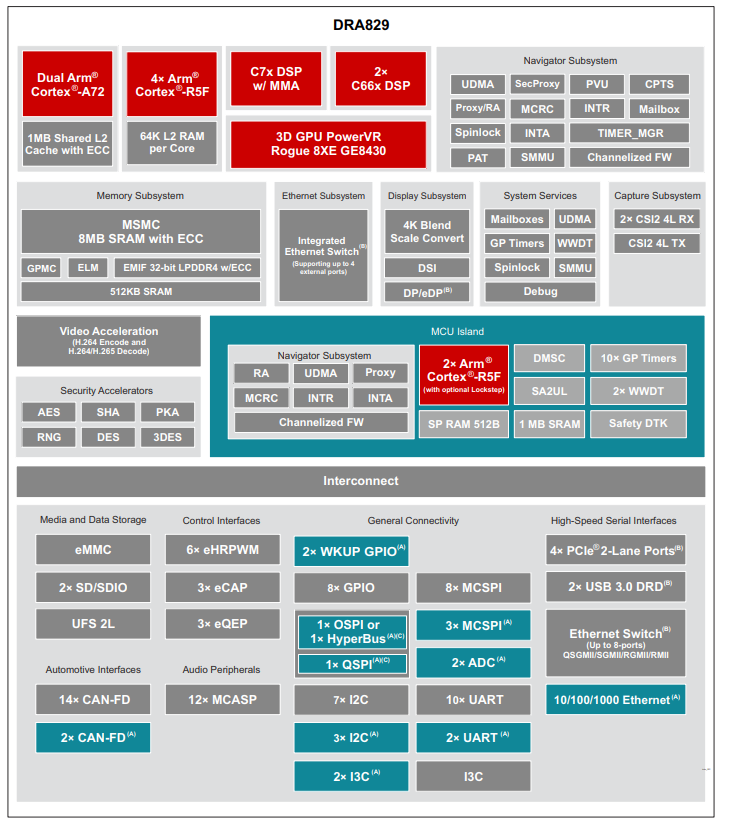

4.1.3, Features

|

Processor Cores: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Block Diagram

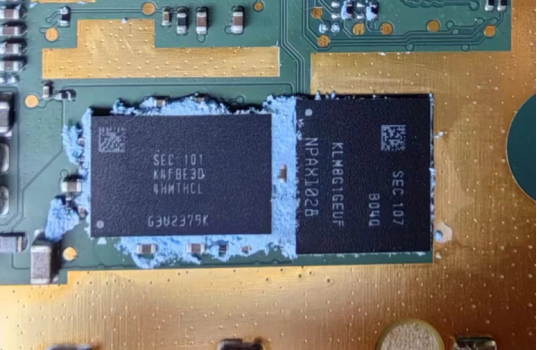

4.2, Storage Chips

4.2.1, LDDR4-K4FBE3D4HM

K4FBE3D4HM Introduction

Storage Capacity: 32GB

Read/Write Speed: 4266 Mbps

Function:

①, LPDDR4 provides fast storage access speed and high bandwidth. Autonomous driving systems require real-time perception and analysis of environmental data around the vehicle, including images, radar data, etc. The high-speed read/write capability of LPDDR4 can accelerate the transmission speed of data between memory and processor, thereby improving system response speed and real-time performance.

②, LPDDR4 has low power consumption characteristics. Autonomous driving systems need to operate stably for long periods and usually work in embedded environments, where heat dissipation and power consumption control are essential considerations. The low-power design of LPDDR4 can reduce the energy consumption of the controller, extend battery life, and reduce heat dissipation issues, improving system stability and reliability.

③, LPDDR4 supports high-density storage and large-capacity memory. Autonomous driving systems need to store and manage large amounts of map data, vehicle status data, historical control information, etc. The high-density storage capability of LPDDR4 can meet these needs and ensure high-speed read/write and processing performance of the data.

Features

|

• Double data rate architecture; two data transfers per clock cycle • Bidirectional data strobe (DQS_t, DQS_c) sent/received with the data captured by the receiver • Differential clock input (CK_t and CK_c) • Differential data strobe (DQS_t and DQS_c) • Command and address on the positive CK edge; the two edges of DQS reference the data and data mask • Each module consists of 2 channels • Each channel has 8 internal banks • DMI pins: DBI (data bus inversion) during normal write and read operations, DM for masking write data when DBI is off -DBI on masks write count# of DQ 1 • Burst length: 16, 32 (OTF) • Burst type: continuous • Read/write latency: see table 64 LPDDR4 AC timing table • Automatic precharge option for each burst access • Configurable drive strength • Refresh and self-refresh modes • Partial array self-refresh and temperature-compensated self-refresh • Write leveling • CA calibration • Internal VREF and VREF training • FIFO-based write/read training • MPC (multi-purpose command) • LVSTL (low-voltage swing terminated logic) IO • VDD1/VDD2/VDDQ: 1.8V/1.1V/1.1V • VSSQ terminal • No DLL: CK to DQS unsynchronized • Edge-aligned data output, data input center-aligned write training • Refresh rate: 3.9us |

4.2.2, eMMC KLM8G1GETF

KLM8G1GETF-B041 Introduction

Storage Capacity: 64GB

Function:

①, This EMMC chip is one of the main media for storing the firmware and operating system of the controller. The firmware and operating system of the main controller are burned into the EMMC chip to be loaded from the chip at startup. This ensures the stability and consistency of the system and enables the controller to boot quickly.

②, The EMMC chip is also responsible for storing and managing the running code within the controller. Autonomous driving controllers need to process a large amount of data and complex algorithms, and the running programs require high real-time performance and performance. The EMMC chip provides fast data read and write speeds, effectively executing the running code of the controller and ensuring its normal operation.

③, The EMMC chip is also used to store and manage data within the controller. Autonomous driving systems need to record and store various sensor data, map data, and other important data in real time to support real-time decision-making and improve algorithms. The EMMC chip provides large capacity storage space and high-speed data read/write capabilities, meeting the data storage requirements of autonomous driving controllers.

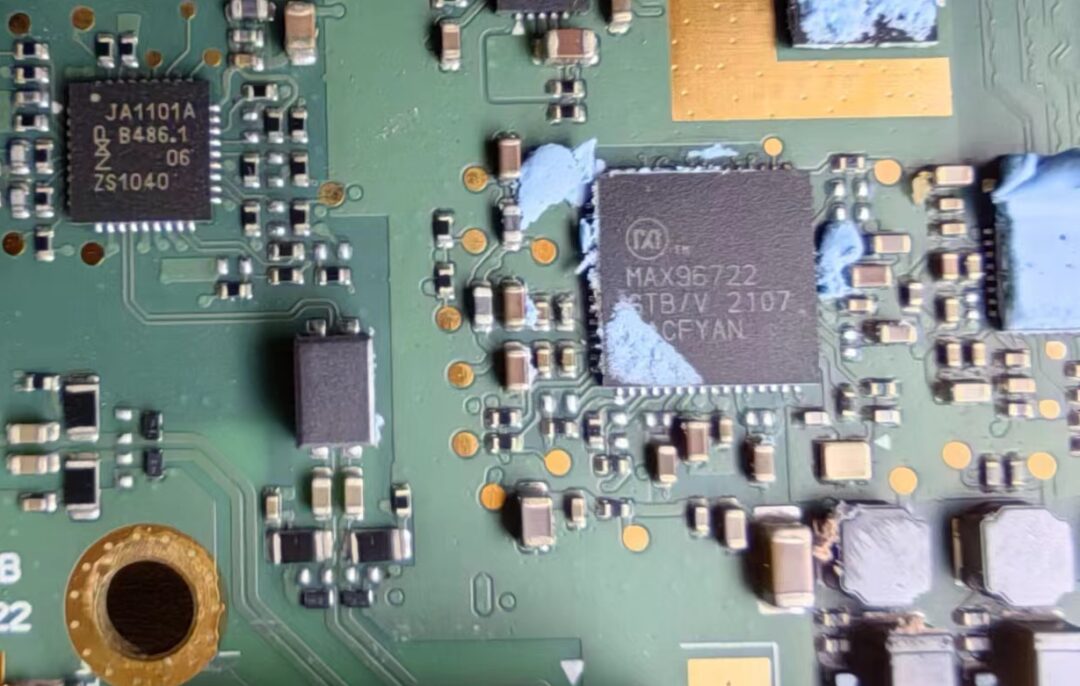

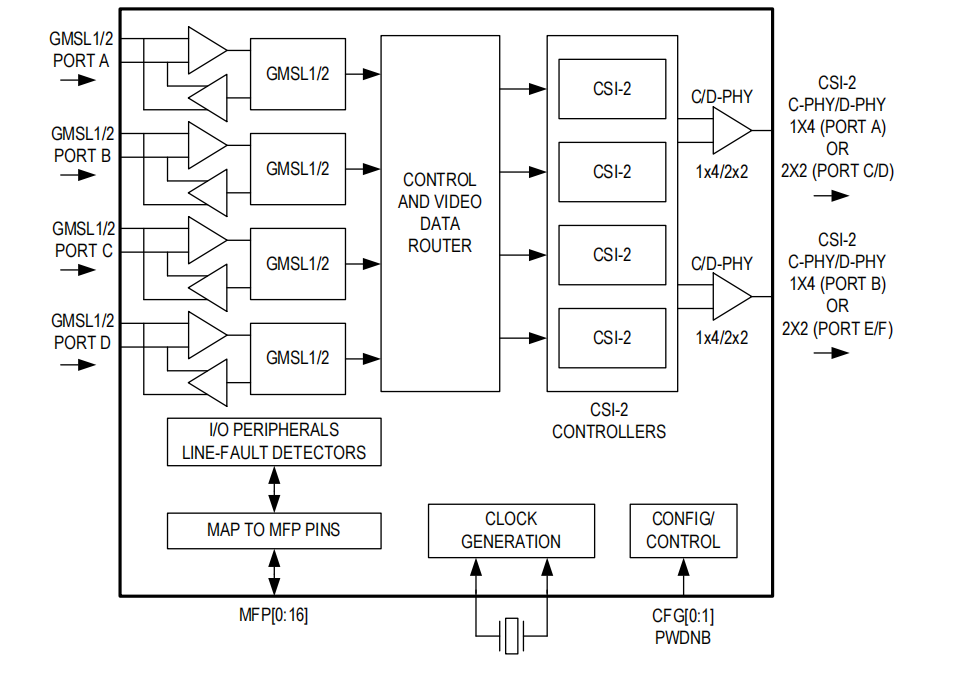

4.3, Serializer/Deserializer Chips

4.3.1, Maxim MAX96722

Introduction

MAX96722 deserializer converts GMSL2 or GMSL1 serial input into MIPI CSI-2 D-PHY or C-PHY format output. This device allows simultaneous transmission of bidirectional control channel data while performing forward video transmission on each link. MAX96722 can accommodate up to four remote sensors using industry-standard coaxial cables or STP interconnects. Each GMSL2 serial link operates at a fixed rate of 3Gbps in the forward direction and 187.5Mbps in the reverse direction. In GMSL1 mode, MAX96722 can pair with first-generation 3.12Gbps or 1.5Gbps GMSL1 serializers or operate in GMSL1 with GMSL2 serializers at up to 3.12Gbps.

MAX96722 supports the aggregation and replication of video data, allowing streams from multiple remote sensors to be combined and routed to one or more available CSI-2 outputs. Data can also be routed based on virtual channel IDs, allowing multiple streams from a single GMSL input to be independently routed to different CSI-2 outputs. Alternatively, frame-level cascading can be used to synchronize and combine data from multiple sensors into a single CSI-2 stream within a composite superframe. The CSI-2 interface supports 2×4 channel and 4×2 channel configurations using C-PHY or D-PHY.

Features

|

MIPI CSI-2 v1.3 output configurable to 2×4 channels, 1×4 lane + 2×2 lane, or 4×2 lane |

• Optional D-PHY v1.2, 80Mbps-2.5Gbps/Lane or C-PHY v1.0, 182Mbps-5.7Gbps-Lane • 16/32 channel virtual channel support (D/C-PHY) • Flexible aggregation and routing of incoming data via CSI-2 VC or frame-level cascading • Data can be copied and routed to any CSI port • Supports RAW8/10/12/16/20, RGB565/666/ 888, YUV422 8-/10-bit formats • Dual-pixel mode improves transmission efficiency • CSI-2 lane reallocation and polarity inversion • MIPI/GMSL video PRBS generator and checker • Checkerboard/color gradient pattern generator • Raw CSI-2 PRBS generator • Independently configure all video paths and GMSL/CSI-2 ports |

|

Independently configurable four GMSL inputs GMSL1/2 operations, link speeds, and video formats |

• Mixed GMSL1/GMSL2 support • Backward compatible with GMSL1 serializers • GMSL1 forward link speed up to 3.12Gbps • 3Gbps GMSL2 link speed (forward) and 187.5Mbps (reverse) • Synchronous and simultaneous support of asynchronous cameras • Precise synchronization of multiple serializers for large camera systems • GMSL PRBS generator/checker for link testing • Eye monitor for continuous diagnostics • Adaptive equalization, up to 15 meters of coaxial with multiple vertical connectors • Compatible with 50Ω coaxial cables or 100Ω STP |

|

Compatible with ASIL-B (GMSL2) |

• Video watermark insertion and detection • 16-bit CRC protection for control channel data Retransmission after error detection • Optional 32-bit CRC protection for video line data • ECC protection for video data memory • CRC protection for CSI-2 data streams |

|

Concurrent control channels for device configuration and communication with remote peripherals |

• 3 I2C/UART, 2 SPI, 17 GPIO • Eight hardware selectable device addresses |

|

Programmable spread spectrum reduces EMI |

|

|

Line fault monitoring for GMSL links |

|

|

64-lead 9 x 9mm TQFN with exposed pads |

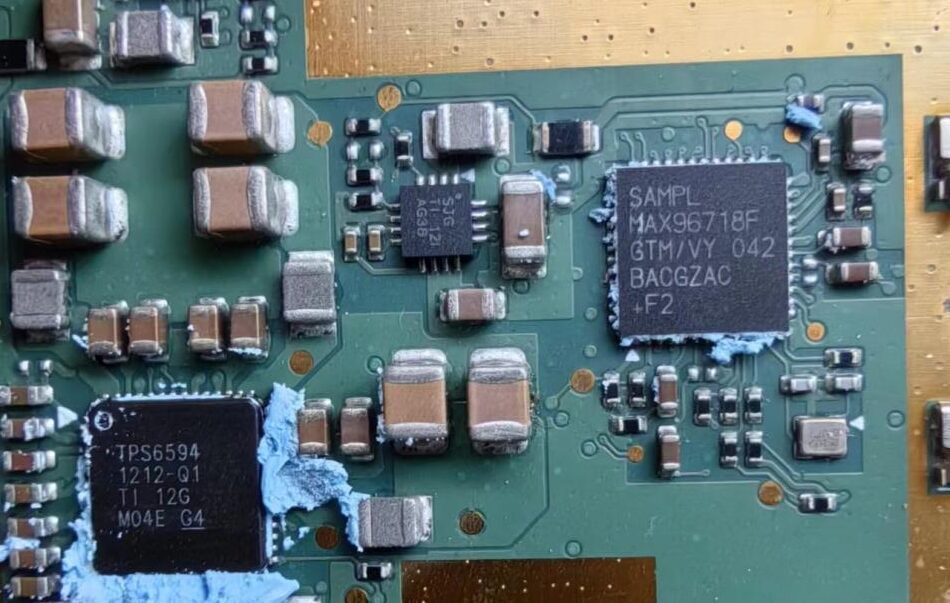

4.3.2, Maxim MAX96718

Similar performance to MAX96722, detailed chip manual not found!

4.4, Ethernet/Switch Chip

TJA1101 Introduction

TJA1101 is an Ethernet PHY compliant with the 100BASE-T1 standard, optimized for automotive use cases such as gateways, IP camera links, driver assistance systems, and backbone networks. This device provides 100Mbit/s transmission and reception capabilities over two unshielded twisted pairs, supporting cable lengths of at least 15m.

TJA1101 is designed for automotive ruggedness and ISO 26262, ASIL A compliance, while minimizing power consumption and system costs. Due to compliance with ASIL-A standards, sufficient safety features have been implemented to ensure compliance with ASIL requirements at the system level.

Features

|

Functional Overview |

Features |

|

General |

• 100BASE-T1 PHY • MII and RMII compatible interfaces for the bus • Compact HVQFN 36-lead package (6×6 mm) for PCB space-constrained applications • ISO 26262, compliant with ASIL-A |

|

Optimized for Automotive Use Cases |

• Transmitter optimized for capacitive coupling with unshielded twisted pairs • Adaptive receiver equalizer optimized for automotive cable lengths of at least 15 meters • Enhanced integrated PAM-3 pulse shaping for low RF emissions • EMC optimized output driver strength for MII and RMII • MDI pins protection against ESD up to ±6 kV HBM and ±8 kV IEC61000-4-2 • MDI pins protection against transients in automotive environments • MDI pins do not require external filtering or ESD protection • Automotive-grade temperature range of -40°C to +125°C • AEC-Q100 qualified automotive product |

|

Low Power Mode |

• Dedicated PHY enable/disable input pin to minimize power consumption • Output suppressed by voltage regulator control • Compliant with the Open Alliance wake-up concept (global wake-up support) – Strong remote wake-up detection via bus – PHY level wake-up forwarding • Compliant with the Open Alliance sleep concept • Local wake-up pin • Wake-up via SMI access |

|

Diagnostic Functions |

• Real-time monitoring of link stability and transmission data quality • Cable fault diagnostics (short circuit and open circuit) • No-gap power undervoltage detection with fault mute behavior • Internal, external, and remote loopback modes for diagnostics |

|

Others |

• Reverse MII mode for back-to-back connection of two PHYs • On-chip voltage regulator for single supply operation of 3.3 V • Optional 1.8 V external supply for digital core • On-chip termination resistors for differential cable pairs • Supports up to 16 kB jumbo frames |

Block Diagram

TJA1101’s block diagram is illustrated below. The 100BASE-T1 section contains functional blocks specified in the 100BASE-T-1 standard, which constitute the physical coding sublayer (PCS) and physical medium attachment (PMA) layer of the signal transmission and reception paths. The MII/RMII interface (including the serial management interface (SMI)) complies with IEEE802.3 Section 22.

Additional blocks have been defined for mode control, register configuration, interrupt control, system configuration, reset control, local wake-up, remote wake-up, undervoltage detection, and configuration control.

Many power-related functional blocks have been defined: an internal 1.8V regulator for the digital core, a very low power (VLP) supply for sleep mode, reset circuits, power monitoring, and inhibit control.

The clock signal required for the operation of the PHY is generated in the PLL block, derived from an external crystal or oscillator input signal.

Pin strapping allows many default PHY settings (e.g., master or slave configuration) to be hardware-configured at power-up.

4.5, Power Management Chip

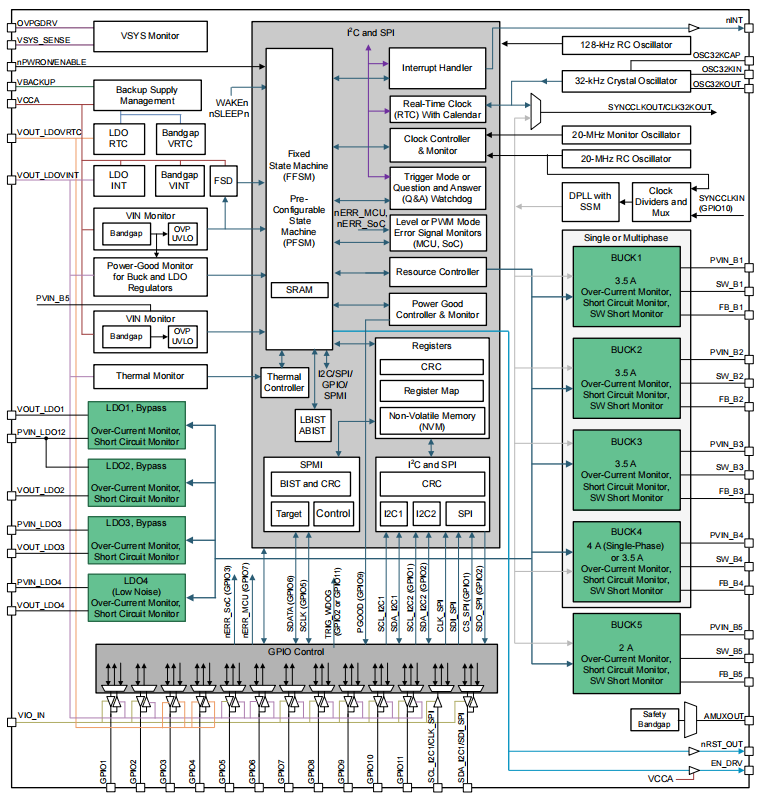

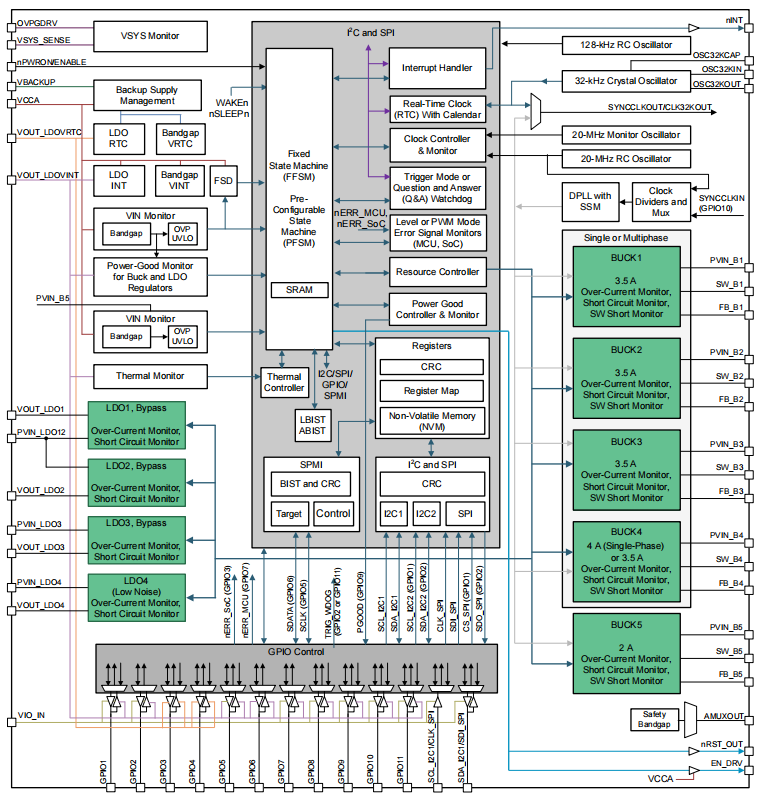

4.5.1, TPS6594

TPS6594-Q1 features 5 buck converters and 4 LDOs suitable for automotive safety-related applications.

Features

|

Features |

Functions |

|

Meets automotive application requirements,with AEC-Q100 compliant features |

– Device input supply voltage range of 3V to 5.5V – Device temperature grade1:–40°C to +125°C Operational temperature range Device HBM classification grade 2 – Device CDM classification grade C4A |

|

Complies with functional safety standards

|

– Developed for functional safety applications – Helps to ensure ISO 26262 system design meets ASIL-D documentation – Helps to ensure IEC 61508 system design meets SIL-3 documentation – System functions meet ASIL-D – Hardware integrity meets ASIL-D – Input supply voltage monitoring and overvoltage protection – Undervoltage/overvoltage monitoring and overcurrent monitoring on all output power rails– 具有可选触发/Q&A 模式的看门狗 – 具有可选级别/PWM 模式的两个错误信号监测 (ESM) – 具有高温警告和热关断功能的温度监测 – 对内部配置寄存器和非易失性存储器 (NVM) 的 位完整性 (CRC) 错误检测 |

|

Low Power Consumption

|

– 2μA typical shutdown current – Typical value of 7μA only in backup power mode – Typical value of 20μA in low-power standby mode

|

|

Five switch-mode buck regulators:

|

– Output voltage range: 0.3V to 3.34V(voltage step of 5mV、10mV or 20mV) – Output current:其中一个是 4A,另外三个是 3.5A, 还有一个是 2A – Four buck regulators’ flexible multi-phase functionality:single rail output current of up to 14A – Short circuit and overcurrent protection – Internal soft-start limits inrush current – Switching frequency of 2.2MHz/4.4MHz – Can be synchronized with external clock input

|

|

Three low-dropout (LDO) linear regulators with configurable bypass mode

|

– Output voltage range in linear regulator mode: 0.6V to 3.3V (voltage step of 50mV) – Bypass mode output voltage range:1.7V to 3.3V – 500 mA output current,具有短路和过流保护 |

|

One low-noise low-dropout (LDO) linear regulator

|

– Output voltage range: 1.2V to 3.3V(voltage step of 25mV) – 300mA output current,具有短路和过流保护 |

|

Configurable power sequencing control in non-volatile memory (NVM):

|

– Configurable power-up and power-down sequences between power states – Digital output signals can be included in the power sequence – Digital input signals can trigger power sequence transitions – Configurable safety-related fault handling |

|

• 32kHz crystal oscillator, buffered output of 32kHz clock output • Real-time clock (RTC) with alarm and periodic wake-up mechanism • One SPI or two I2C control interfaces,and the second I2C interface is dedicated to Q&A watchdog communication |

Functional Block Diagram

4.5.2, MAX20087

MAX20087 Introduction

Dual/Four-channel camera power protector; the industry’s only ASIL-grade camera protector, providing diagnostics via I2C. Maxim has four camera power diagnostic chips: MAX20086, MAX20087, MAX20088, MAX20089.

MAX20086–MAX20089 dual/four camera power detector IC provides up to 600mA load current for each of the four output channels. Each output is individually protected against battery short circuit, ground short circuit, and overcurrent situations. The IC operates at 3V to 5.5V supply and 3V to 15V camera supply. At 300mA, the input-output voltage drop is only 110mV (typical).

The IC provides enable input and I2C interface to read the diagnostic status of the device. The onboard ADC can read the current through each switch. Versions compliant with ASIL B and ASIL D support reading an additional seven diagnostic measurements via ADC, ensuring high fault coverage.

MAX20086–MAX20089 each include over-temperature shutdown and overcurrent limit on each output channel. All devices are designed for an operating temperature range of -40°C to +125°C.

Features

|

Features |

Functions |

|

Small solution size

|

Up to 4 600mA protection switches 3V to 15V input supply voltage 3V to 5.5V device operating supply 26V battery short circuit isolation Adjustable limit current value(100mA to 600mA) Parallel multi-channel for higher current Optional I2C address Small size(4mm × 4mm), 20-lead SWTQFN and WETQFN packages |

|

High Precision

|

±8% limit current accuracy 0.5ms soft-start time 0.25ms soft shutdown time 0.3µA shutdown current 110mV voltage drop @ 300mA |

|

Designed for safety applications |

Compatible with ASIL B/D Short circuit diagnostics VBAT/GND Output overvoltage/undervoltage diagnostics Input overvoltage/undervoltage diagnostics Read 8-bit current, output voltage, and power supply readings for each channel via I2C Automatic retry on faults |

|

AEC-Q100 certified, -40°C to +125°C operating temperature range |

4.5.2, MAX20087

|

Chip |

Price |

|

DRA829 |

700 |

|

Samsung eMMC5.1 KLM8G1GEUF |

18 |

|

Samsung LPDDR4 K4FBE3D4HM |

100 |

|

Maxim MAX96718F |

100 |

|

Maxim MAX96722 |

110 |

|

NXP 100M PHY transceiver JA1101A |

18*2 |

|

Texas Instruments TPS6594 |

80 |

|

Maxim MAX20087A |

20*2 |

|

NXP TJA1043 |

15*4 |

|

Texas Instruments LM5143 |

50 |

This column will continuously disassemble the latest controller schemes from both domestic and international sources, including but not limited to intelligent driving, cockpit, central computing, body domain control, chassis domain control, and power domain control.

To continuously launch popular controller disassemblies, this column will adopt a

crowdfunding

model to purchase relevant domain controller samples. Friends who participate in the crowdfunding can place orders for controllers they are interested in and receive more detailed disassembly reports.

If you would like to participate in the crowdfunding disassembly, please contact the editor: btigh

teast.

Upcoming includes:

Intelligent Driving Domain Controller

:Great

Xinjiang vehicle domain control, Yangwang U8 domain control, Ideal L8 domain control

Cabin Domain Controller:Xiaomi SU7, Mercedes-Benz E300, Zeekr 007, Leapmotor Four-leaf Clover

END