The Intelligent Gorilla and Zhixdong will jointly hold the 2024 China Generative AI Conference in Beijing on April 18-19. Over 40 guests, including Wang Changhu, founder of Aishi Technology, Zhou Zhifeng, partner at Qiming Venture Partners, You Yang, founder of Lucheng Technology, and others, have confirmed to deliver speeches and presentations. Registration is welcome.

The SAIC Roewe third-generation RX5 is the first fuel vehicle in China equipped with the NGP intelligent navigation assist driving function. The NGP intelligent driving function was launched in early August 2022. Today, we will decode the design scheme of the domain controller for the SAIC Roewe RX5 NGP intelligent version.

Introduction to Roewe RX5 Intelligent Driving Solution

To enhance user experience with advanced intelligent assisted driving functions, SAIC Roewe has put considerable thought into the vehicle’s perception sensor scheme. The all-new third-generation Roewe RX5 NGP intelligent version adopts a multi-dimensional perception fusion scheme, equipped with 1 8-megapixel 120° front-view camera, 5 2-megapixel 100° surround view cameras, 4 360° surround cameras, 3 millimeter-wave radars, 12 ultrasonic radars, and a high-precision positioning module, totaling 28 sensors, providing comprehensive coverage of the vehicle’s surrounding environment, allowing for a longer detection distance, a wider detection range, and more precise identification of various objects.

To realize the fusion of multiple sensors and implement more complex algorithms, the SAIC Roewe NGP intelligent version domain controller is provided by Hongjing Intelligent Driving. This intelligent driving domain controller uses 3 Horizon Journey 3 high-performance domestic AI chips, which utilize Horizon’s self-developed Bernoulli 2.0 BPU® architecture to implement various intelligent driving algorithm modules for environmental perception, map positioning, and fusion planning, achieving 360° surround visual perception coverage. Additionally, this system supports efficient intelligent driving planning and decision-making algorithms, possesses deep learning capabilities, and provides iterative updates.

Roewe RX5 Intelligent Driving Domain Controller Scheme

1. Appearance Structure of the Intelligent Driving Domain Controller

The SAIC Roewe RX5 NGP intelligent version domain controller is designed by Hongjing Intelligent Driving, with a metal machined shell featuring numerous heat dissipation grooves. This domain controller employs a natural heat dissipation method, with thermal grease applied to the surface of the main chip, allowing direct contact with a metal post that extends into the metal shell, thereby dissipating heat to the outside through the shell connected to the metal post. The external heat dissipation grooves of the domain controller shell increase the contact area with air, further facilitating heat dissipation.

Front view of the autonomous driving domain controller shell

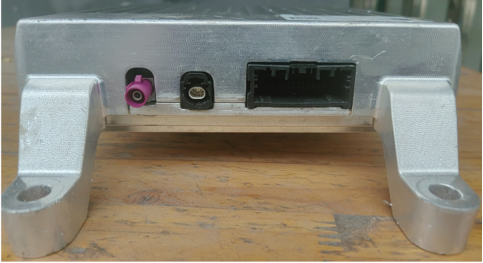

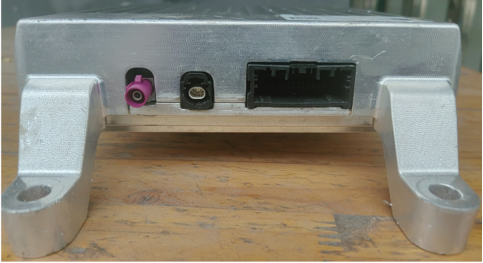

Back view of the autonomous driving domain controller shell

2. Interfaces of the Intelligent Driving Domain Controller

The wired terminal of this domain controller is distributed on both sides; the right side mainly includes power, IO, communication interfaces, GPS antenna, etc.; the left side mainly distributes the wiring terminals for surround, side, and front views.

Wired terminal diagram of the autonomous driving domain controller 1

Wired terminal diagram of the autonomous driving domain controller 2

3. PCB Board of the Intelligent Driving Domain Controller

Wired terminal diagram of the autonomous driving domain controller 2

3. PCB Board of the Intelligent Driving Domain Controller

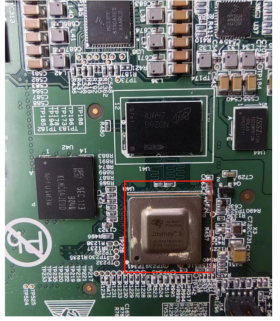

Front view of the autonomous driving domain controller PCB

Front view of the autonomous driving domain controller PCB

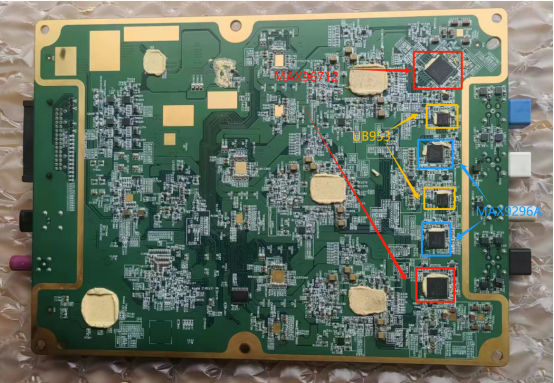

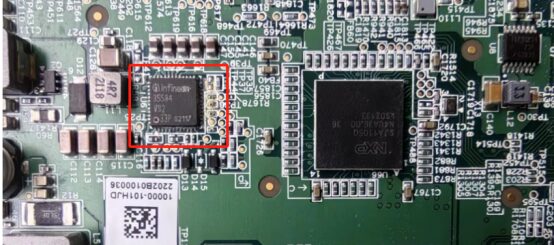

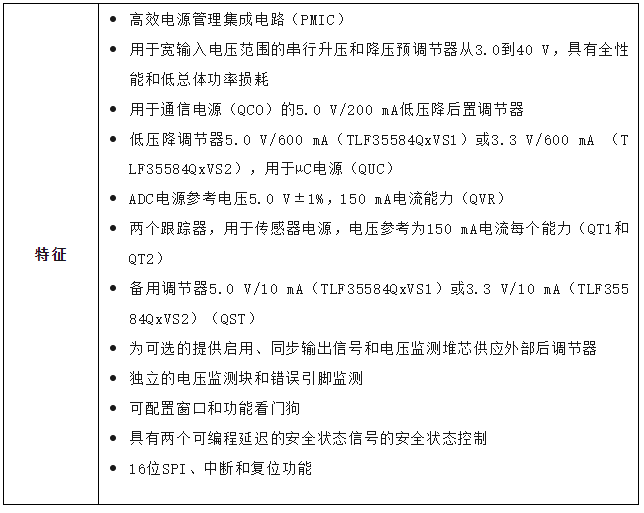

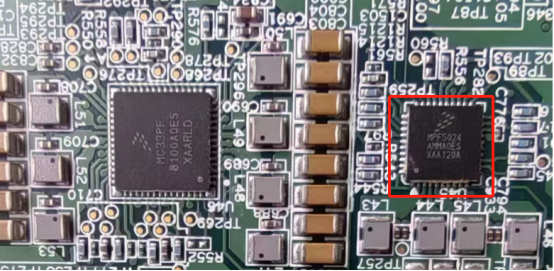

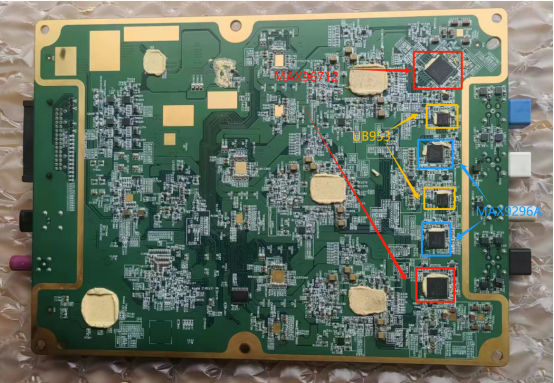

Annotated front view of the autonomous driving domain controller PCB

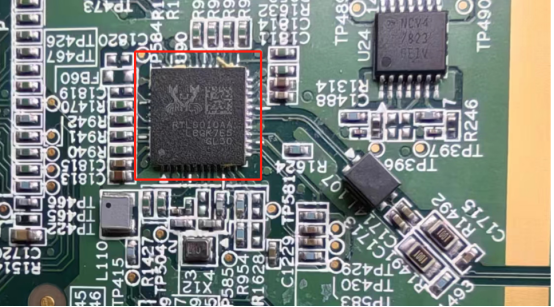

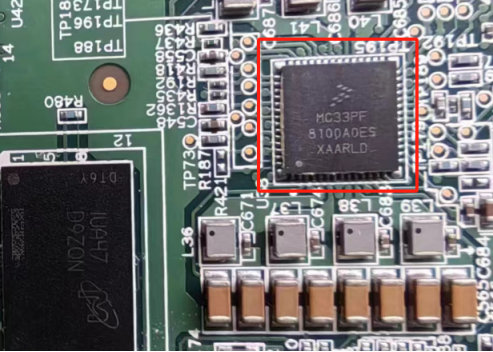

In the image, the numbered components are: 1-Horizon J3, 2-Micron DDR4 2G, 3-Samsung eMMC 64G, 4-American Chipone Nor flash, 5-Infineon AURIX TC397, 6-Ublox ZED F9K, 7-NXP switch SJA1105Q, 8-Power chip MC33PF 8100A0ES, 9-Power chip Infineon 355584, 10-PHY chip RTL9010AA, 12-Power management chip MPF5024AMMA0ES.

Annotated back view of the autonomous driving domain controller PCB

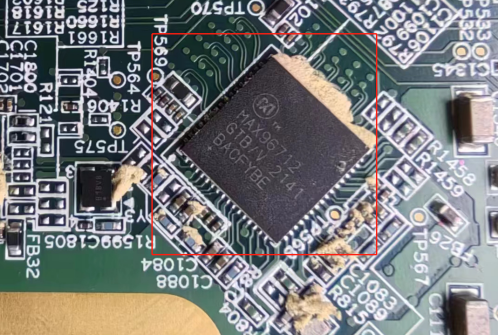

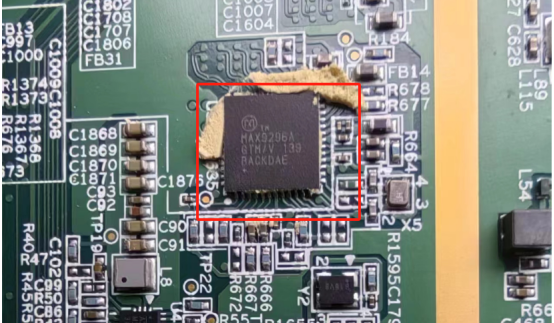

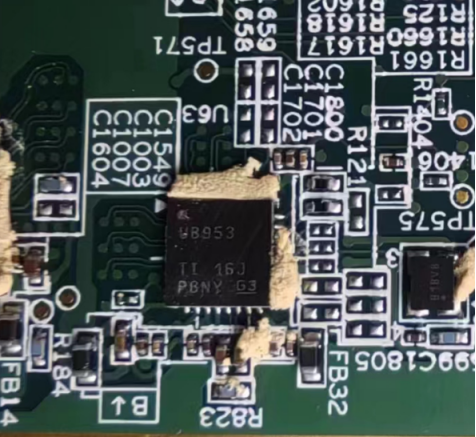

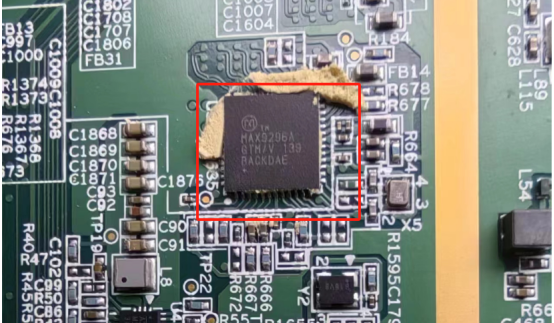

In the image, the numbered components are: Maxim GMSL MAX96712, Texas Instruments FDLink UB953, Maxim GMSL MAX9296A.

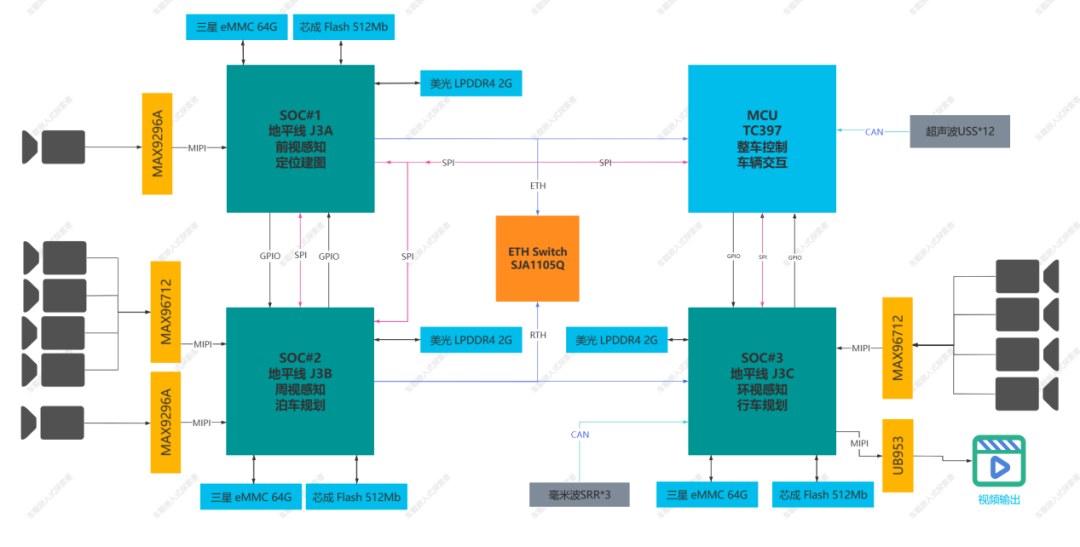

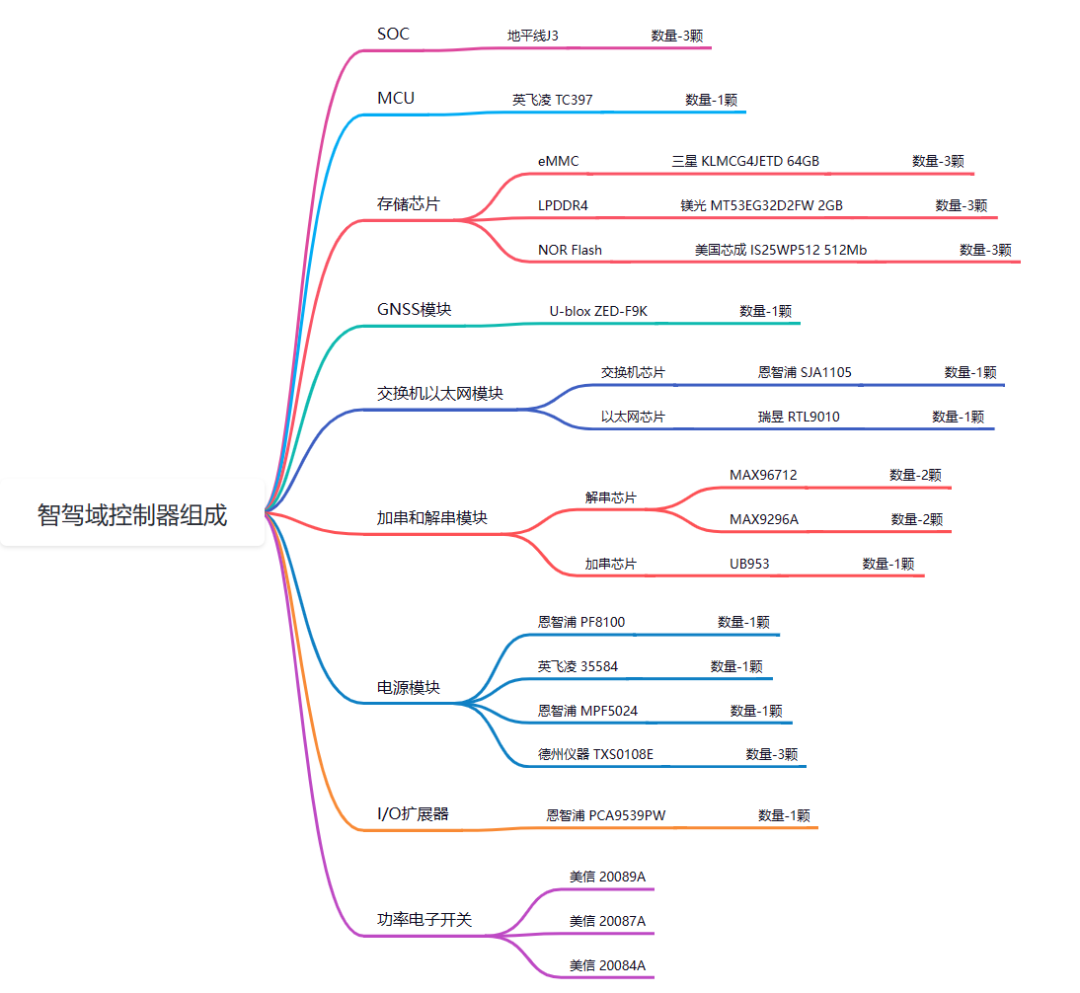

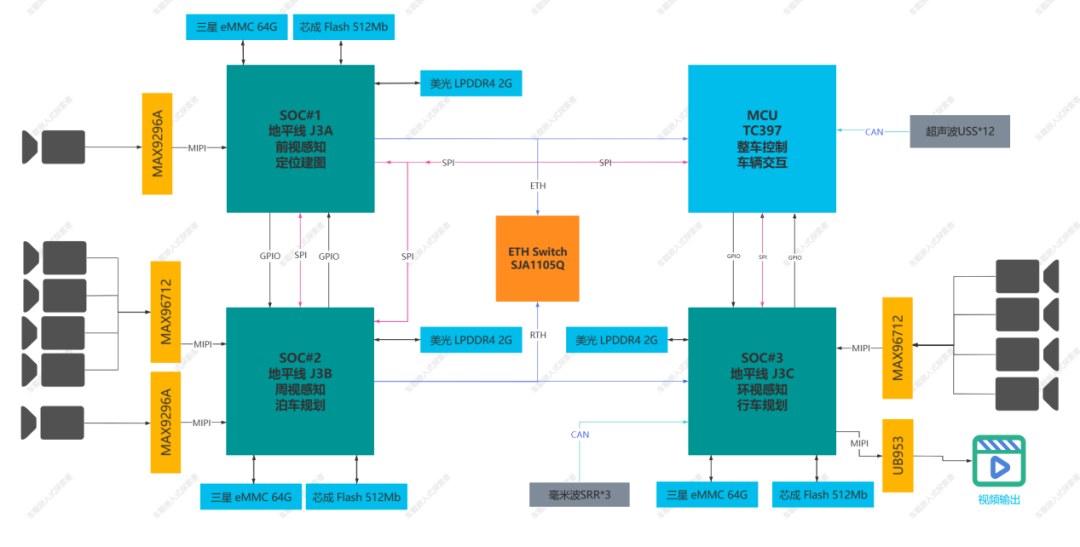

4. Domain Controller System

Autonomous driving domain control system block diagram

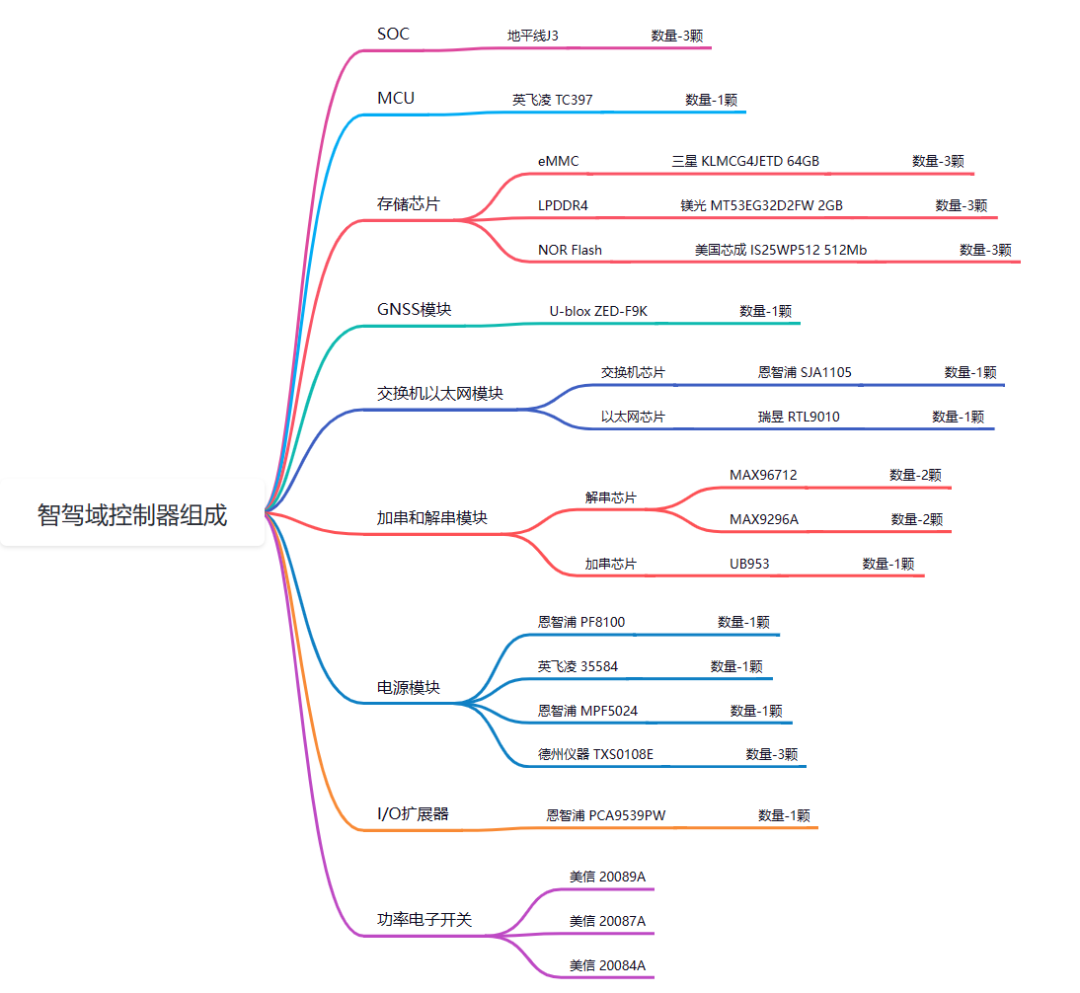

Composition diagram of the autonomous driving domain control system

SOC, or System on Chip, is a large integrated circuit that integrates multiple functional modules such as processor cores, memory controllers, and peripheral controllers. In the autonomous driving domain controller, the SOC chip is responsible for processing sensor data, performing real-time image processing, and executing computer vision algorithms. Common SOC chip models include Nvidia Drive Orin, Intel’s Mobileye EyeQ series, Qualcomm’s Snapdragon Automotive Platform series, and Horizon Journey series.

The SAIC Roewe RX5 uses 3 Horizon J3 chips.

5.1 Functions of the 3 Horizon J3 Chips

|

|

|

|

|

Responsible for perception from the front-view camera and GNSS module’s positioning and mapping functions.

|

|

|

Responsible for perception from the surround-view camera, rear camera, and parking planning functions.

|

|

|

Responsible for perception from the four surround cameras and driving planning functions.

|

5.2 Overview of Horizon Journey 3 Chip

The Horizon Journey 3 is a second-generation in-vehicle intelligent chip under Horizon; it is based on Horizon’s self-developed BPU®️2.0 architecture and complies with AEC-Q100. The Journey 3 not only supports deep learning-based image detection, classification, pixel-level segmentation, and other functions; it also supports efficient encoding of H.264 and H.265 video formats, making it an ideal platform for implementing multi-channel complex computing tasks and multi-channel digital video recording, such as advanced driver assistance systems (ADAS) and automatic parking assistance (APA).

5.3 Features of Horizon Journey 3

|

|

· Manufactured using TSMC’s 16nm FFC process;

· Uses FCBGA484 packaging, with a pin pitch of 0.65mm and chip size of 15mmx15mm;

· Complies with automotive AEC-Q100 Grade 2 standards (operating temperature: -40~105 degrees Celsius)

|

|

|

· Uses 4 Arm Cortex A53 cores, with 32KB/32KB L1 I/D core 512KB Level 2 cache;

· Maximum operating frequency: 1.2GHz;

· Supports Dynamic Frequency Scaling (DFS);

|

|

|

· Composed of dual-core Bernoulli architecture BPU0 and BPU1, with computing power of 5TOPS;

· Maximum operating frequency: 950MHz;

· Supports Dynamic Frequency Scaling (DFS);

|

|

|

· Supports x32 external DDR4/LPDDR4/LPDDR4X DRAM, maximum capacity of 4GB;

· Maximum speed of supported DDR4 can reach DDR4-3200 MT/s;

· Maximum speed of supported LPDDR4/LPDDR4X can reach 3200MT/s;

|

|

Network Interface Characteristics

|

· Supports one Gigabit network interface;

· External Ethernet PHY supports RMII and RGMII protocols;

· Supports Time-Sensitive Networking (TSN) and Audio Video (AV) traffic;

|

|

|

· Uses BIF-SPI slave interface, with maximum transmission rate of AP SPI master device up to 66 MHz;

· Suitable for AP eMMC host transmission mode, up to 8 lines using BIF-SD device interface HS200 mode (maximum 192MB/s). The application processor (AP) uses BIF-SPI and BIF-SD host interfaces to access J3’s DDR, SRAM, and module registers for data exchange and control;

· Supports USB3.0 host/device dual-role high-speed interface.

|

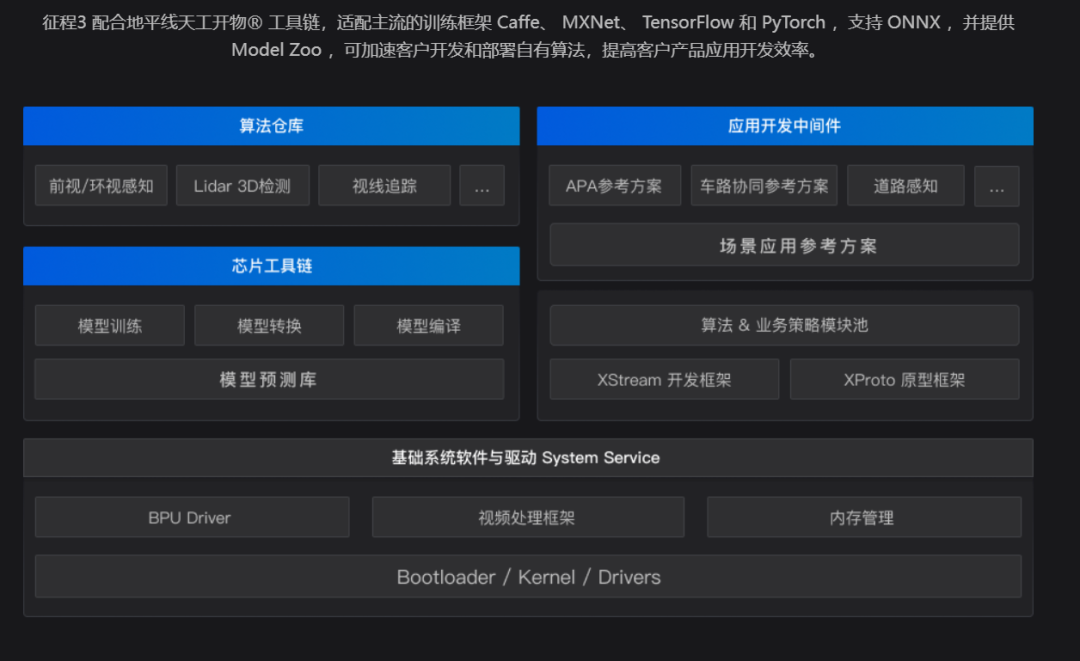

5.4 Toolchain for Horizon Journey 3

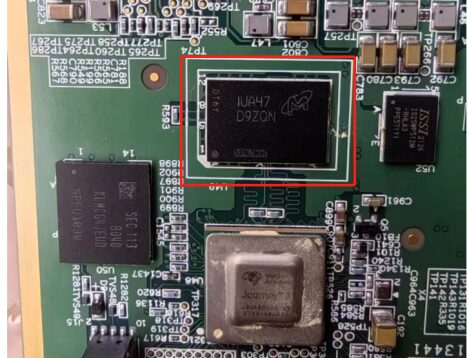

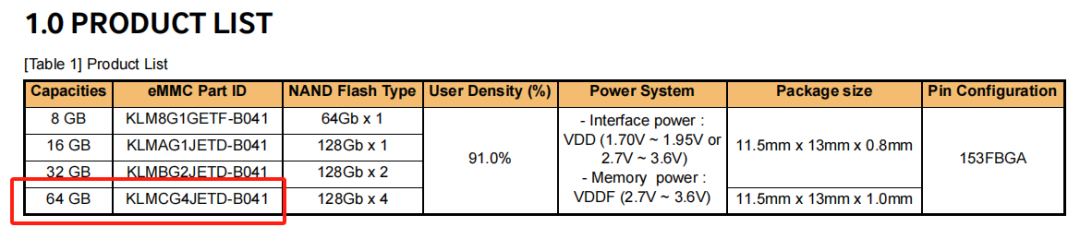

Common storage modules used in intelligent driving domain controllers include eMMC and DDR4; they play an important role in storing data within the autonomous driving domain controller. The eMMC chip serves as a flash storage device, responsible for storing the system’s operating system, algorithms, and data. DDR4 chips are high-speed memory chips that are responsible for caching and running algorithms. Common eMMC chip models include Samsung’s KLM and SK Hynix’s eMMC, while common DDR4 chip models include Micron’s Crucial and Kingston’s HyperX.

Micron DDR4 2GB, specific model: MT53E1G32D2FW-046

Model: KLMCG4JETD-B041, Samsung eMMC 64G

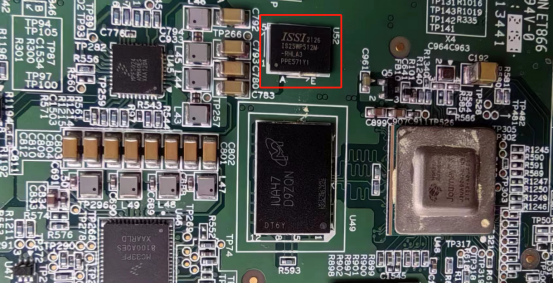

American Chipone IS25WP512M-RHLA3 512Mb

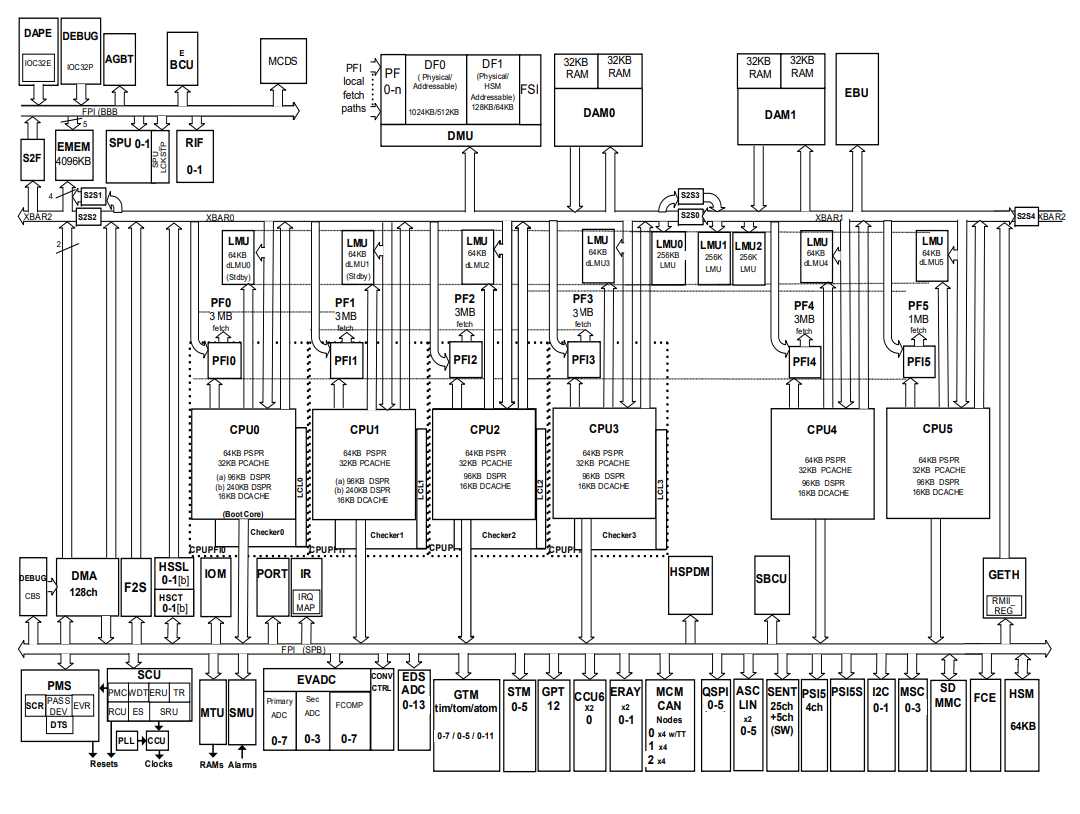

The MCU chip plays an important role in the autonomous driving domain controller. MCU, or Microcontroller Unit, is a microcomputer that integrates functions such as processor core, memory, and input/output interfaces. In the autonomous driving domain controller, the MCU chip is responsible for real-time calculations, data acquisition, and control tasks. Common MCU chip models include NXP’s S32K series, Infineon’s AURIX TC3X7 series, and Renesas’ RH850 series. MCU chips can communicate with SOC chips via CAN bus, Ethernet, and SPI.

The TC397 chip in this domain controller is responsible for overall vehicle control and data interaction.

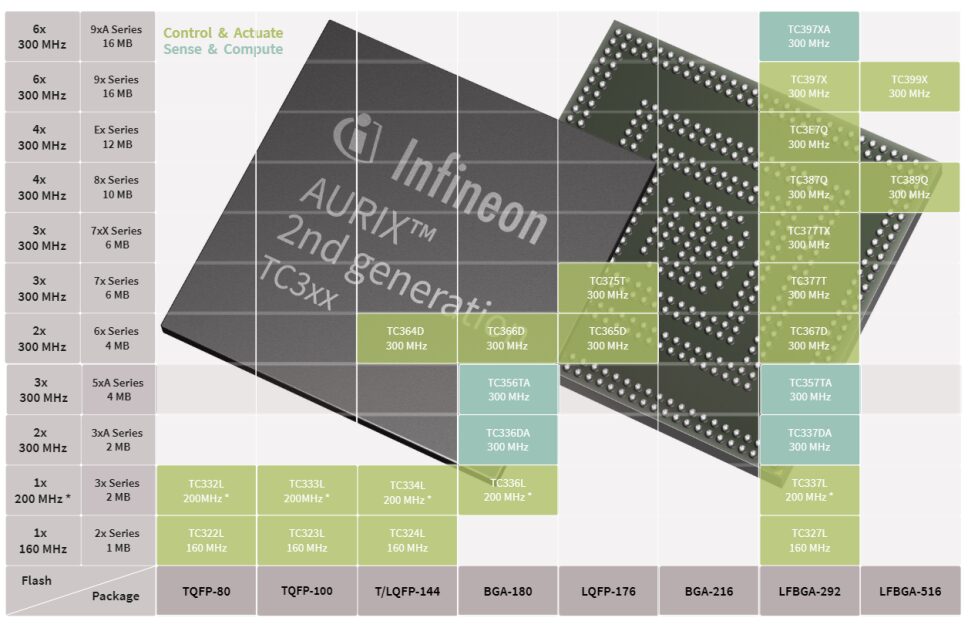

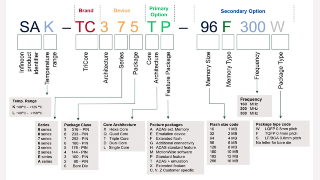

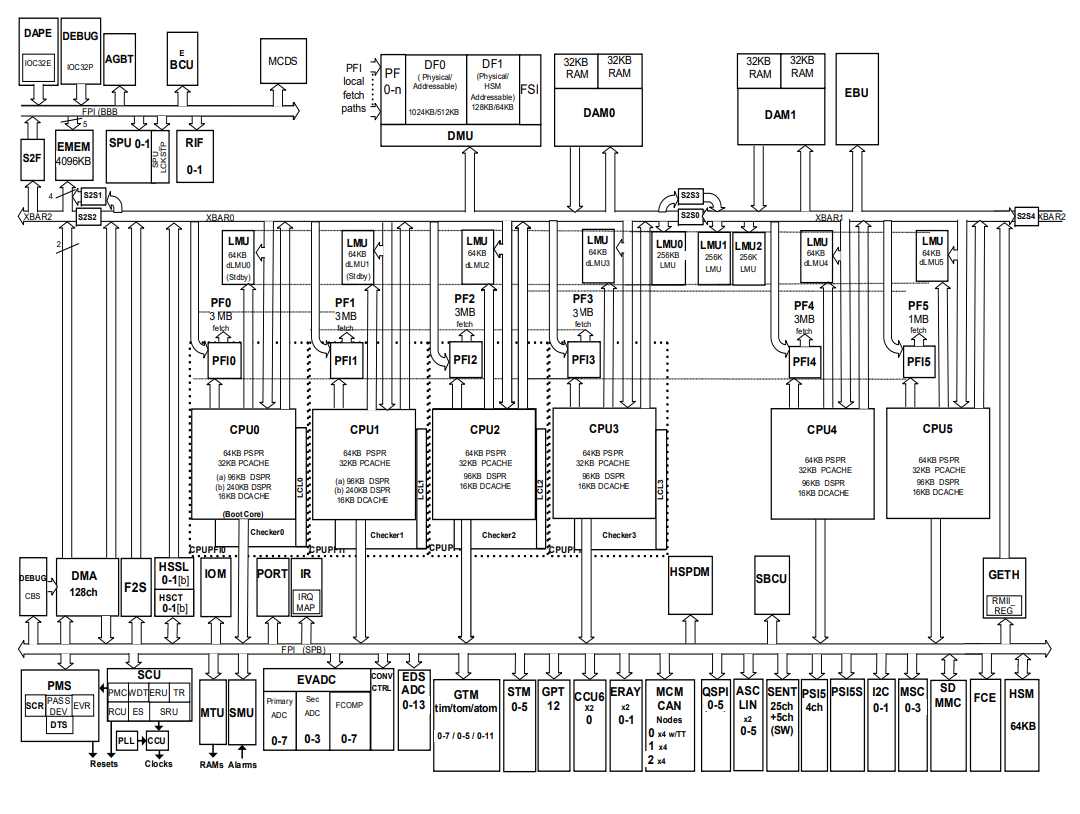

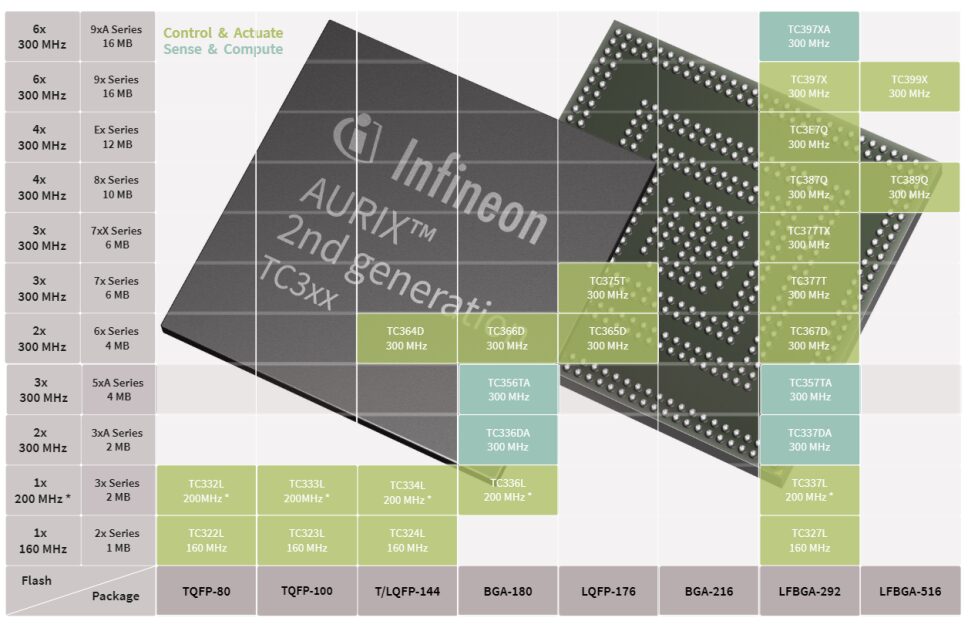

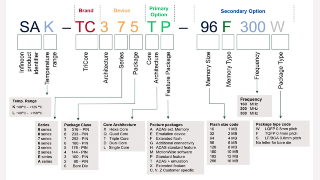

Overview of Infineon AURIX TC397

The TC397 belongs to the Infineon AURIX 2G series products, which feature a high-performance architecture with up to six cores, with a maximum clock frequency of 300MHz, achieving high-speed computing capabilities; in terms of storage, this series supports up to 16MB Flash and has A/B switching capabilities, allowing for convenient over-the-air software updates (SOTA); in terms of functional safety, this series of MCUs can be equipped with up to 4 lockstep cores, complying with ISO 26262 functional safety D-level; it also has a built-in hardware encryption module (HSM), which is very useful in the autonomous driving field.

|

|

Core: 6 TriCore™ running at 300 MHz (with 4 lockstep cores, providing 4000 DMIPS)

Flash: 16 MB flash/ECC protection

RAM: Up to 6.9 MB SRAM/ECC protection

Peripherals: 12xCAN FD, 2xFlexRay, 12xLINs, 4xQSP, 2xI²C, 25xSENT, 6xPSI, 2xHSSL, 4xMSC, 1x eMMC/SDIO

LVDS: 8×400 Mbit/s LVDS radar interface

SPU: 2x SPU (Signal Processing Unit) for radar signal processing

Timers: Redundant and diverse timer modules (GTM, CCU6, GPT12)

Encryption: EVITA complete HSM (ECC256 and SHA2)

Packaging: BGA-292 packaging

Functional Safety: Developed and documented according to ISO 26262/IEC61508 to support safety requirements up to ASIL-D/SIL3

AUTOSAR: Supports AUTOSAR 4.2

Power Supply: Single voltage power supply 5 V or 3.3 V

Temperature: 165°C junction temperature

|

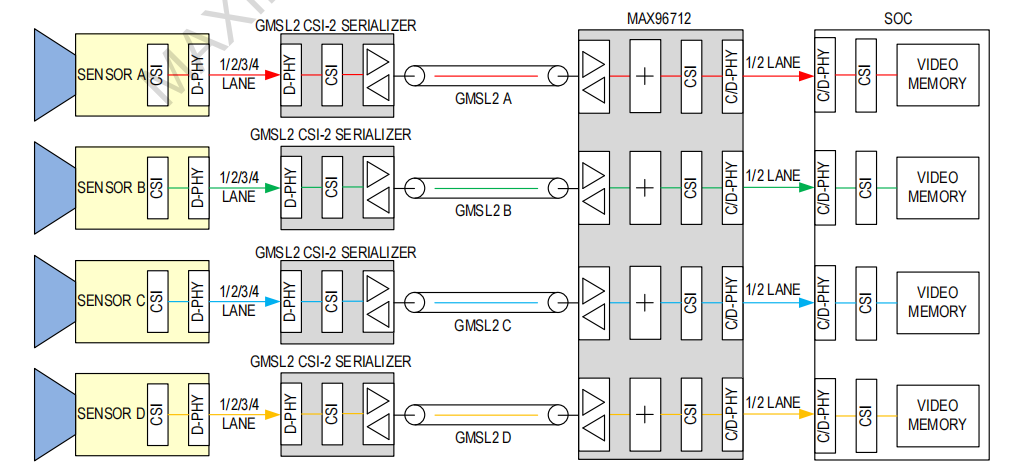

8. Serializer/Deserializer Chip

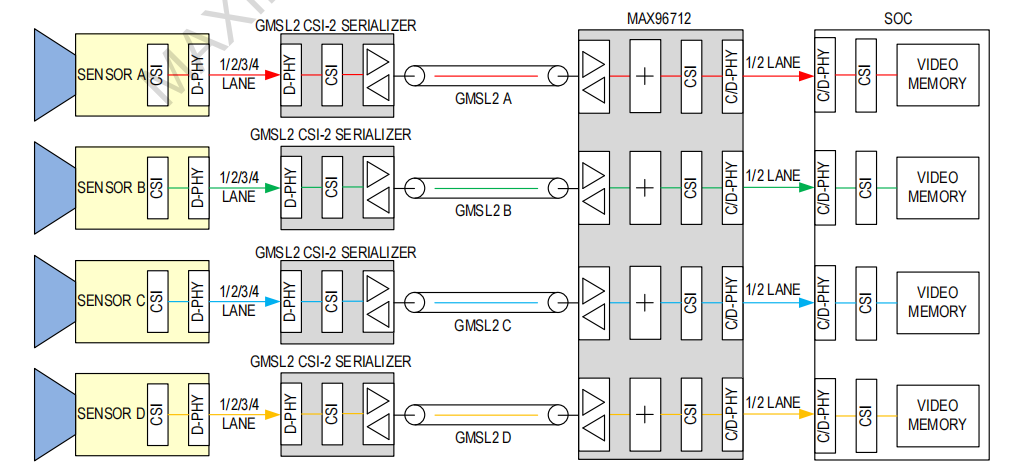

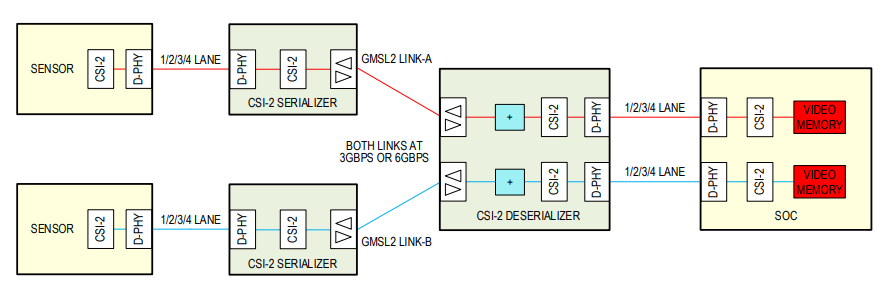

MAX96712 deserializer converts GMSL2 or GMSL1 serial input into MIPI CSI-2 D-PHY or C-PHY format output. This device allows simultaneous transmission of bidirectional control channel data while video transmission is ongoing for each link. MAX96712 can accommodate up to four remote sensors using industry-standard coaxial cables or STP interconnects. Each GMSL2 serial link operates at a fixed rate of 3Gbps or 6Gbps in the forward direction and 187.5Mbps in the reverse direction. In GMSL1 mode, MAX96712 can pair with first-generation 3.12Gbps or 1.5Gbps GMSL1 serializers or operate with GMSL2 serializers at up to 3.12Gbps.

MAX96712 supports aggregation and replication of video data, allowing data streams from multiple remote sensors to be combined and routed to one or more available CSI-2 outputs. Data can also be routed such that multiple streams from a single GMSL input can be independently routed to different CSI-2 outputs. Alternatively, frame-level cascading can synchronize and combine data from multiple sensors into a single CSI-2 stream within a composite superframe. The CSI-2 interface supports 2×4 channel and 4×2 channel configurations using C-PHY or D-PHY.

Various peripheral communication options are provided for flexible local register access and remote device programming. Three I2C/UART ports support parallel or tunneled remote peripheral communication with redundant local and remote internal register access. Two SPI ports are also available as tunnel interfaces to remote peripherals (GMSL2).

|

|

|

|

MIPI CSI-2 v1.3 output configurable to 2×4 channels, 1×4 lane + 2×2 lanes, or 4×2 lanes

|

• Optional D-PHY v1.2, 80Mbps to 2.5Gbps/channel or C-PHY v1.0, 182Mbps to 5.7Gbps/channel

• 16/32 channel virtual channel support (D/C-PHY)

• Flexible aggregation and routing of incoming data via CSI-2 VC or frame-level cascading

• Data can be replicated and routed to any CSI port

• Supports RAW8/10/12/14/16/20, RGB565/666/888, YUV422 8/10 bit formats

• Dual pixel mode for improved transmission efficiency

• CSI-2 lane reallocation and polarity inversion

• MIPI/GMSL video PRBS generator and checker

• Checkerboard/color gradient pattern generator

• Raw CSI-2 PRBS generator

• Independent configuration of all video paths and GMSL/CSI-2 ports

|

|

Four GMSL inputs, with independently configurable GMSL1/2 operation, link speed, and video format

|

• Mixed support for GMSL1/GMSL2 and 3G/6G

• Backward compatible with GMSL1 serializers

• GMSL1 forward link speed up to 3.12Gbps

• GMSL2 link speed of 3Gbps or 6Gbps (forward) and 187.5Mbps (reverse)

• Supports precise synchronization of multiple serializer systems for large camera systems

• GMSL PRBS generator/checker for link testing

• Eye monitor for continuous diagnostics

• Adaptive equalization for coaxial cables with multiple inline connectors up to 15 meters

• Compatible with 50Ω coaxial cables or 100Ω STP

|

|

|

• Video watermark insertion and detection

• 16-bit CRC protection for control channel data, retransmitted upon error detection

• Optional 32-bit CRC protection for video line data

• ECC protection for video data memory

• CRC protection for CSI-2 data streams

|

|

Concurrent control channels for device configuration and communication with remote peripherals

|

• 3 I2C/UART, 2 SPI, 17 GPIO

• Eight hardware selectable device addresses

|

|

Programmable spread spectrum to reduce EMI

|

|

64-lead 9mm x 9mm TQFN with exposed pads

|

System diagram of MAX96712 with four independent inputs and outputs

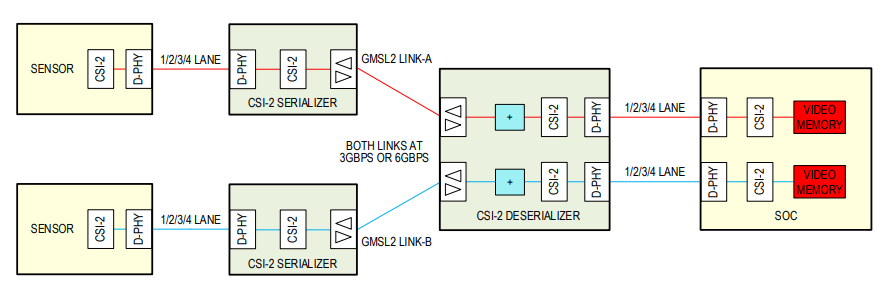

MAX9296A deserializer converts single or dual serial inputs into MIPI CSI-2 output. This device operates in GMSL1 or GMSL2 mode. MAX9296A also sends and receives side channel data, achieving full-duplex transmission of forward path video and bidirectional control data, compliant with 50Ω coaxial cables or 100Ω STP cables as per GMSL2 or GMSL1 channel specifications.

Physical image of MAX9296A

Block diagram of two independently running video sources of MAX9296A

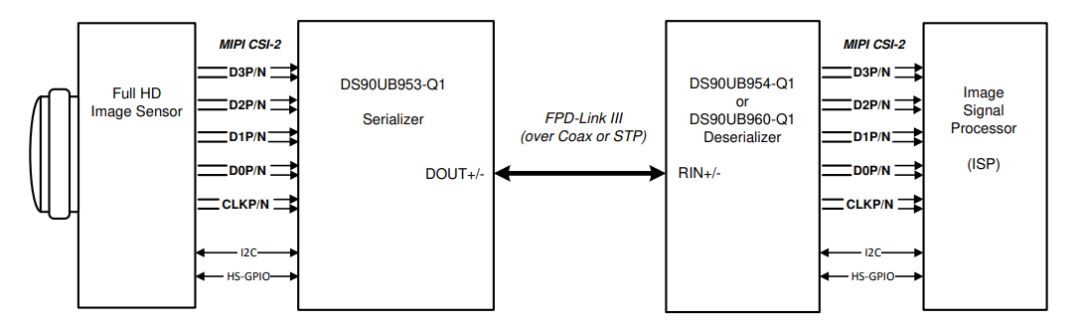

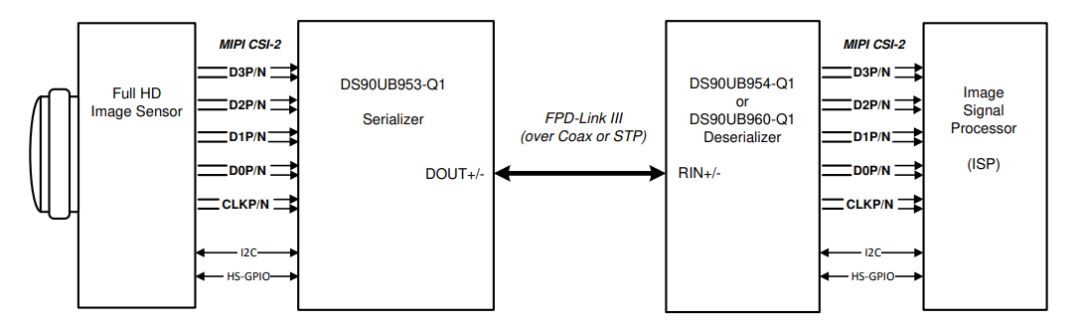

DS90UB953-Q1 serializer belongs to TI FPD-Link III device series, designed to support high-speed raw data sensors, including 2.3MP/60fps imagers and 4MP/30fps cameras, satellite radars, LiDAR, and time-of-flight (ToF) sensors. This chip provides 4.16Gbps forward channel and ultra-low latency 50Mbps bidirectional control channel, and supports power over coaxial (PoC) or STP cables. DS90UB953-Q1 features advanced data protection and diagnostic functions, supporting ADAS and autonomous driving. In conjunction with a matching deserializer, DS90UB953-Q1 can provide precise multi-camera sensor clocking and sensor synchronization.

|

|

• Complies with automotive AEC-Q100 standards: – Device temperature grade 2: operating temperature range -40°C to +105°C;

• Complies with ISO 10605 and IEC 61000-4-2 ESD standards;

• Coaxial cable power (PoC) compatible transceivers;

• 4.16Gbps grade serializer supports high-speed sensors, including full HD 1080p 2.3MP 60fps and 4MP 30fps imagers;

• System interface compliant with D-PHY v1.2 and CSI-2 v1.3 standards – up to 4 data channels, each channel rate of 832Mbps – supports up to four virtual channels

• Precise multi-camera clocking and synchronization

• Flexible programmable output clock generator

• Advanced data protection and diagnostics, including CRC data protection, sensor data integrity checks, I2C write protection, voltage and temperature measurements, programmable alarms, and line fault detection

• Supports single-ended coaxial or shielded twisted pair (STP) cables

• Ultra-low latency bidirectional I2C and GPIO control channels support ISP control from the ECU side

• 1.8V single power supply

• Low power consumption (0.28W typical)

• Provides functional safety – documentation to assist in ISO 26262 system design

• Compatible with DS90UB954-Q1, DS90UB964-Q1, DS90UB962-Q1, DS90UB936-Q1, DS90UB960-Q1, DS90UB934-Q1, and DS90UB914A-Q1 deserializers

• Wide temperature range: -40°C to 105°C

• Compact 5mm × 5mm VQFN package and PoC solution size suitable for compact camera module designs

|

|

|

• Advanced Driver Assistance Systems (ADAS)

– Surround view systems (SVS)

– Camera monitoring systems (CMS)

– Front-view cameras (FC)

– Driver monitoring systems (DMS)

– Rear-view cameras (RVC)

– Automotive satellite radar and LiDAR modules – Time-of-flight (ToF) sensors

• Security and surveillance cameras

• Industrial and medical imaging

|

Typical applications of UB953

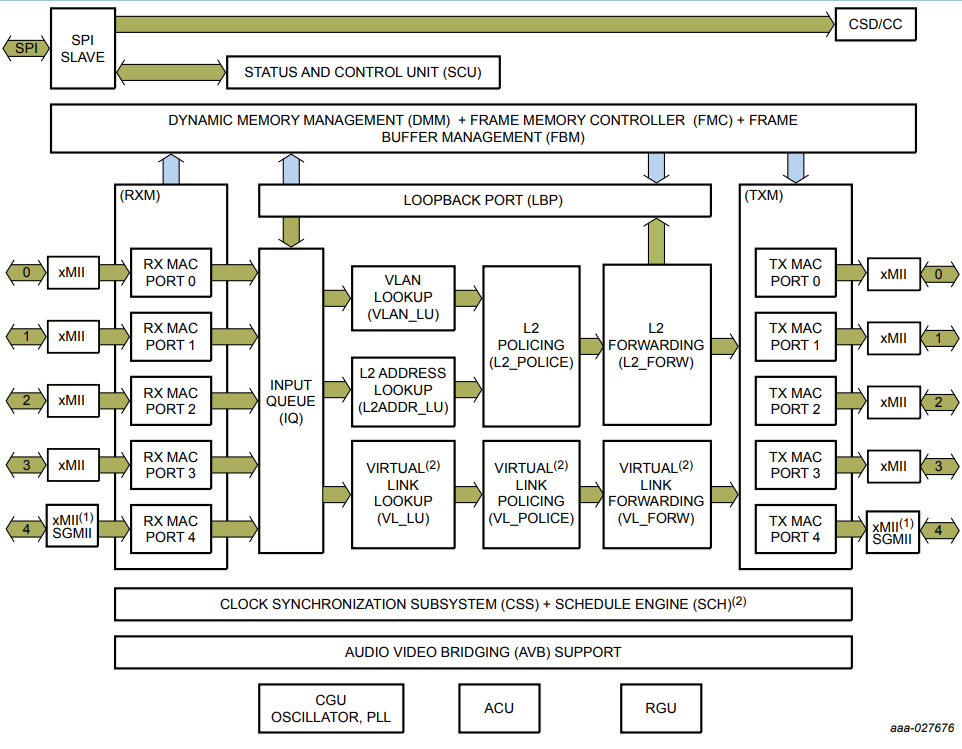

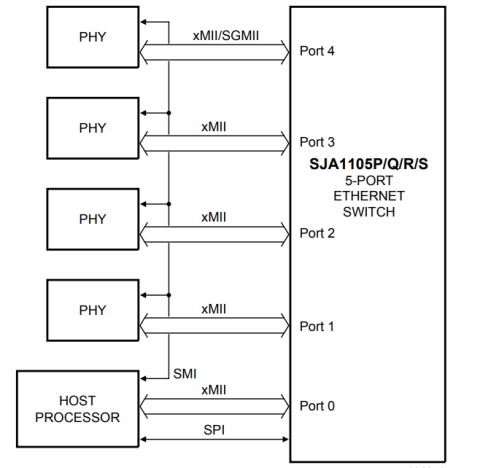

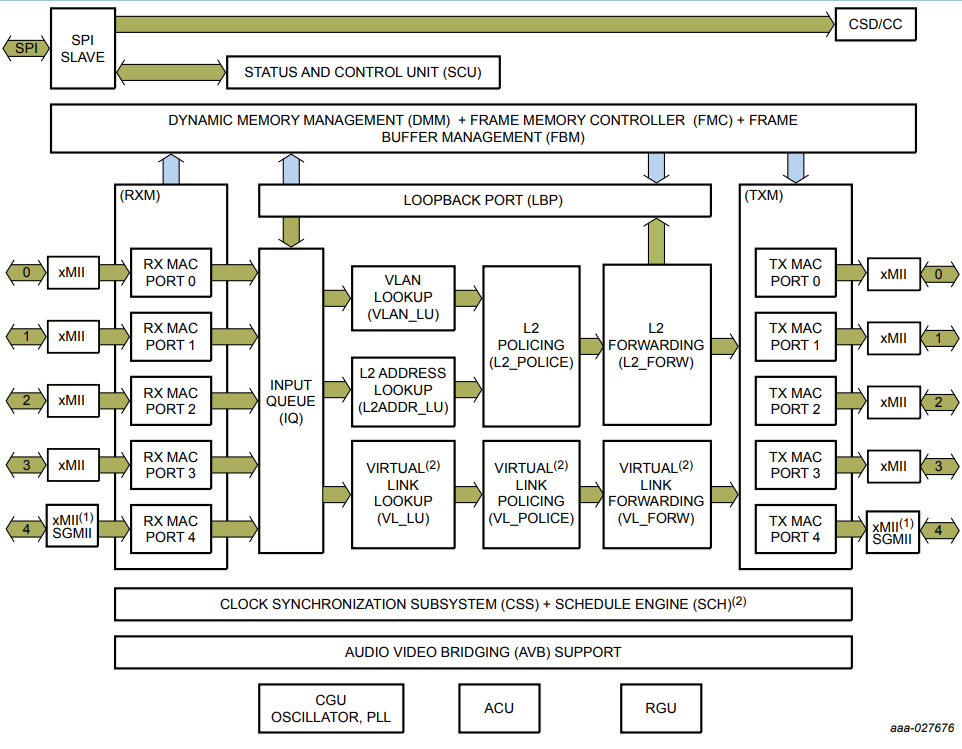

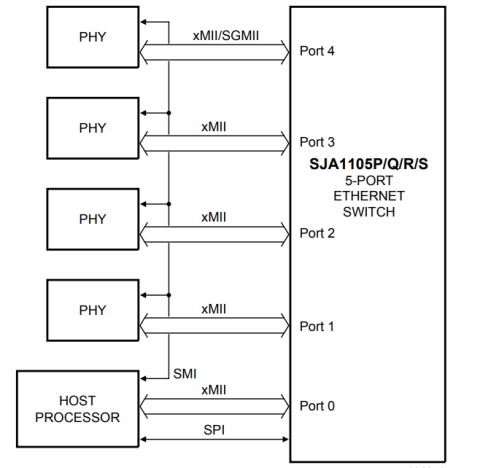

SJA1105P/Q/R/S is designed to provide a cost-optimized and flexible solution for automotive Ethernet switches. The SJA1105P/Q variants are functionally enhanced versions of SJA1105/T, plug-and-play alternatives. In the SJA1105R/S variants, one port provides SGMII functionality. These devices can be used in applications requiring SGMII connections to host processors or applications needing to cascade multiple devices.

SJA1105P/Q/R/S series of automotive Gigabit Ethernet switches enhance the capabilities of SJA1105/SJA1105T[1] switches with improved safety-related features, extended interface options, and ISO 26262 ASIL-A compliance.

SJA1105P/Q/R/S is a 5-port automotive Ethernet switch that supports IEEE Audio Video Bridging (AVB) and Time-Sensitive Networking (TSN) standards. Each of the five ports can be individually configured to operate at 10/100/1000 Mbit/s. This feature provides flexibility for connecting any Fast/Gigabit/Optical PHY or MCU/MPU to any port. Examples of external PHY include NXP Semiconductors’ [2] and [3] TJA1100 and TJA1102 IEEE 100BASE-T1 PHY.

All SJA1105P/Q/R/S variants offer new frame whitelisting/blacklisting, port reachability, and address learning limitation features, improving switch security by restricting data processing to known frames and data sources, preventing forwarding of erroneous or malicious data.

The updated MII/RMII/RGMII interfaces provide extended IO voltages such as 1V8 and 3V3 RGMII. Additionally, the SGMII interface available on the /R and /S variants expands the connection options for the switch. The /P and /Q variants do not have SGMII ports and maintain 100% pin compatibility with SJA1105/SJA1105T switches.

The SJA1105P/Q/R/S switch series is developed according to ISO 26262 standards. ASIL-A compliance reduces the design burden for safety-critical ECUs. Additional documents, including safety manuals, can be provided upon request.

These switches are compatible with IEEE AVB standards. The /Q and /S variants support extended TSN features such as 802.1Qbv. NXP’s native AUTOSAR drivers and AVB SW stack are available for this series.

Each port of SJA1105 can be independently configured for 10/100 Mbit/s MII/RMII or 10/100/1000 Mbit/s RGMII operation. The SGMII port on SJA1105R/S can be configured for 10/100/1000 Mbit/s operation. The SPI slave interface provides access to the device registers for the host processor.

SJA1105P/Q/R/S Ethernet switch connected to PHY and host processor system diagram

RT9010 is a low-noise, low-loss product with a power capability of up to 300mA and power-up reset functionality. Operating from an input range of 2.5V to 5.5V, the output voltage range is from 1.2V to 3.6V.

RT9010 features 2% accuracy, very low dropout (240mV@300mA), and extremely low ground current. The shutdown current is close to zero, making it suitable for battery-powered devices. Other features include current limiting, over-temperature, and output short-circuit protection.

RT9010 includes short-circuit thermal foldback protection. When an output short-circuit (VOUT<0.4V) occurs, RT9010 reduces its OTP trip point from 165°C to 110°C, providing maximum safety for end users.

|

|

Wide operating voltage range: 2.5V to 5.5V

Low noise for RF applications

No noise bypass capacitor required

Fast response in line/load transients

TTL logic controlled shutdown input

Low temperature coefficient

Over-temperature protection

Short-circuit thermal foldback protection

Compact TSOT-23-6 package

RoHS compliant, 100% lead-free

|

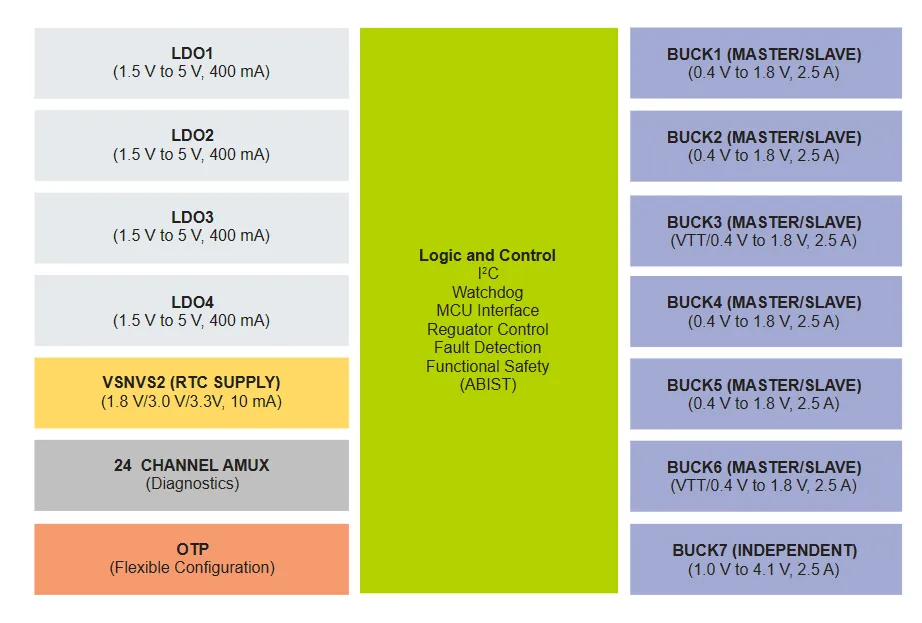

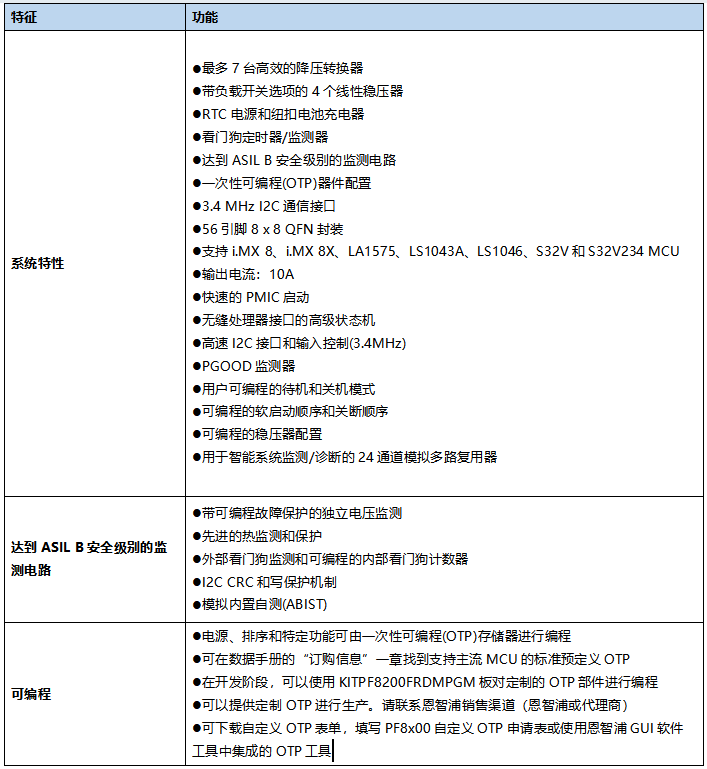

The power management module is also an important component in the autonomous driving domain controller. The power management chip is responsible for managing the power supply and energy management for the entire system, ensuring that each component operates normally.

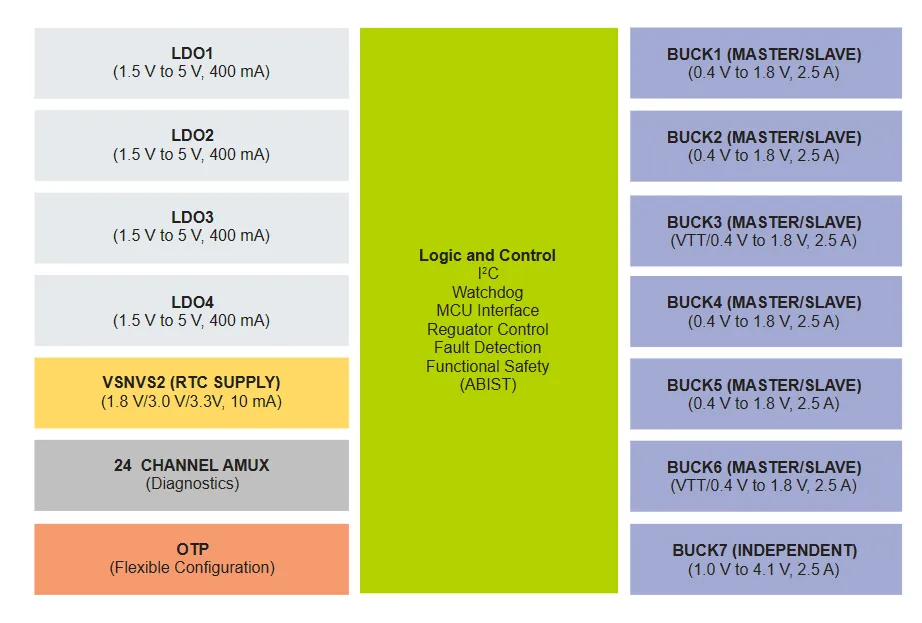

PF81/PF82 PMIC series is designed for high-performance processing applications such as entertainment control, in-vehicle information services, dashboards, automotive networks, ADAS, and sensor fusion.

Two versions are offered to meet different market needs:

-

PF82 with functional safety, compliant with ISO 26262 standards, providing a robust and flexible solution for ASIL-B (D) automotive applications.

-

PF81 is the basic version of this product, with power management and digital control functions, without functional safety, suitable for systems not requiring ASIL-B compliance.

TLF35584 is a multi-output system power supply designed for safety-related applications, providing 5V-μC, transceiver, and sensor through efficient and flexible pre/post-regulator concepts across a wide input voltage range. Due to the broad switching frequency range, it can be optimized for efficiency and minimal filtering component usage. It powers ADCs with dedicated reference regulators, providing independent tracking sources for two separate sensor power supplies. Flexible state machines, including timers, and backup regulators assist users in selecting applications.

The power management chip MPF5024AMMA0ES

PF5024 integrates multiple high-performance buck regulators. It can operate as a standalone load regulator IC or as a supporting chip for a larger PMIC.

It integrates one-time programmable (OTP) memory to store critical startup configurations, significantly reducing the external components typically used to set output voltages and regulator sequences. Regulator parameters can be adjusted post-startup via a high-speed I2C interface, providing flexibility for various system states.

PF5024 is a power management integrated circuit (PMIC) designed for building blocks of main power management for NXP’s i.MX8 and S32V series high-end multimedia application processors. It can also provide power solutions for high-end i.MX6 series and several non-NXP processors.

–SW1 to SW4: 0.4 V to 1.8 V; 2500mA

–Configurable as multiphase regulators

–VTT termination mode on SW2

–Programmable current limit

–Spread spectrum and manual tuning of switching frequency

–Global PGOOD output and PGOOD monitor

–Independent PGOOD output for each regulator

–Advanced state machine for seamless processor interfaces

–High-speed I2C interface support (up to 3.4 MHz)

–User-configurable standby and shutdown modes

–Programmable soft-start and power-down sequences

–Programmable regulator configuration

–Independent voltage monitoring with programmable fault protection

–Advanced thermal monitoring and protection

–External watchdog monitoring and programmable internal watchdog counter

–I2C CRC and write protection mechanism

–Analog built-in self-test (ABIST)

It is understood that this power chip has been discontinued.

Estimated Cost of the Scheme

Estimated total cost is approximately 3000 yuan.

Preview of the 2024 China Generative AI Conference

Click the business card below

The Intelligent Gorilla and Zhixdong will host the 2024 China Generative AI Conference (GenAICon 2024) in Beijing on April 18-19. The main venue will hold an opening ceremony, a large model session, an AI Infra session, and an AIGC application session; sub-venues will conduct discussions on embodied intelligence technology, AI agent technology seminars, and the China Smart Computing Center Innovation Forum. Registration is welcome for participation~

Click the business card below

Wired terminal diagram of the autonomous driving domain controller 2

Wired terminal diagram of the autonomous driving domain controller 2