1.5 The Conflict Between Dynamic Power and Static Power

Over the past 15 years, with the development of semiconductor technology, Vdd has decreased from 5V to 3.3V, and from 2.5V to 1.2V. The ITRS roadmap predicts that high-performance devices will use 1.0V in 2008 and 2009, while low-power devices will use 0.8V.

The issue with lowering Vdd is that it tends to reduce Ids, resulting in slower transistor speeds. Ignoring speed saturation and other subtle effects that occur below 90nm, the Ids of a MOSFET can be approximated as:

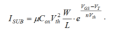

where u is the carrier mobility, Cox is the gate capacitance, Vt is the threshold voltage, and Vgs is the gate-source voltage. Thus, to maintain good performance, we need to lower Vt while reducing Vdd (and Vgs). However, lowering the threshold voltage (Vt) leads to an exponential increase in subthreshold leakage current (Isub) as follows:

Thus, a conflict arises. To reduce dynamic power, we lower Vdd; to maintain performance, we lower Vt; but the result is an increase in leakage current. When the process is not very advanced, this is a reasonable approach, as the static power generated by leakage current is far less than dynamic power. However, with 90nm technology, we will reach a point where static power and dynamic power are equally important, and we need to reassess this issue.

1.6 Static Power Consumption

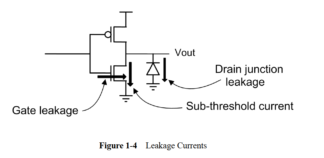

There are four main sources of leakage current in CMOS gates (Figure 1-4)

Subthreshold leakage (Isub): The current flowing from the drain to the source of a transistor operating in the cutoff region (or subthreshold state).

Gate leakage (Igate): The current flowing directly from the gate through the oxide to the substrate due to gate oxide tunneling and hot carrier injection.

Gate-induced drain leakage (Igidl): The current flowing from the drain to the substrate caused by high electric fields due to high drain-gate voltages in the MOSFET.

Reverse-biased junction leakage (Irev): Caused by the drift of a small number of carriers and the generation of electron-hole pairs in the depletion region.

Subthreshold leakage occurs when the CMOS gate is not fully turned off. Its value can be approximated as:

In this equation, W and L are the dimensions of the transistor, and Vth is the thermal voltage kT/q (25.9mV at room temperature). The parameter n is a function of the device manufacturing process, ranging from 1.0 to 2.5.

This equation tells us that the amount of subthreshold leakage has an exponential relationship with the difference between Vgs and Vt. Therefore, when we reduce Vdd and Vt (to limit dynamic power), leakage power worsens exponentially.

Gate leakage results from tunneling current through the gate oxide. In 90nm gates, the thickness of the gate oxide layer is only a few atomic layers thick—so thin that the tunneling current can become quite significant. In previous technology nodes, leakage current was primarily subthreshold leakage. However, starting from 90nm, gate leakage current is almost 1/3 of the subthreshold current. In the 65nm range, it can equal subthreshold leakage in some cases. Future nodes will require high-k dielectric materials to control gate leakage, which seems to be the only effective method to reduce gate leakage.

Subthreshold leakage current increases exponentially with temperature. This complicates the design of low-power systems. Even at room temperature, leakage can be acceptable, but in the worst case, it can exceed the chip’s design.

There are several methods to reduce leakage current.

One technique is called Multi-Vt: using high Vt cells where performance targets allow, and low Vt cells where timing needs to be met.

The second technique is to turn off the power when logic blocks are inactive. This method is known as power gating.

These two methods will be discussed in detail in later chapters. However, we will now mention three additional techniques:

VTCMOS: Variable Threshold CMOS (VTCMOS) is another very effective method for reducing static leakage current. By applying a reverse bias voltage to the substrate, the value of Vgs-Vt can be reduced. This method can reduce static leakage current by up to three orders of magnitude. However, VTCMOS increases the complexity of the library, requiring two additional grids to control the voltage applied to the wells. Unfortunately, the effectiveness of reverse body bias is decreasing with the application of scaling technology.

Stack Effect: When multiple transistors are turned off, the stack effect or self-reverse bias can help reduce subthreshold leakage. This is mainly because a small amount of subthreshold leakage causes the intermediate nodes between stacked transistors to be pulled away from the power/ground rails.

The figure below shows two series OFF transistors, where the drain of N2 is at VDD, so the stack leaks due to DIBL (Drain-Induced Barrier Lowering), but the intermediate node Vx stabilizes to the point where each transistor has the same current.

If Vx is relatively small, N1 will see a smaller DIBL effect, leaking less. If Vx is relatively large, DIBL for the (gate to source) voltage of N2 becomes negative, reducing its leakage.

Thus, we expect the leakage of series transistors to be less.

A stack with three or more transistors will have lower leakage compared to a stack with fewer transistors (i.e., two).

Long Channel Devices: From the subthreshold current equation, it can be seen that using long channels will reduce leakage. Unfortunately, long channel devices have lower dynamic current, leading to performance degradation. They have larger gate capacitance, which adversely affects dynamic power and further reduces performance. Unless the switching activity of long channel devices is very low, the total power dissipation may not decrease. Therefore, when using long channel devices, switching activity and performance targets must be considered.