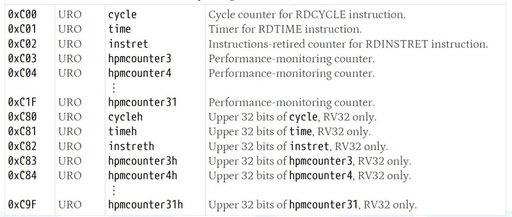

RISC-V Performance Counters and Timer Extensions – Zicntr and Zihpm

Introduction: RISC-V (pronounced “risk-five”) is a new instruction set architecture (ISA) originally designed to support research and education in computer architecture. However, in recent years, it has evolved into a standardized, free, and open architecture for industrial implementations. One significant advantage of the RISC-V instruction set is its scalability, allowing users to select appropriate extension … Read more