| Source: SIMIT Strategic Research Office (ID: SIMITSRO)

Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences

The two major architectures of current CPUs are CISC (Complex Instruction Set) and RISC (Reduced Instruction Set). x86 is the representative architecture of CISC, occupying over 95% of the desktop computer and server market. Arm, as a type of RISC, holds a major position in the mobile processor market, including smartphones and wearable devices. In response to the emerging fields of IoT, 5G, and AI applications, the two major reduced instruction set architectures, RISC-V and MIPS, have once again taken the historical stage.

– RISC-V –

Introduction to RISC-V

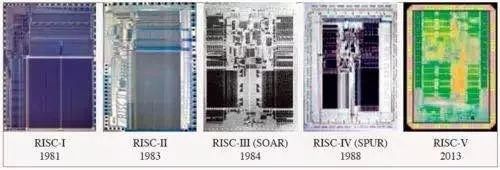

RISC-V is a free and modular RISC instruction set developed by U.C. Berkeley. The “V” has two meanings: firstly, it is the fifth generation of instruction set architecture designed by Berkeley starting from RISC I; secondly, it represents variation and vectors.

Professor David Patterson led the development of the fifth-generation RISC processor.

In December 2015, a team of researchers from U.C. Berkeley and several other universities published an article on the Nature website. In the article, researchers manufactured a microchip that integrated both the RISC-V instruction set CPU and an on-chip optical communication device using standard CMOS technology. This marks a significant increase in the interface speed of microelectronic chips in the near future, no longer limited by the previous electrical interface IO speeds.

Unlike the high IP costs of x86 and Arm architectures, the RISC-V architecture provides great freedom to users under the BSD open-source license, allowing users to modify and redistribute the open-source code, as well as develop and sell commercial software based on the open-source code.

Development of RISC-V

For any new technology, especially an open standard, factors such as technology, ecosystem, platform choices for chip and system developers, security, software, and investment are all stepping stones on the long road to transforming great ideas into commercial success and widespread industry application. From the convening of the RISC-V Workshop in 2015, the establishment of the RISC-V Foundation, to the formation of the China RISC-V Industry Alliance in 2018, as well as the first global RISC-V Summit held at the end of 2018, a series of actions demonstrate that RISC-V is thriving. Of course, the commercialization of RISC-V also relies on the promotion of enterprises and strong support from national policies.

1. RISC-V Workshop

Since 2015, many meaningful projects have emerged at the Workshop held every six months. For instance, Berkeley has developed several open-source processors that cover applications from high-performance computing to embedded systems, and has incubated the startup SiFive, which has received venture capital.

2. RISC-V Summit

The first global RISC-V Summit was held in Silicon Valley from December 3-6, 2018, with over 1,000 software and hardware professionals related to chip design attending the summit.

3. RISC-V Foundation

The RISC-V Foundation was established in 2015 as a non-profit organization dedicated to promoting the application and implementation of the free and open-source RISC-V instruction set architecture. Members of the RISC-V Foundation can access and participate in the development of RISC-V ISA specifications and related HW/SW ecosystems. The RISC-V Foundation consists of over 200 member organizations, including U.C. Berkeley, MIT, Princeton University, ETH Zurich, IIT, Lawrence Livermore National Laboratory, Nanyang Technological University in Singapore, and the Institute of Computing Technology, Chinese Academy of Sciences; semiconductor manufacturers such as Qualcomm, NVIDIA, NXP, Samsung, Microsemi, Micron, TSMC, SiFive, ZTE Microelectronics, Huawei HiSilicon, MediaTek, and Cloud Semiconductor; IT companies like Google and IBM; hard drive manufacturers like Western Digital and Seagate; and development tool companies like SEGGER, Mentor Graphics, and Express Logic; as well as investment companies like Xiamen Semiconductor Investment Group.

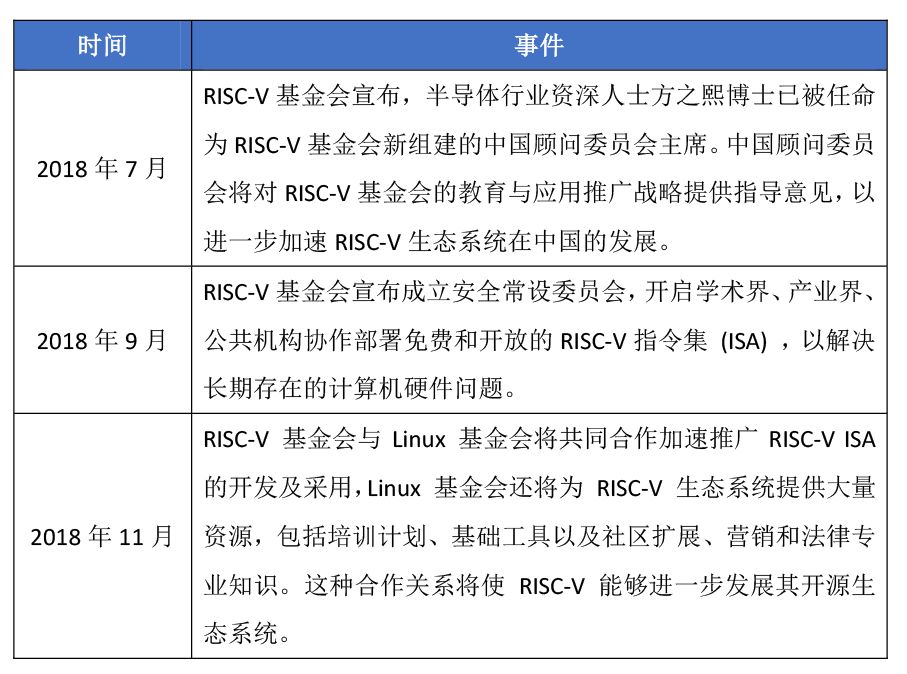

Key events of the RISC-V Foundation in 2018

4. China RISC-V Industry Alliance

In September 2018, the China RISC-V Industry Alliance was established in Zhangjiang, Shanghai, initiated by Shanghai SiFive, Xinkai Technology, Shanghai Saifang Technology (SiFive China), Hangzhou Zhongtian Microelectronics, Beijing Junzheng, Zhaoyi Innovation, Zhixiang Er Microelectronics, Lexin Technology, Shixin Electronics, Spreadtrum Communications, Horizon Robotics, Amlogic, BGI Semiconductor, Shanghai High-Performance Integrated Circuit Design Center, Shanghai Integrated Circuit Industry Association, and Shanghai Internet of Things Industry Association, with Shanghai SiFive serving as the first chairman unit of the alliance.

The purpose of the China RISC-V Industry Alliance is to gather advantageous resources, with the market mechanism as the main body, supplemented by moderate overall coordination and cooperation, to enhance China’s participation in the development of RISC-V standards and technology, accelerate the improvement of the domestic RISC-V “IP core – chip – software – complete machine – system” industrial ecosystem, and promote support for the development of the RISC-V industry from the industry, academia, and investment circles in China. The China RISC-V Industry Alliance will focus on the following aspects: first, building an industry communication platform to promote the widespread application of RISC-V; second, promoting RISC-V talent cultivation and establishing a training program for universities; third, promoting collaborative development among members and establishing a long-term cooperation mechanism; fourth, undertaking activities of the global RISC-V Foundation to deepen international cooperation and exchanges.

5. National Policies/Strategies

In 2017, the Indian government stated that it would vigorously fund RISC-V-based processor projects, making RISC-V the de facto national instruction set of India.

The Israel Innovation Authority chose to develop a service platform for national enterprises based on RISC-V, creating the RISC-V GenPro incubator.

The U.S. Defense Advanced Research Projects Agency (DARPA) is promoting five projects for open-source IP: the Performance Revolution for Embedded Computing (PERFECT), Faster Integrated Circuits (CRAFT), System Security Integration via Hardware and Firmware (SSITH), Posh Open Hardware (POSH), and Intelligent Design of Electronic Assets (IDEA), among which CRAFT, POSH, and IDEA explicitly require development based on the RISC-V instruction set.

Shanghai has become the first city in China to include RISC-V in its government support targets. In June 2018, the Shanghai Municipal Economic and Information Commission issued a notice regarding the 2018 annual second batch of special funds for the development of the Shanghai software and integrated circuit industry (in the field of integrated circuits and electronic information manufacturing), one of which is to support companies engaged in RISC-V-related design and development.

6. Progress of Representative Enterprises

(1) SiFive

In July 2015, RISC-V pioneers Krste Asanovic, Yunsup Lee, and Andrew Waterman founded SiFive to accelerate the commercialization of RISC-V. Currently, one-third of the employees are members of the RISC-V R&D team. On May 8, 2017, SiFive announced the completion of $8.5 million in Series B financing. On April 2, 2018, SiFive announced the completion of $50.6 million in Series C financing, with existing investors Sutter Hill Ventures, Spark Capital, Osage University Partners, and new investors Intel Capital, Chengwei Capital, as well as industry companies like Huami, SK Telecom, and Western Digital participating in the Series C financing.

SiFive currently has two types of products: one is the Core IP of the RISC-V instruction set; the other is Freedom SoC designs, including the low-cost Freedom Everywhere platform (designed for microcontrollers, embedded products, IoT, and wearable applications) and the high-performance Freedom Unleashed platform (for machine learning, storage, and networking applications).

SiFive has established deep cooperative relationships with several internationally renowned semiconductor manufacturers. For example, Western Digital announced that all memory controller chips planned for its products will adopt RISC-V IP, with an estimated future annual shipment volume of 2 billion cores; the SSD controller chips of South Korean company FADU will adopt SiFive Core IP.

(2) Western Digital

In November 2017, Western Digital’s CTO Martin Fink announced at the seventh RISC-V Working Group meeting that the 1-2 billion processor cores used annually in Western Digital products will be replaced with RISC-V processor cores. Western Digital is also one of the investment partners of AI chip startup Esperanto, which aims to develop energy-efficient, high-performance computing solutions based on RISC-V.

In December 2018, Western Digital announced three important announcements regarding the RISC-V processor launched last year, unveiling the self-developed general-purpose architecture SweRV based on the RISC-V instruction set and the open-source SweRV instruction set simulator (ISS), as well as the cache coherence technology based on Ethernet OmniXtend. Western Digital expects that hardware and software will be used in various solutions for big data and fast data applications, including flash memory controllers and SSDs.

SweRV Architecture

Western Digital plans to provide the SweRV architecture as an open-source product to third parties starting in the first quarter of 2019, hoping to promote the eventual adoption of the RISC-V instruction set by hardware and software developers through third-party usage.

SweRV Instruction Set Simulator (ISS)

This program allows software designers to simulate the execution of their code on the SweRV core, simplifying program development, which is crucial for promoting the adoption of RISC-V.

OmniXtend Technology

This technology was developed by Western Digital in collaboration with SiFive, enabling cache coherence over Ethernet. Western Digital hopes this technology can add non-volatile memory to processors, while also stating that this memory-centric architecture can be used for other components like CPUs, GPUs, FPGAs, and machine learning accelerators.

(3) Huami Technology

In September 2018, Huami Technology released the world’s first AI chip for smart wearables: Huangshan No. 1, which adopts the RISC-V architecture instead of ARM architecture, thus being the world’s first RISC-V open-source instruction wearable processor. In the RISC-V architecture, Huami has incorporated its own AI engine, divided into four parts: two ECG engines, one biometric recognition engine, and one heart disease recognition engine. Among them, the biometric recognition engine can determine whether the tester is the owner based on the heart condition of each individual. Huangshan No. 1 has successfully taped out and is expected to be officially commercialized in the first half of 2019.

Since 2015, RISC-V has gained significant momentum, attracting hundreds of technology companies including IBM, NXP, Western Digital, NVIDIA, Qualcomm, Samsung, Google, Huawei, and Tesla to join its ranks, and the industry is continuously building an ecosystem around it, causing a significant impact on Arm. However, MIPS, as its competitor, has also proven its strength on the path to commercialization, with CPU chip shipments based on MIPS reaching 8.5 billion since 2000. Now returning to open-source, following the path of “Simplicity”, it remains to be seen who will emerge victorious and where the chips will fall. The next article will briefly discuss MIPS.

If RISC-V is a new recruit emerging from academia, then MIPS is an old veteran that has been through the market for many years. Next, let’s talk about MIPS, which aspires to be China’s Arm.

– MIPS –

Introduction to MIPS

MIPS stands for “Microprocessor without interlocked piped stages”, and is one of the derivative architectures based on the reduced instruction set (RISC). Its mechanism aims to avoid data dependency issues in the pipeline by using software methods as much as possible. It was first developed in the early 1980s by a research team led by Professor Hennessy at Stanford University.

Development of MIPS

The MIPS instruction set is closely tied to the development of MIPS Corporation, and its commercialization journey has been fraught with challenges.

In 1981, Professor John Hennessy of Stanford University released the first MIPS chip.

In 1984, Professor Hennessy left Stanford University to found MIPS Computer Systems Inc. In 1986, the R2000 chip was launched. In 1988, the R3000 chip was launched.

In 1989, MIPS Computer Systems Inc. went public, focusing on workstations.

In 1991, MIPS Corporation released the world’s first 64-bit processor, the R4000.

In 1992, Silicon Graphics Inc. (SGI) acquired MIPS Computer Systems Inc., forming MIPS Technology Inc. (MTI), releasing the R8000 in 1994, the R10000 in 1996, and the R12000 processor in 1997.

In 1998, after spinning off from SGI, MIPS Technologies Inc. went public again, changing its strategy to focus on embedded systems. In 1999, MIPS Corporation released the MIPS32 and MIPS64 architecture standards, laying the foundation for the development of future MIPS processors. MIPS Corporation continued to develop high-performance, low-power 32-bit core processors (MIPS324Kc) and high-performance 64-bit core processors (MIPS64 5Kc). In 2000, MIPS Corporation released versions targeting the MIPS32 4Kc and 64-bit MIPS 64 20Kc processor cores.

In 2002, the Institute of Computing Technology, Chinese Academy of Sciences began developing the Loongson processor using the MIPS architecture without authorization from MIPS Corporation, resulting in an infringement lawsuit.

In 2009, the Chinese Academy of Sciences reached a settlement with MIPS Corporation and obtained formal authorization. Loongson purchased the MIPS architecture license, which is known as the instruction set system, and later added a permanent buyout of the MIPS license.

In 2012, MIPS sold another 498 patents for $350 million to Bridge Crossing LLC (the parent company of ARM).

In 2013, the UK company Imagination acquired MIPS Corporation for $60 million in cash. Imagination gained full control of MIPS, including 82 key patents of the MIPS architecture, and authorized all remaining patents of MIPS, which will continue to develop as part of Imagination.

In 2017, Imagination sold its U.S.-based embedded processor division MIPS to Tallwood MIPS for $65 million. Tallwood MIPS is indirectly owned by the California investment firm Tallwood Venture Capital.

In June 2018, AI chip startup Wave Computing acquired MIPS.

In December 2018, Wave Computing announced that the MIPS architecture will soon be open-sourced.

MIPS Ecosystem

To build a competitive processor, the architecture used must not only be a globally universal architecture but also have a supportive ecosystem. From the RISC-V Workshop, RISC-V Foundation to the China RISC-V Industry Alliance, and the first global RISC-V Summit, the commercialization of RISC-V seems to have been planned, suddenly launching a full-scale construction of its ecosystem.

Unlike the development of RISC-V, over 8.5 billion chips based on the MIPS architecture have been delivered in thousands of commercial solutions to date. MIPS does not have a foundation or summit; it only joined the Linux Foundation in 2016 as a member and has had lukewarm design seminars based on the MIPS architecture, which are more like product promotion events. MIPS has been struggling to survive in the cracks, from workstations and desktop computers to embedded systems and artificial intelligence.

From MIPS’s layout, its application in servers and networks is relatively stable, but the market share change remains uncertain. There seems to be little hope in the mobile market, while no giant player has emerged in the emerging smart hardware field for the time being.

Wave Computing announced the upcoming opening of the MIPS architecture, providing free MIPS architecture to global semiconductor companies, developers, and universities for the development of the next generation SoC. The MIPS architecture open-source plan will offer the latest 32-bit and 64-bit MIPS architectures for free to all participants, without incurring architecture licensing fees and copyright fees, while also providing users of all MIPS architectures with protection for hundreds of existing patents worldwide.

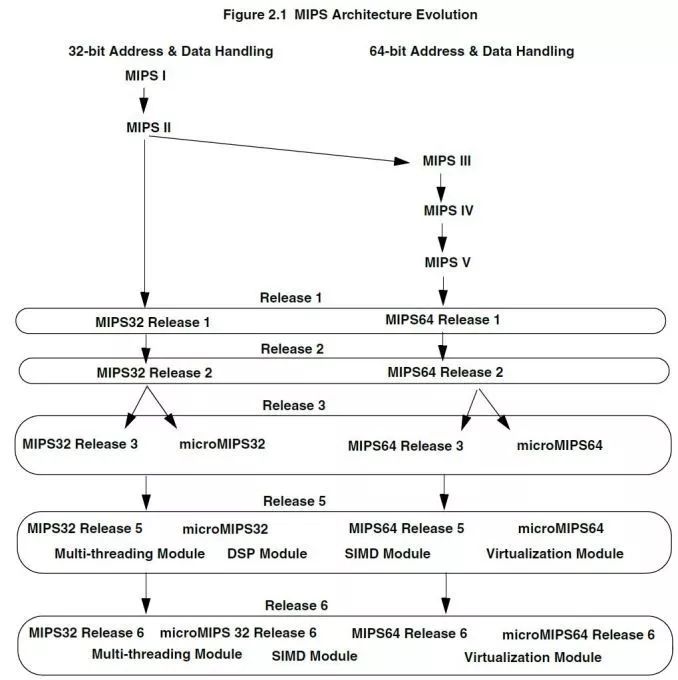

MIPS architecture evolution chart

This open-source plan targets the MIPS R6 instruction set, which is a nearly brand-new instruction set for MIPS, with extensive optimizations made to the previous MIPS architecture, and the core has been redesigned. The ecological advantages previously accumulated by MIPS may not be fully realized. Moreover, even though MIPS provides compatibility tools for customers of early MIPS versions, the porting process may still involve a significant amount of work.

MIPS has the support of industry leaders such as Broadcom, Cavium, Intel (Mobileye), Loongson, Jieli, and Junzheng. MIPS has a wealth of mature tools, software environments, and patents, and the open-sourcing of its instruction set is beneficial for the entire MIPS ecosystem, and may also present an opportunity for domestic companies. Previously, Loongson had one-time bought out the MIPS instruction set license and then developed and expanded the instruction set itself, but this approach posed a significant problem in establishing an ecosystem. It is impossible to rely solely on Loongson to promote the construction of the Loongson ecosystem. With this MIPS open-source initiative, it is hoped to promote development in China.

This article is original to the SIMIT Strategic Research Office. For reprints, please contact [email protected]