Jianbo Micro AI RISC-V Server Encryption Chip: In-Depth Practice of Domestic Computing Power Security

In today’s rapidly advancing technology landscape, computing power security has become an essential component of national technology strategy. At the beginning of 2025, a joint announcement by eight departments regarding the “Guidelines for Promoting RISC-V Chip Applications” has sparked a wave of domestic chip substitution. The policy clearly mandates that servers in critical areas such as finance and government must use domestic encryption chips, which not only opens up a trillion-level market space for local enterprises but also presents a historic development opportunity for domestic chips.

According to industry analysis reports, the market size of China’s server chip industry has surpassed 200 billion yuan, with the localization rate showing an accelerating upward trend. Against this backdrop, Jianbo Microelectronics focuses on the in-depth development of the RISC-V architecture, positioning its AI server encryption chip to address the dual demands of data security and computing efficiency. By integrating a hardware-level encryption engine with customized computing units, Jianbo Micro’s technical route aligns deeply with the national strategy of “independent and controllable”.

With the implementation of the “Cybersecurity Law” and the “Data Security Law”, server chips are no longer merely carriers of computing power; they are gradually transforming into core components of security infrastructure. Jianbo Micro’s exploration and practice undoubtedly inject strong momentum into domestic computing power security.

1. Independent Architecture: From Open Source to Controllable Technical Breakthroughs

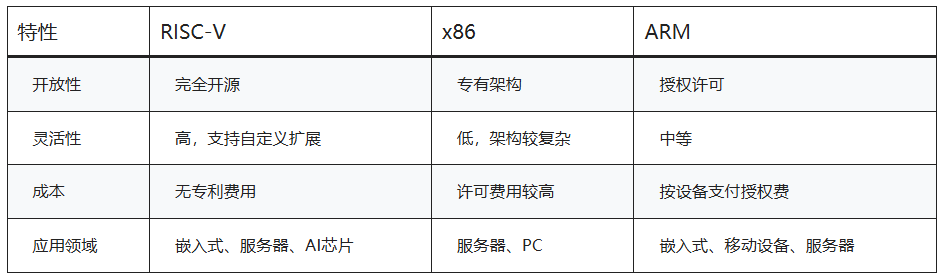

The architectural vulnerabilities of traditional server chips are becoming increasingly prominent. The ARM architecture faces the risk of license termination, the X86 instruction set cannot be modified independently, and third-party encryption IP modules may become security weaknesses. Jianbo Micro has chosen the RISC-V open-source architecture as a breakthrough point to fundamentally establish technological autonomy.

(Comparison of RISC-V Architecture with Other Architectures)

1. Deep Customization of Instruction Set

Deep customization of the instruction set has become the first technical barrier. Based on the RV64GC base instruction set, Jianbo Micro has expanded and developed a dedicated instruction set for encryption, achieving hardware-level acceleration for national cryptographic algorithms SM2/SM3/SM4/SM9.

According to corporate testing reports, its encryption engine achieves a processing speed of 10Gbps, improving performance by 20 times compared to software solutions. This breakthrough makes the CW3832BT80 chip one of the first domestic server encryption solutions to pass CC EAL4+ certification, while also meeting financial PCI-DSS standards and government level three requirements.

2. Heterogeneous Architecture Innovation

In the face of challenges from complex application scenarios, heterogeneous architecture innovation demonstrates unique value. Jianbo Micro employs a three-layer design of “CPU + encryption coprocessor + hardware security module (HSM)”, improving IOPS performance by 45% in distributed storage tests while reducing system power consumption by 38%.

This architecture allows a single chip to handle microsecond-level responses for financial transactions while also undertaking PB-level data encryption tasks for government cloud, showcasing strong adaptability and flexibility.

3. Toolchain Autonomy

To build a complete technical ecosystem, Jianbo Micro is simultaneously advancing toolchain autonomy. The self-developed LLVM compiler supports multi-core parallel debugging and is deeply compatible with domestic operating systems such as Kirin and Tongxin UOS.

Corporate technical white papers indicate that this toolchain achieved a 98% pass rate in compatibility testing, laying a solid foundation for the large-scale deployment of chips.

2. Dual Breakthroughs in Security and Efficiency

At the testing center in Nanjing Jiangbei New Area, the Jianbo Micro CW3832BT80 chip is undergoing extreme stress testing. Key performance metrics recorded in technical documents include: DDR5 9600MT/S memory bandwidth support, 15W typical power consumption control, and microsecond-level encryption response capability. The realization of these indicators stems from three core technological breakthroughs:

(Jianbo Micro CW3832BT80 Chip)

(Jianbo Micro CW3832BT80 Chip)

1. Hardware-Level Key Management System

The hardware-level key management system builds a security foundation. The chip integrates an independent security module (HSM) to achieve full lifecycle protection for key generation, storage, and usage.

In banking transaction scenarios, it supports a “one transaction, one key” mechanism, physically blocking the risk of key leakage. This design has passed the security assessment of the National Cryptography Administration, providing strong protection for data security in critical areas such as finance.

2. Quantum-Resistant Technology Research

Quantum-resistant technology research targets future threats. Jianbo Micro collaborates with the Chinese Academy of Sciences to conduct hardware research on lattice-based algorithms, focusing on breaking through the energy efficiency bottleneck of post-quantum encryption.

The technology roadmap indicates that this project aims to be applied in the security system construction of the national “East Data West Computing” project, laying out plans for the future of network security.

3. Energy Efficiency Optimization Technology

Energy efficiency optimization technology addresses industry challenges. Through chip-level clock gating and voltage regulation technology, power consumption is controlled at 15W under a 10Gbps encryption load.

Corporate testing data shows that this indicator reduces power consumption by 40% compared to similar imported chips, significantly alleviating the heat dissipation pressure in data centers and contributing to the construction of green data centers.

3. Empirical Path of Industrial Implementation

The technical value must be verified through scenarios. Jianbo Micro chips have made substantial progress in three major areas:

1. Financial Sector

The financial sector has taken the lead in opening up breakthrough opportunities. According to the corporate client list, this chip has entered the supply chain system of Industrial and Commercial Bank of China and China Merchants Bank.

In banking transaction system tests, it achieves microsecond-level response for encryption delays while optimizing the server cluster PUE value to 1.12. These data are benchmarked in the financial industry, providing strong support for the safe and efficient development of financial technology.

2. Government Cloud Applications

Government cloud applications validate privacy computing capabilities. The Shenzhen Nanshan government cloud platform adopts the Jianbo Micro solution, supporting cross-system data sharing for 23 departments.

The built-in privacy computing engine of the chip ensures that data is “available but invisible” during joint modeling processes, significantly reducing compliance risks for government data and safeguarding the construction of government information systems.

3. Industrial Internet

The industrial internet expands application boundaries. Haier’s smart factory embeds the chip into industrial gateways, achieving end-to-end encrypted transmission of production data.

Cooperation cases show that this solution effectively prevents data tampering of devices, providing a secure foundation for intelligent manufacturing and promoting deeper industrial digital transformation.

4. Collaborative Localization Practice

Chip autonomy is by no means a single-point breakthrough. Jianbo Micro’s industrialization path relies on deep ecological collaboration:

1. Manufacturing Stage

The manufacturing stage addresses key bottlenecks. The 28nm process from SMIC is used to achieve mass production of chips, relying on the mature processes of domestic foundries to ensure supply chain security.

The packaging and testing stage collaborates with Changjiang Electronics Technology to develop advanced 2.5D solutions, integrating core technologies such as bump processing to ensure high quality and stability of the chips.

2. Software Ecosystem

The software ecosystem builds an open system. The open-source core encryption algorithm library provides 327 national cryptographic standard interfaces, attracting over 200 developers to participate in ecosystem construction.

The algorithm acceleration platform co-built with Tencent Cloud enhances the efficiency of SM9 signature verification by five times, creating favorable conditions for the efficient development and deployment of software applications.

3. Standardization Construction

Standardization construction holds the power of rule discourse. As a major participating unit, Jianbo Micro is involved in the formulation of five national standards, including the “Technical Specifications for Server Encryption Chips”, promoting the inclusion of Chinese technical solutions in the international standard system through the RISC-V International Foundation, enhancing China’s international influence in the chip field.

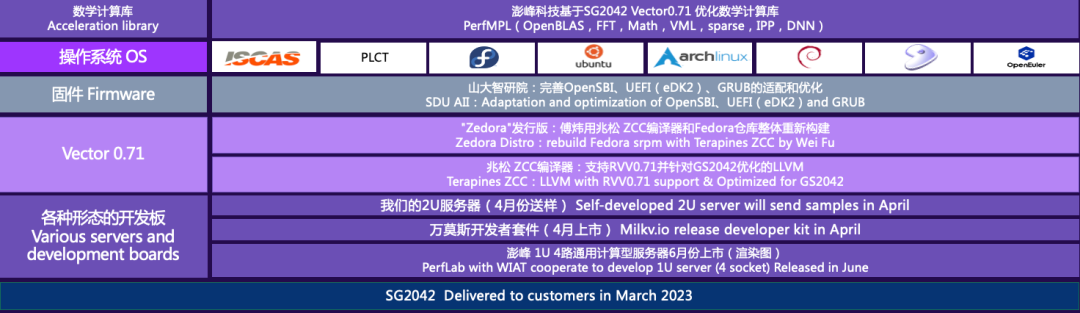

(RISC-V Computing Ecosystem)

5. Technical Coordinates for Future Journeys

The technical evolution route of Jianbo Micro has clearly anchored: advancing the mass production of 7nm quantum-resistant chips by 2026 and breaking through automotive-grade server chip certification by 2027.

These plans resonate with the progress of domestic semiconductor processes—SMIC’s 28nm process yield has surpassed 95%, and Changjiang Electronics Technology’s 2.5D packaging technology has reached international standards.

In the context of global competition, Jianbo Micro’s practices have industry implications: the RISC-V architecture is not only a technical alternative but also a strategic fulcrum for reconstructing the industrial ecosystem. As data sovereignty becomes a focal point of national competition, this comprehensive autonomy from instruction set to application ecosystem is reshaping the security gene of China’s computing power infrastructure.

It is believed that in the future, Jianbo Micro will continue to uphold the spirit of innovation, making greater contributions to the cause of domestic computing power security and pushing China’s chip industry to new heights.