🚀 In-Depth Analysis of MIPI M-PHY: The High-Speed Data Highway of Mobile Connectivity!

🚀 In-Depth Analysis of MIPI M-PHY: The High-Speed Data Highway of Mobile Connectivity!

📱 Mobile devices are becoming increasingly competitive: faster response times, higher definition videos, and smoother application experiences—achieving all this is a “low-key giant” shining behind the scenes: MIPI M-PHY. Today, we will dissect how it achieves a perfect balance between “speed” and “energy efficiency” from architecture, speed, power-saving mechanisms to burst transmission!

🔧 What is M-PHY? A One-Sentence Understanding

It is a serial physical layer interface standard used for high-speed communication between chips (such as application processors and cameras, UFS storage, 5G RF modules, etc.). You can think of it as:

A "light-speed express lane" between chips—fast, stable, and energy-efficient.🧱 Architectural Highlights: Modularity is Key!

The core of the M-PHY architecture lies in its modularity, as shown in the diagram (not included, can be illustrated):

- Channel: Each channel is independent, containing M-TX (transmit) or M-RX (receive).

- Lane Manager: After combining multiple channels, it is used for alignment and clock compensation.

- Sub-Link: A sub-link (upstream or downstream) that can contain multiple channels.

- Clock Source: Generally uses PLL to provide clock, with high precision and low jitter.

🧠 Insight: This design allows the system to be flexibly scalable—if you need more speed, just add a few more “lanes,” making it flexible and easy to manage!

⚡ High-Speed Gear Levels Explained

The high-speed operation of M-PHY is not a fixed rate, but divided into “gears” (referred to as Gear):

| Gear | Rate (Mbps) | Remarks |

|---|---|---|

| Gear 1 | ~1248 | Entry-level |

| Gear 2 | ~2496 | Mainstream speed |

| Gear 3 | ~5824 | High-end flagship configuration |

Gears are further divided into Rate A / B, corresponding to different encoding/calibration methods, giving engineers a flexible balance between performance and power consumption.

📌 Formula: The rate offset tolerance is:

⏰ Clock Strategies: Synchronous vs. Plesiochronous

MIPI M-PHY has two clock modes:

- Mesochronous: Both ends have the same clock frequency but different phases.

- Plesiochronous: Both ends have their own independent clocks, with frequencies close but not completely consistent.

This also determines:

- Type-I supports plesiochronous, suitable for long distances (e.g., adding an optical module).

- Type-II uses a shared clock, suitable for PCB direct connections.

🧠 Insight: The plesiochronous mode can save wiring and pins, making it very suitable for SoC designs; however, the recovery capability of CDR becomes crucial!

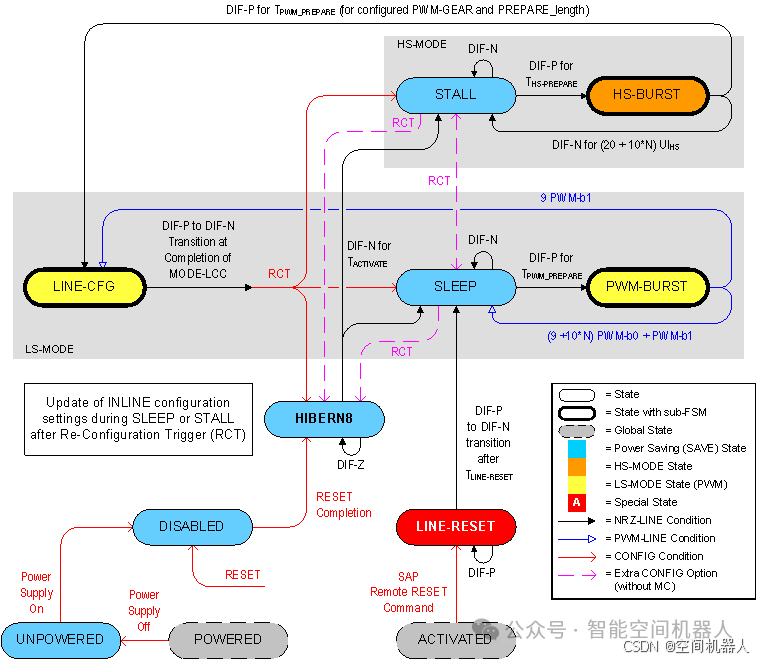

💤 Multi-Level Low Power States

M-PHY does not “foolishly keep the lights on waiting for you” when not transmitting data—it has a rich set of low power mechanisms, as shown:

Power on: Disable → Hibern8 → LS Mode → HS Mode

↘ ↑ ↖

Sleep / Stall / Idle| State | Power Consumption | Recovery Time | Applicable Scenarios |

|---|---|---|---|

| Hibern8 | Ultra-low power | ~100us-1ms | Application with long periods of no data |

| Stall | Low power | ~ns level | Pause data in HS mode |

| Sleep | Medium power | ~us level | Idle in LS mode |

💡 Tip:

<span>Stall</span>is a fast power-saving state exclusive to HS, with very quick switching.<span>Hibern8</span>is like “deep sleep,” but configuration is retained, suitable for standby scenarios.

⚡ Bursting: Finish Strong!

The most ingenious design is—Burst Transmission (Burst Mode):

Imagine a scenario where you want to say a lot but don’t want to keep the microphone on, so you speak quickly and then turn it off—that’s the charm of Bursting.

M-PHY is “speaking while turning off”:

Start Transmission

High-Speed Data Sending

Immediately Enter Stall

Recovery Wait

This way, energy is not wasted on “idle spinning,” and each “burst” only requires a few symbol cycle overheads to restart.

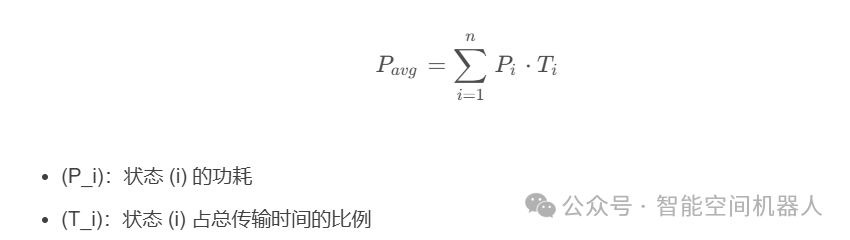

🔋 How to Calculate Average Power Consumption?

This is one of the most critical formulas during SoC development:

🧠 Insight: During design, dynamic planning must be done between transmission requirements and power consumption budgets to avoid blindly pursuing Gear 3, which can lead to overheating!

🧑🏫 Conclusion: Why is M-PHY So Desirable?

✅ Flexible rates, supporting multiple Gear levels✅ Rich power-saving mechanisms, capable of deep sleep and quick wake-up✅ Burst transmission perfectly fits the IO mode of mobile devices✅ Type-I / Type-II meet different needs for short and long distances✅ Aligns with mainstream protocols like USB4/SSIC/PCIe

📚 Postscript: Future Trends?

With the development of protocols like PCIe 5.0 / USB4 / UFS4.0, the importance of M-PHY will only increase. Low power + high speed + configurability is the core demand of all future interface designs, and MIPI M-PHY hits the mark.