The PMU is the power management unit responsible for supplying power to the SOC, regulating voltage and current to ensure that various modules operate normally. Power integrity ensures that the Power Distribution Network (PDN) can provide stable and clean voltage and current, avoiding noise interference with the normal operation of the SOC.

So what exactly does power noise refer to? It may include voltage fluctuations, high-frequency noise, ground bounce, etc. These noise sources may come from the PMU’s own switching noise, such as the switching operations of DC-DC converters, or other external factors, such as load transient changes, PCB layout issues, and so on.

Next, we need to consider how PMU power noise is transmitted to the SOC. The PMU typically powers the SOC through power rails; if the voltage output from the PMU has noise, this noise will propagate through the power network to various parts of the SOC. There may be multiple power domains within the SOC, and different modules have varying sensitivities to power noise. For example, digital circuits may tolerate high-frequency noise to some extent, but analog circuits such as ADCs and PLLs are very sensitive to noise and are easily disturbed.

If power integrity is compromised, it may lead to various problems in the SOC, such as timing errors, reduced signal integrity, increased bit error rates, and even system crashes. Therefore, noise control of the PMU is crucial for the stable operation of the SOC.

Next, we will analyze the specific mechanisms of influence. For instance, whether the PMU’s switching frequency overlaps with the SOC’s sensitive frequency bands. If the frequency of the PMU’s switching noise is close to the operating frequency of certain circuits within the SOC, it may cause resonance, amplifying the noise impact. Additionally, the impedance characteristics of the power distribution network are also important; if the PDN has high impedance at high frequencies, the noise voltage will be greater, leading to unstable power supply voltage for the SOC.

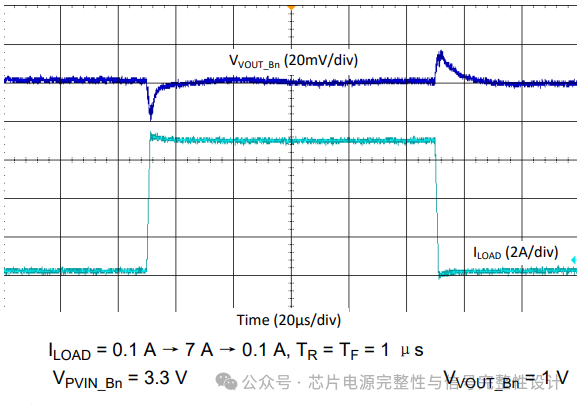

We also need to consider the PMU’s load transient response. When the SOC’s load suddenly changes, for example, switching from low-power mode to high-performance mode, the PMU needs to quickly adjust the output voltage to maintain stability. If the PMU’s response speed is not fast enough, or if overshoot or undershoot occurs during the transient response, this will cause voltage fluctuations, affecting the power integrity of the SOC.

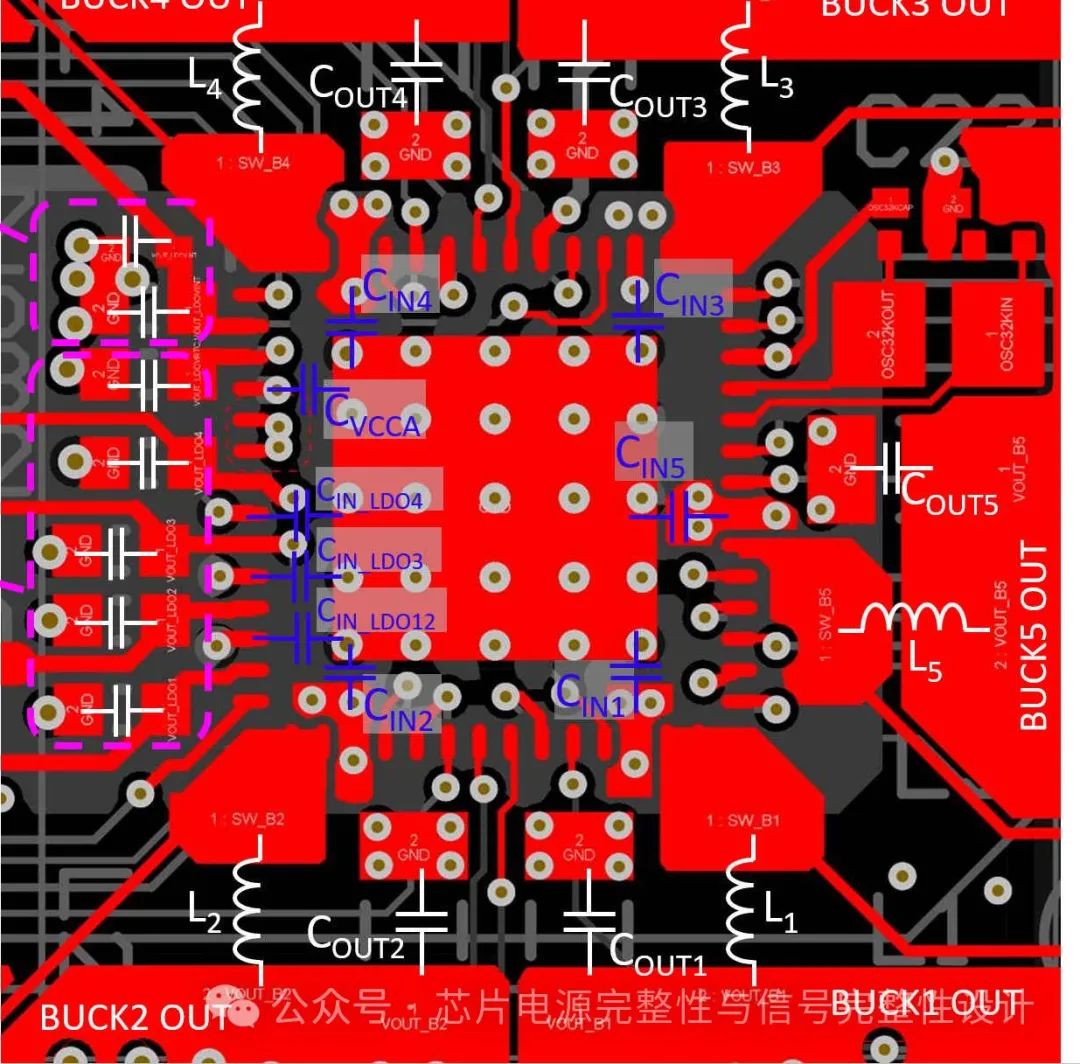

Furthermore, PCB layout and packaging design can also affect noise transmission. For example, whether the power path between the PMU and SOC is short enough, whether there are sufficient decoupling capacitors, and whether the ground plane design is good; all these factors may affect the propagation and suppression of noise.

Possible solutions include optimizing the PMU design, such as using more efficient DC-DC converter topologies, increasing filter capacitance, and improving feedback control loops to enhance transient response. Additionally, at the SOC end, it may be necessary to design a more robust power distribution network, reasonably arrange decoupling capacitors, use power isolation techniques, and conduct thorough power integrity simulations and testing.

At the same time, attention should be paid to some chip details, such as whether the SOC’s sensitivity to power noise varies across different process nodes, or the collaborative design strategies between the PMU and SOC, such as how Dynamic Voltage Frequency Scaling (DVFS) affects power noise and integrity. Furthermore, thermal effects may also impact power noise; temperature changes can cause performance drift in the PMU, thereby affecting the stability of the output voltage.

We also need to consider the methods for testing and measurement, how to accurately measure the noise output from the PMU in an actual system, and how to assess the impact of this noise on the SOC. This may require using tools like oscilloscopes and spectrum analyzers to conduct time-domain and frequency-domain analyses.

Below, we will conduct a comprehensive analysis from the mechanisms of noise generation, propagation paths, impacts on the SOC, design optimization methods, and more, to ensure coverage of key points and provide effective solutions.

The impact of PMU (Power Management Unit) chip power noise on SOC (System on Chip) power integrity (PI) involves multiple levels and requires a systematic analysis from noise generation mechanisms, propagation paths, SOC sensitivity, and mitigation strategies. The following is an in-depth discussion:

1. Mechanisms and Sources of PMU Power Noise Generation

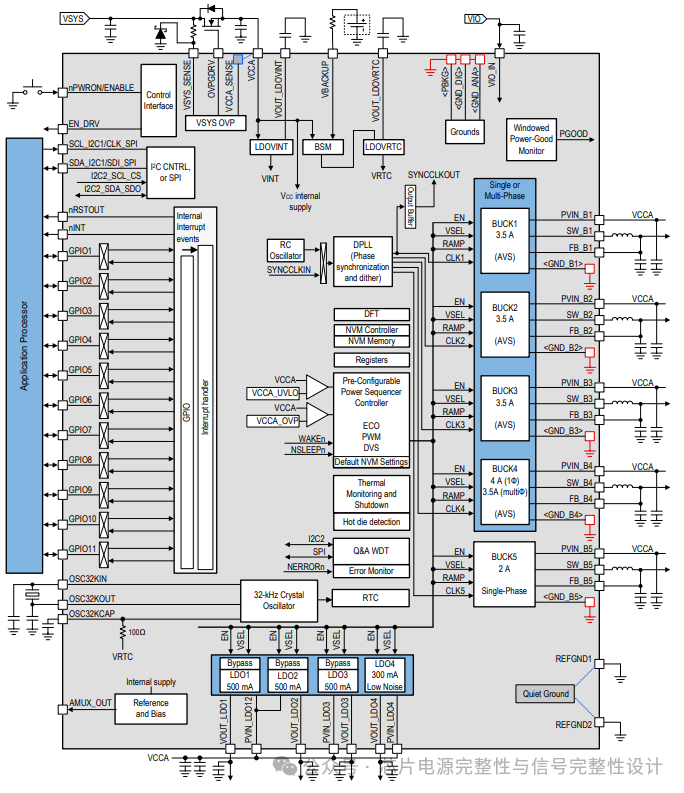

The key internal modules of the PMU (such as DC-DC converters, LDOs, etc.) are the main sources of noise:

· Switching Noise: The switching actions of Buck/Boost converters lead to high-frequency ripple (hundreds of kHz to MHz), with its magnitude related to switching frequency, inductor/capacitor parameters, and load current.

· Ground Bounce and Crosstalk: Rapidly switching currents (di/dt) cause ground bounce noise, which couples into the SOC power network through common-mode paths.

· Load Transient Response: Dynamic load changes in the SOC (such as CPU burst operations) can lead to instantaneous voltage drops (Undershoot) or overshoots (Overshoot) in the PMU output, and insufficient transient recovery time can exacerbate noise.

· Thermal Noise and Device Nonlinearity: Thermal noise generated by the PMU’s internal MOSFET on-resistance, inductive core losses, and harmonic distortion caused by nonlinear components.

2. Impact of Power Noise on SOC Power Integrity

2.1 Direct Effects

· Voltage Domain Stability: PMU output noise directly adds to the SOC power rails; if it exceeds the tolerance range (e.g., ±3% of the rated voltage), it may lead to logical errors or functional failures.

· Timing Violations: Power noise causes clock jitter and variations in logic gate delays, which may violate setup/hold times in high-frequency designs.

· Degradation of Analog Circuit Performance: Modules such as PLLs, ADCs/DACs are sensitive to power noise, which may increase phase noise and decrease signal-to-noise ratio (SNR).

2.2 Indirect Effects

· Signal Integrity (SI) Coupling: Power noise couples into signal lines through PDN impedance, leading to crosstalk and increased bit error rates (BER), with signal jitter introduced by power affecting high-speed signal timing margins, resulting in interface AC timing violations, especially as the speed of storage class high-speed interfaces increases, the demand for power quality becomes more stringent.

· Electromagnetic Interference (EMI): High-frequency noise interferes with surrounding circuits through radiation or conduction pathways, potentially causing system-level EMC issues.

3. Noise Propagation Path and PDN Impedance Analysis

3.1 Transmission Paths

· Conductive Path: The power network from the PMU output to the SOC (PCB traces, package interconnections, on-chip metal layers) constitutes the main conductive path, and its impedance characteristics (Z(f)) determine the extent of noise attenuation.

· Radiation Path: High-frequency noise couples to nearby sensitive circuits through space, necessitating attention to PCB layout and shielding design.

3.2 Key Frequency Bands of PDN Impedance

· Low Frequency (<1MHz): Dominated by decoupling capacitors and PCB plane capacitance, ensuring sufficient capacitance value to suppress low-frequency ripple.

· Mid Frequency (1MHz~100MHz): Package and on-chip capacitance play a major role; capacitance distribution and ESL (Equivalent Series Inductance) need optimization.

· High Frequency (>100MHz): On-chip capacitance and metal layer RC networks dominate; the use of on-chip nanoscale capacitors (such as MOS capacitors) is necessary to reduce impedance.

4. Design Optimization and Noise Suppression Strategies

4.1 PMU-side Optimization

· Topology Selection: Use multiphase Buck converters to spread the switching noise spectrum, or use LDOs to supply power to noise-sensitive modules.

· Dynamic Response Enhancement: Optimize compensation networks (such as Type III compensators) to improve load transient response speed and reduce voltage drops.

· Synchronization Rectification and Soft Switching Techniques: Reduce switching losses and di/dt noise.

· Select Appropriate Low-Frequency Transient LC Combinations:Reduce transient switching noise.

4.2 PDN Design

· Impedance Design: Optimize the PDN impedance curve through frequency domain simulation (e.g., ANSYS SIwave) to ensure Z(f) is below the target impedance (Ztarget) in the target frequency bands.

· Decoupling Strategy: Use a mix of large-capacity electrolytic capacitors (low frequency), ceramic capacitors (mid frequency), and embedded capacitors (high frequency) to design a capacitor combination that covers the entire frequency range, ensuring physical design can shorten current loops.

4.3 SOC-side Reinforcement

· Power Domain Isolation: Digitally and analog power domains are powered independently, with deep well isolation or Guard Rings inside the chip to reduce coupling; external digital and analog power use their respective digital or analog grounds for isolation, reducing mutual interference. If digital and analog are combined, ensure that the total noise of each meets their respective power noise requirements.

· Adaptive Voltage Scaling (AVS): Dynamically adjust voltage based on workload to reduce static noise margin requirements.

4.4 System-level Collaborative Design

· Timing Analysis and Collaborative Simulation: Combine power noise models with timing analysis tools (such as PrimeTime) to evaluate the marginal impact of noise on timing.

· EMI/EMC Design: Optimize PCB stacking, power segmentation, and filtering circuits to suppress common-mode noise radiation.

5. Understanding Future Challenges and Trends

· Advanced Process Nodes: The thin oxide layers below 3nm are more sensitive to voltage fluctuations, necessitating stricter noise tolerance designs.

· Chiplet Technology: The cross-package noise coupling mechanisms between PMU and SOC become more complex under multi-chip integration, requiring 3D PDN collaborative optimization.

· AI-driven Design: Utilize machine learning algorithms to quickly iterate PDN parameters, achieving Pareto optimality between noise and energy efficiency.

The impact of PMU power noise on SOC power integrity runs throughout the entire process from chip design to system integration. It requires multi-physical field collaborative simulation, PDN impedance optimization, and system-level noise suppression technologies to achieve a balance between energy efficiency and stability. In the future, as process evolution and application scenarios become more complex, cross-level collaborative design and intelligent optimization tools will become key breakthroughs.