Introduction

Overview

Today, we continue to share typical cases from one of the Ivy League schools—Cornell University’s FPGA course ECE 5760: A Chirikov Standard Mapping Solver based on the DE1-SOC development board.

(For more other cases, please refer to the website:

https://people.ece.cornell.edu/land/courses/ece5760/FinalProjects/)

1. Project Overview

Project Website

https://people.ece.cornell.edu/land/courses/ece5760/FinalProjects/s2024/hwm44_mck65/index.html

Project Description

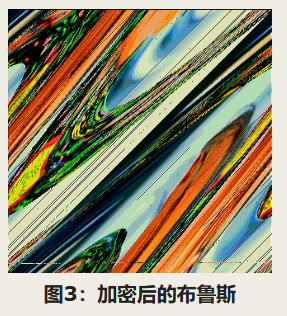

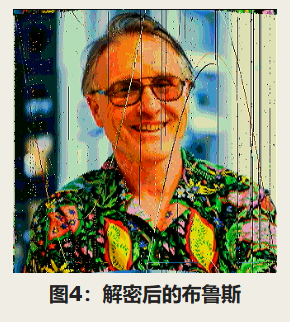

This project implements a Chirikov standard mapping solver on the Altera DE1-SOC development board and applies it to a proof of concept for image encryption and decryption.

2. Chirikov Standard Mapping Solver Model

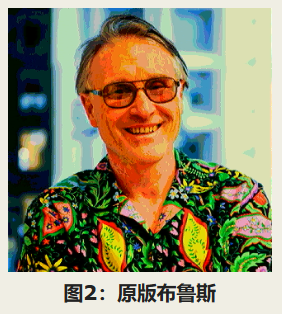

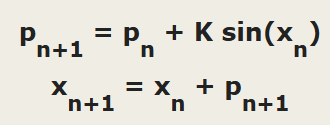

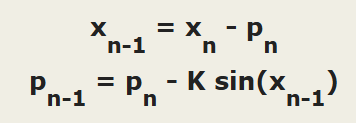

The solver model for the Chirikov standard mapping was first introduced by Boris Chirikov in 1969. The standard mapping is a discrete-time Hamiltonian dynamical system described by the following set of equations:

And the inverse mapping equations are described as:

This reversibility allows us to utilize the standard mapping for encryption/decryption schemes. (For more detailed descriptions, please refer to the project website.)

3. Engineering Design

The project includes designs for both the FPGA side and the HPS side.

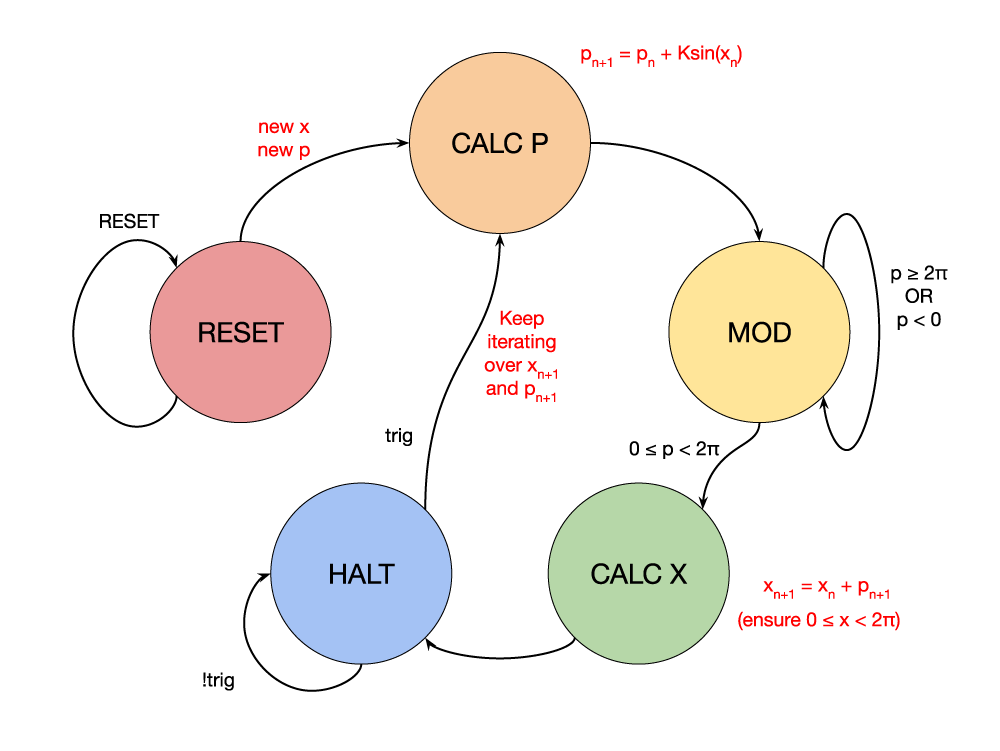

First, the iterator is implemented on the FPGA, as this computation can be easily realized through a state machine.

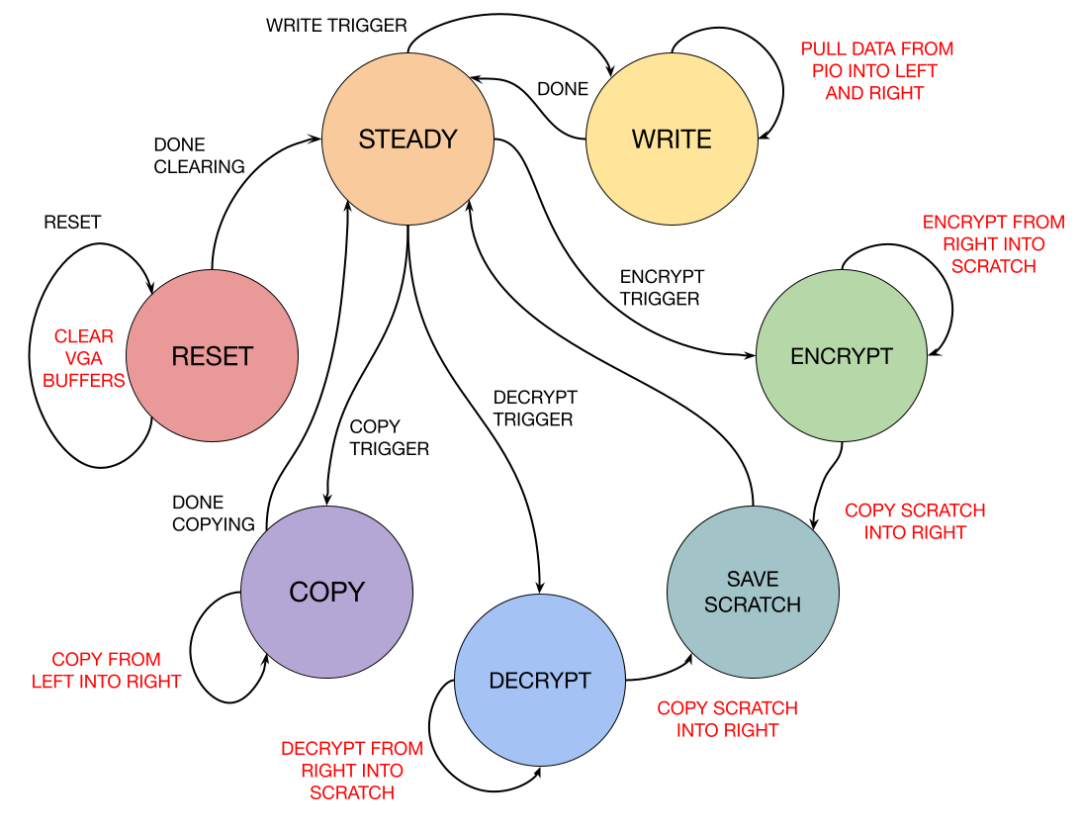

Additionally, a second state machine is implemented in the FPGA, connected to an M10k block with a VGA memory of 640×480 elements and 8 bits wide. This state machine controls the iterator and writes to memory as instructed.

On the HPS (ARM Cortex-A9 hard IP), the top-level state machine is primarily controlled through the PIO channel to manage input and output to the iterator. The project includes three programs: the first is an interactive demonstration that uses a multithreaded program to poll mouse input and trigger the iterator; the second is an automated demonstration that removes mouse event polling and uses an automated nested loop to iterate K and select 100 pseudo-random points; the third is an encryption demonstration where the C program is modified to send only pixel data to the FPGA for writing images. This program uses command line parameters to set various parameters.

4. Video Demonstration

Click the border to bring up the video toolbar The following video is sourced from Terasic

5. Source Code Download

https://people.ece.cornell.edu/land/courses/ece5760/FinalProjects/s2024/hwm44_mck65/index.html

(See the content of the link forAppendix C: Program Listing)

Previous Readings:FPGA Open Source Project Sharing—String Art Implementation Based on DE1-SOCFPGA Open Source Project Sharing—FPGA Accelerated Heat Diffusion SimulatorFPGA Open Source Project Sharing—2D N-Body Gravity SimulatorFPGA Open Source Project Sharing—Dijkstra Algorithm Implementation for China Railway NetworkGitHub Open Source Project Introduction—HDMI Design Based on DE10-Nano