RISC-V (pronounced “risk-five”) is an open-source instruction set architecture (ISA) based on the principles of Reduced Instruction Set Computing (RISC), which can be simply explained as a type of “open-source hardware” corresponding to the open-source software movement. The project began in 2010 at the University of California, Berkeley, but many contributors are volunteers and industry professionals from outside the university. Compared to most instruction sets, the RISC-V instruction set can be freely used for any purpose, allowing anyone to design, manufacture, and sell RISC-V chips and software without paying patent fees to any company. Although it is not the first open-source instruction set, it is significant because its design makes it suitable for modern computing devices. The designers considered performance and power efficiency for these applications. The instruction set also has a wealth of supporting software, addressing the common weaknesses of new instruction sets.

RISC-V (pronounced “risk-five”) is an open-source instruction set architecture (ISA) based on the principles of Reduced Instruction Set Computing (RISC), which can be simply explained as a type of “open-source hardware” corresponding to the open-source software movement. The project began in 2010 at the University of California, Berkeley, but many contributors are volunteers and industry professionals from outside the university. Compared to most instruction sets, the RISC-V instruction set can be freely used for any purpose, allowing anyone to design, manufacture, and sell RISC-V chips and software without paying patent fees to any company. Although it is not the first open-source instruction set, it is significant because its design makes it suitable for modern computing devices. The designers considered performance and power efficiency for these applications. The instruction set also has a wealth of supporting software, addressing the common weaknesses of new instruction sets.

The CPU architecture has traditionally been dominated by x86 and ARM, but since the birth of RISC-V in 2010, there has been a subtle trend towards a three-way competition in CPU architecture:

X86: The mainstream in the traditional PC market, adept at handling large data, with IP controlled by Intel and AMD.

ARM: The mobile (smartphone) market, primarily handling fast data, and is now also used in portable laptops, with most IP controlled by ARM Holdings.

RISC-V: When both data transfer speed and volume need to be considered, the capabilities of these two mainstream architectures are limited. RISC-V shows strong advantages.

Currently, all general-purpose x86 architecture processor technologies are controlled by Intel and AMD, whileARM (Advanced RISC Machines) is a semiconductor design company headquartered inCambridge, UK, with its legal status and historical origins clearly pointing to the UK. Intel and AMD are American companies, and ARM is essentially a follower of American interests, existing as a dominant force in the chip field. They are not open-source; it is said that chip designers must pay fees to access their literature online, let alone the licensing fees that are often required, as they set the industry standards. They exist at the top of the food chain.

RISC-V represents an opportunity for domestic chip independence to make a significant leap forward.

Compared to most instruction sets, the RISC-V instruction set can be freely used for any purpose, allowing anyone to design, manufacture, and sell RISC-V chips and software and demonstrating unique advantages in architectural simplicity and modularity.

Advantages of RISC-V:

1. Modularity: RISC-V organizes different parts in a modular way and attempts to meet various application scenarios through a unified architecture, a modularity that x86 and ARM architectures do not possess.

2. Fewer instructions: Benefiting from its concise architecture and modular characteristics, the number of instructions in the RISC-V architecture is very simple. The basic RISC-V instruction set has only over 40 instructions, and with other modular extension instructions, there are only a few dozen instructions in total.

3. RISC-V is fully open-source and has a complete set of open-source free compilers, development tools, and software development environments (IDEs), allowing any user to freely modify and extend it to meet customized needs, significantly lowering the barriers to modifying the instruction set.

Applications of RISC-V:1. IoT (Internet of Things), connecting everything.2. Mobile market, expected to fully replace ARM’s position in the smartphone market.3. Server market, high-performance computing chips.4. Storage market, driven by big data technology demands.5. AI (Artificial Intelligence) market.6. Automotive electronics field. RISC-V Ecosystem DevelopmentGlobally, the RISC-V Foundation has over 4,000 members across more than 50 countries, forming a complete layout from IP, design, application, to terminal manufacturers. China is an important participant, with major tech companies like Alibaba’s Pingtouge, Huawei, and specialized IP suppliers like Chipone Technology, as well as SoC chip designers like Sifive and Ruisi Semiconductor.

RISC-V Ecosystem DevelopmentGlobally, the RISC-V Foundation has over 4,000 members across more than 50 countries, forming a complete layout from IP, design, application, to terminal manufacturers. China is an important participant, with major tech companies like Alibaba’s Pingtouge, Huawei, and specialized IP suppliers like Chipone Technology, as well as SoC chip designers like Sifive and Ruisi Semiconductor.

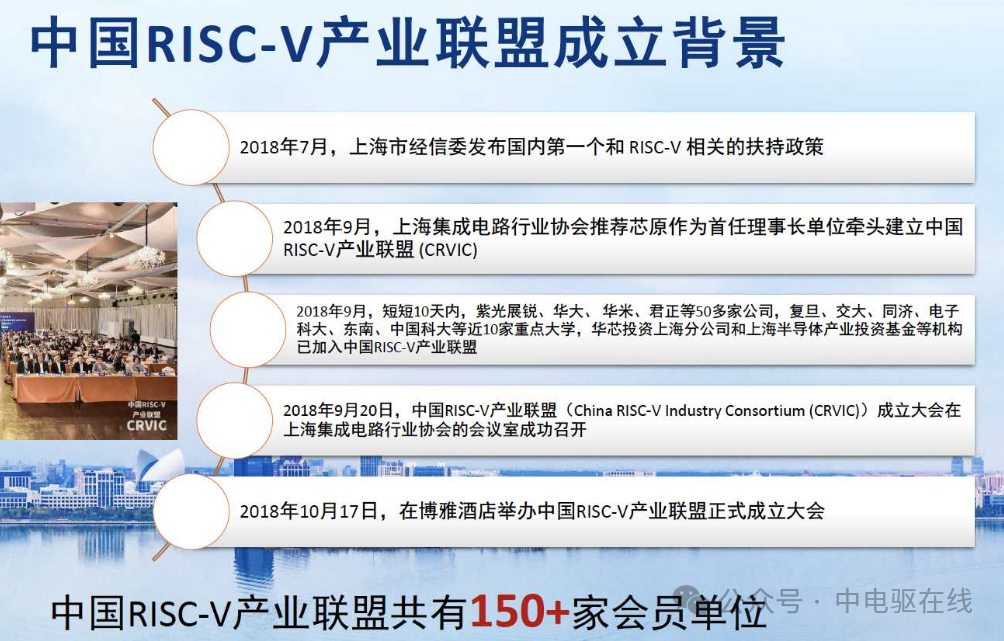

On October 17, 2018, the founding conference of the China RISC-V Industry Consortium (CRVIC) was successfully held at the Shanghai Integrated Circuit Industry Association meeting room in Zhangjiang. It attracted many organizations to join, including Chipone Technology, Sifive, Hangzhou Zhongtian Micro, Beijing Junzheng, GigaDevice, and Unisoc, with Chipone Technology serving as the first chairman unit of the consortium.

The establishment of the consortium aims to build an industry exchange platform, promote the widespread application of RISC-V; foster RISC-V talent development and establish university training programs; promote collaborative development among members and establish long-term cooperation mechanisms; and undertake activities of the RISC-V global foundation to deepen international cooperation and exchange.

From the current shipment of hundreds of billions of RISC-V chips, we can see that RISC-V has already established a foothold in embedded systems, IoT, and edge computing.

In the consumer electronics products we encounter daily, it is very likely that RISC-V IP cores have already been used.

From the strength of China, we are gradually transforming from followers to rule-makers. To avoid bottlenecks in semiconductor processes, we must also participate in standard-setting at the upstream design and development end to become global top players and establish ourselves as a strong chip nation. The road ahead is long, but we will get there!

Thank you for reading, liking, and following! China Electronics Online grows with you!