Reported by Electronic Enthusiasts Network (Author: Zhou Kaiyang) When many people hear about RISC-V, the first thing that comes to mind is its applications in IoT and consumer electronics, as well as various low-power market opportunities. Although RISC-V has previously appeared in supercomputers or data centers, and in GPU solutions, it has often served merely as an accelerator or a “glue” in heterogeneous systems. As an architecture that has been gaining momentum in recent years, RISC-V’s ambitions naturally do not stop there. Recently, RISC-V has made several significant moves, preparing to fully enter the AI and automotive markets, and has even enlisted the legendary Jim Keller to endorse it, further accelerating RISC-V’s expansion.

Semiconductor Veteran Jim Keller Chooses RISC-V as the Core for AI Chips

Many friends familiar with major semiconductor companies have likely heard of the legendary engineer Jim Keller. He has worked at AMD, Apple, Tesla, and Intel, participating in the design of chip systems and architectures such as AMD K8, K7, Zen, Apple A4, A5, and Tesla HW 3.0. At the same time, he is also one of the authors of the x86-64 instruction set specification, and Jim Keller’s design experience spans both RISC and CISC instruction sets. However, in June 2020, Jim Keller, then a senior vice president at Intel, voluntarily submitted his resignation. Rumors suggested that the reason for his departure was a disagreement over the company’s plan to outsource more production. In January of this year, Jim Keller joined an AI chip startup, Tenstorrent, as CTO. The company’s CEO is also a long-time friend of Jim Keller, Ljubisa Bajic, who served as a chip architect at AMD for many years. Coinciding with the Linley Spring Processor Conference this month, Tenstorrent announced that it has obtained a license for SiFive’s general-purpose RISC-V CPU design. Founded in 2016, the company will utilize SiFive’s newly launched Intelligence X280 64-bit RISC-V core to design a SoC.

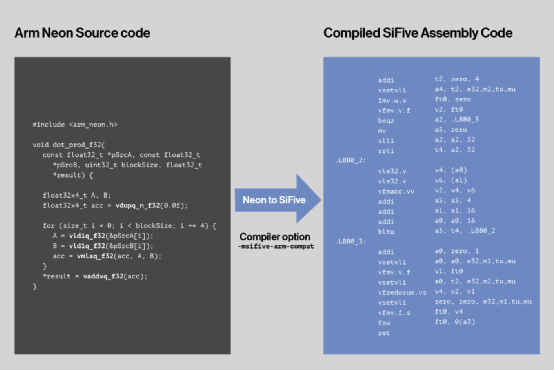

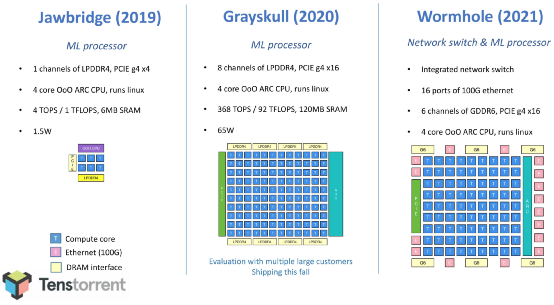

Arm Code Translated to SiFive Assembly Code / SiFive Intelligence is SiFive’s newly launched AI/machine learning product line, providing software and hardware integration solutions through SiFive’s AI architecture expansion and RISC-V vector extension. The Intelligence X280 is based on SiFive’s 64-bit U7 series RISC-V core and features an 8-stage pipeline design. According to data released by SiFive, the AI extension of Intelligence can reduce execution time to one-twelfth, and SiFive has prepared tools for engineers to directly compile Arm Neon-based code into SiFive’s assembly code. Tenstorrent Machine Learning Processor Roadmap / Tenstorrent Tenstorrent has begun mass production of its second-generation machine learning processor, Grayskull, this year. This processor uses another RISC architecture, ARC, as its CPU core, which Tenstorrent has named Tensix, utilizing GLOBALFOUNDRIES’ 12nm process. The choice of a RISC-V core is likely a decision made after Jim Keller’s arrival. In an interview with HPCwire this year, Jim Keller mentioned that although many startups are beginning to develop and design AI chips, he has also discovered their frustrations in discussions with customers. One of these frustrations is the supporting software; many AI chip companies’ primary goal is to launch high-performance chips, using GFLOPS or TFLOPS as selling points, and then design software afterward. In contrast, Tenstorrent has been designing software and hardware in parallel from the beginning, with a software team that includes members from various compiler and CAD tool backgrounds, including Altera. Although Tenstorrent has not disclosed specific parameter details for its third-generation processor, Wormhole, and the fourth-generation processor currently in design, it is clear that the general processing, vector processing capabilities, and software ecosystem of RISC-V are what Tenstorrent values. The new Tenstorrent processors will also adopt a heterogeneous design, with Tensix handling the main neural network tasks, while Intelligence X280 will be used for application code integration, vector operations, and general computing tasks.

Tenstorrent Machine Learning Processor Roadmap / Tenstorrent Tenstorrent has begun mass production of its second-generation machine learning processor, Grayskull, this year. This processor uses another RISC architecture, ARC, as its CPU core, which Tenstorrent has named Tensix, utilizing GLOBALFOUNDRIES’ 12nm process. The choice of a RISC-V core is likely a decision made after Jim Keller’s arrival. In an interview with HPCwire this year, Jim Keller mentioned that although many startups are beginning to develop and design AI chips, he has also discovered their frustrations in discussions with customers. One of these frustrations is the supporting software; many AI chip companies’ primary goal is to launch high-performance chips, using GFLOPS or TFLOPS as selling points, and then design software afterward. In contrast, Tenstorrent has been designing software and hardware in parallel from the beginning, with a software team that includes members from various compiler and CAD tool backgrounds, including Altera. Although Tenstorrent has not disclosed specific parameter details for its third-generation processor, Wormhole, and the fourth-generation processor currently in design, it is clear that the general processing, vector processing capabilities, and software ecosystem of RISC-V are what Tenstorrent values. The new Tenstorrent processors will also adopt a heterogeneous design, with Tensix handling the main neural network tasks, while Intelligence X280 will be used for application code integration, vector operations, and general computing tasks.

RISC-V Begins to Make Inroads into the Automotive Market

Renesas and SiFive Collaborate to Develop RISC-V Automotive Chips / Renesas, SiFive In addition to the AI market, RISC-V is also starting to target the automotive market. On April 22, Renesas announced that it will collaborate with SiFive to develop the next generation of high-end automotive RISC-V chip solutions. Ken Kataoka, senior vice president of Renesas Electronics and general manager of the Automotive Electronic Solutions Division, stated: “RISC-V plays an important role in providing additional features and more choices for new and existing customers. We are honored to collaborate with SiFive to leverage our years of accumulated automotive electronics technology and SiFive’s advanced RISC-V technology to develop the next generation of automotive semiconductor solutions.” This is not Renesas’s first foray into RISC-V; as early as October last year, Renesas announced a partnership with Andes Technology to utilize the AndesCore 32 as the RISC-V CPU core for application-specific standard products (ASSPs), planning to deliver samples to customers in the second half of 2021. However, these pre-programmed ASSP devices are primarily used for optimizing motor control, voice recognition, and other fields, and do not have much connection with Renesas’s strong automotive business. Renesas’s choice to collaborate with SiFive to develop automotive semiconductors also confirms that RISC-V cores can now meet the high-performance requirements for automotive applications. After all, Renesas already has its own RISC instruction set architecture, SuperH, yet still chooses to collaborate with SiFive based on RISC-V, indicating that they have recognized its advantages. Another challenge in entering the automotive market is the various stringent certifications; however, some RISC-V security IP has already passed automotive regulations. Rambus’s hardware root of trust IP, RT-645, has already received ASIL-D certification. Although this IP is only used to ensure the safety of SoCs in V2X communication, ADAS, ECU, and IVI, and is not responsible for general computing in the main CPU, it still represents an important step for RISC-V in the automotive market.

Renesas and SiFive Collaborate to Develop RISC-V Automotive Chips / Renesas, SiFive In addition to the AI market, RISC-V is also starting to target the automotive market. On April 22, Renesas announced that it will collaborate with SiFive to develop the next generation of high-end automotive RISC-V chip solutions. Ken Kataoka, senior vice president of Renesas Electronics and general manager of the Automotive Electronic Solutions Division, stated: “RISC-V plays an important role in providing additional features and more choices for new and existing customers. We are honored to collaborate with SiFive to leverage our years of accumulated automotive electronics technology and SiFive’s advanced RISC-V technology to develop the next generation of automotive semiconductor solutions.” This is not Renesas’s first foray into RISC-V; as early as October last year, Renesas announced a partnership with Andes Technology to utilize the AndesCore 32 as the RISC-V CPU core for application-specific standard products (ASSPs), planning to deliver samples to customers in the second half of 2021. However, these pre-programmed ASSP devices are primarily used for optimizing motor control, voice recognition, and other fields, and do not have much connection with Renesas’s strong automotive business. Renesas’s choice to collaborate with SiFive to develop automotive semiconductors also confirms that RISC-V cores can now meet the high-performance requirements for automotive applications. After all, Renesas already has its own RISC instruction set architecture, SuperH, yet still chooses to collaborate with SiFive based on RISC-V, indicating that they have recognized its advantages. Another challenge in entering the automotive market is the various stringent certifications; however, some RISC-V security IP has already passed automotive regulations. Rambus’s hardware root of trust IP, RT-645, has already received ASIL-D certification. Although this IP is only used to ensure the safety of SoCs in V2X communication, ADAS, ECU, and IVI, and is not responsible for general computing in the main CPU, it still represents an important step for RISC-V in the automotive market.

Conclusion

We have seen RISC-V make significant progress in several key areas, but we must also acknowledge that this new architecture has encountered challenges during its golden development period due to the semiconductor supply crisis. Many RISC-V processor IPs have not yet utilized advanced processes like 5nm, so they can only compete with ARM for orders in mature processes. Although RISC-V has the widest adoption in IoT applications, it does not mean that RISC-V has stagnated in this area. For example, Allwinner recently launched the D1 application processor based on the T-head Xuantie 906 RISC-V core, and Espressif released the world’s first RISC-V Bluetooth 5.0 and Wi-Fi 6 SoC, ESP32-C6. These are definitely significant markets where RISC-V currently holds an advantage and will be the first RISC-V chips to appear before mainstream engineers. Furthermore, more and more authoritative chip designers are beginning to pay attention to RISC-V and speak out for it. Take Jim Keller, for example. What he values is not the competition between CISC and RISC; he believes that this is the least important aspect. What matters is scalability, usability, and the development of related toolchains, and RISC-V’s achievements in these areas are evident. After all, data centers and automotive markets are also markets that ARM took years to break into. RISC-V has already taken its first step, and the real test is yet to come.

Disclaimer: This article is original to Electronic Enthusiasts Network. Please indicate the source when reprinting. For group discussions, please add WeChat elecfans999, For submission of reports or interview requests, please email [email protected].

More Hot Articles to Read

-

Biden’s $2.25 Trillion Infrastructure Plan! Strengthening the Domestic Semiconductor Supply Chain!

-

One Wafer Equals One Chip! The World’s Largest WSE-2 Processor Released! 7nm, Area of 826 mm²

-

In-Depth Observation: The Replacement of Domestic Chips is a Process, Not Just a Result

-

Domestic Automotive Chips are Getting Stronger! MCU, Power Devices, Networking Chips, and Storage Chips Flourishing

-

Fighting Hard to Build Cars! Huawei, Xiaomi, Alibaba, Evergrande, Didi, a Battle of Titans, Will It End in Chaos?