-

The interface types for cameras mainly include: MIPI CSI-2, LVDS, FPD Link, etc. -

Lidar is generally connected via standard Ethernet interfaces. -

Millimeter-wave radars transmit data via CAN bus. -

Ultrasonic radars typically use LIN bus. -

Common interfaces for combined navigation and inertial navigation IMU are RS232. -

V2X modules generally also use Ethernet interfaces for data transmission.

-

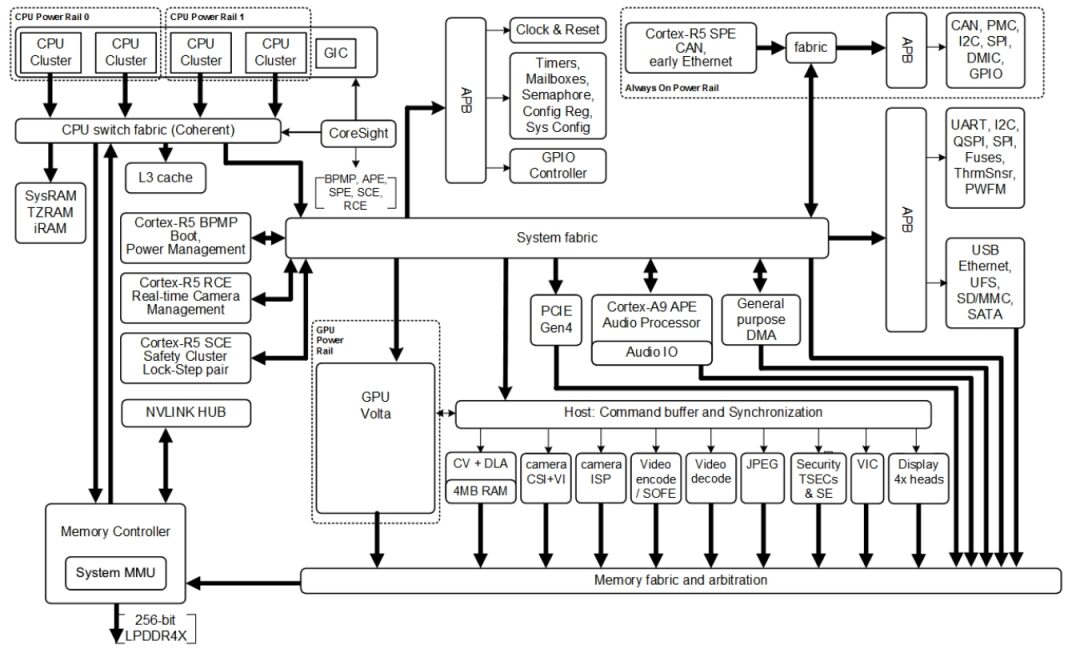

It can provide a wealth of software algorithm talent for the automotive field; -

A large number of algorithm models and related application software have been trained in the general AI field; -

A unified hardware and underlying software interface architecture (CUDA-X) can be easily ported to the automotive sector; -

Due to a large number of users, partners have contributed a wealth of libraries and tools to the CUDA platform.

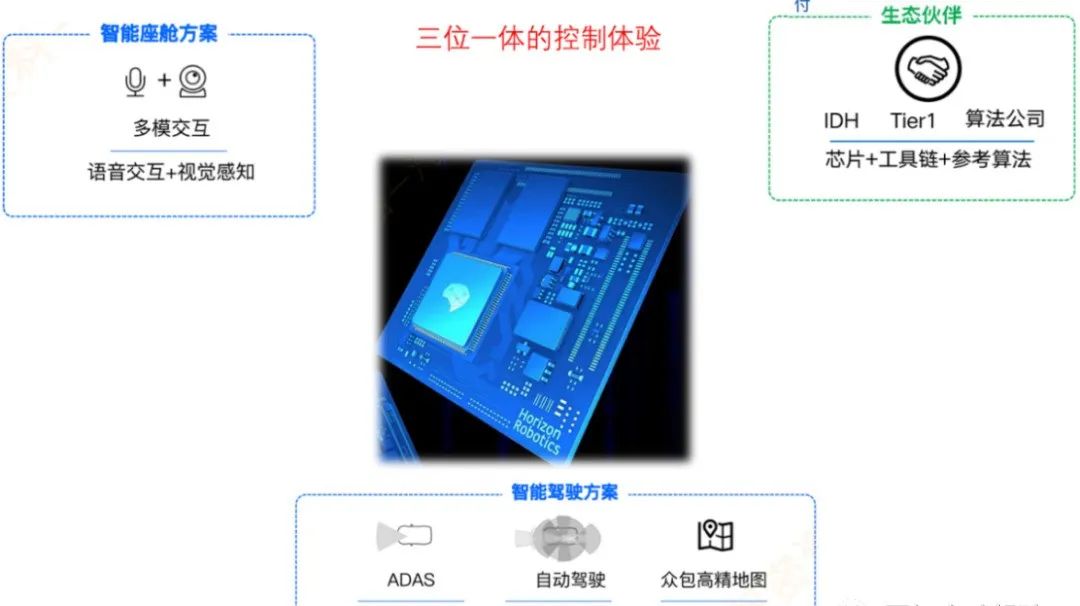

Open and Inclusive, Collaborate Hand in Hand

Share Opportunities and Achievements in Industrial Transformation