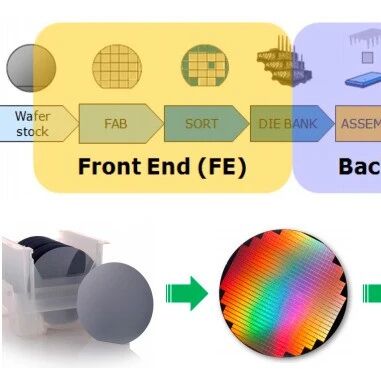

In-Depth Article: Detailed Explanation of the Chip Manufacturing Process!

“IT Chat” is a professional IT information and service platform under the Machinery Industry Press, dedicated to helping readers master more professional and practical knowledge and skills in the broad field of IT, quickly enhancing their workplace competitiveness. Click the blue WeChat name to quickly follow us. This article is reprinted from: Fresh Date Classroom … Read more