Everyone in the electronics industry has a good understanding of chips and various packages, but do you know how a chip is designed? Do you know how the designed chip is produced? After reading this article, you will have a general understanding.

Complex and Tedious Chip Design Process

The chip manufacturing process is like building a house with Lego. First, there is the wafer as the foundation, and then the chip manufacturing process builds up layer by layer to produce the necessary IC chips (which will be introduced later). However, without a design blueprint, no matter how strong the manufacturing capability is, it is useless. Therefore, the role of the architect is very important. But who exactly is the architect in IC design? This article will introduce IC design next.

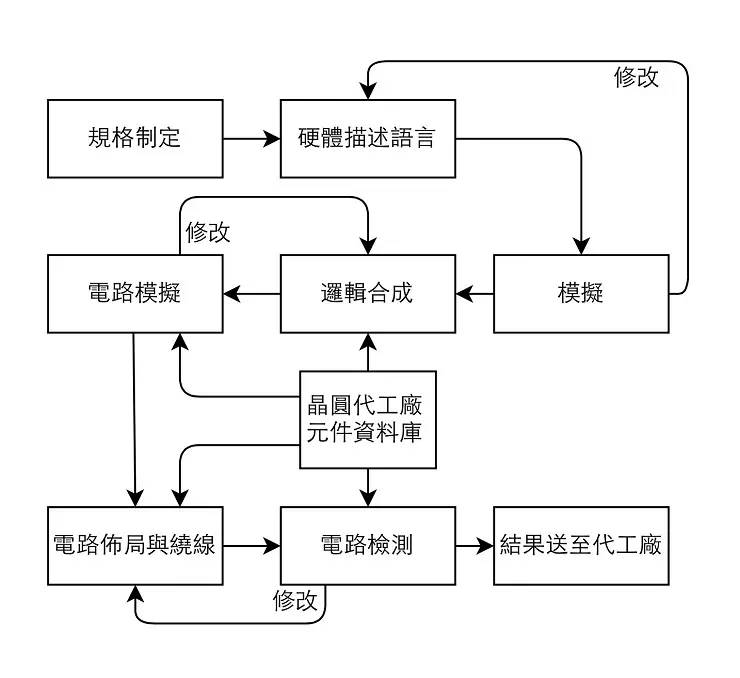

In the IC production process, ICs are typically planned and designed by professional IC design companies. Well-known companies like MediaTek, Qualcomm, and Intel design their own IC chips and provide different specifications and performance chips for downstream manufacturers to choose from. Because ICs are designed by each factory, IC design heavily relies on the skills of engineers, and the quality of engineers affects the value of a company. However, what steps do engineers take when designing an IC chip? The design process can be simply divided as follows.

Step One: Define Goals

In IC design, the most important step is specification formulation. This step is like deciding how many rooms and bathrooms to have before designing a building, and what building regulations need to be followed. After determining all functions, the design can proceed without needing to spend extra time on subsequent modifications. IC design also requires similar steps to ensure that the designed chip will not have any errors.

The first step in specification formulation is to determine the purpose and performance of the IC, setting the general direction. Next, the agreements that need to be met are checked; for example, a wireless card chip must comply with IEEE 802.11 standards, otherwise, this chip will not be compatible with products on the market, making it unable to connect with other devices. Finally, the implementation method of this IC is established, allocating different functions to different units, and establishing the connection methods between different units, thus completing the specification formulation.

After completing the specifications, the next step is to design the details of the chip. This step is like sketching the preliminary architectural plan to outline the overall profile for subsequent drawing. In IC chips, hardware description languages (HDL) are used to describe the circuits. Commonly used HDLs include Verilog and VHDL, which can easily express the functions of an IC through code. Next, the correctness of the program’s functionality is checked and modified continuously until it meets the expected functionality.

▲ Example of a 32-bit adder in Verilog.

▲ Example of a 32-bit adder in Verilog.

With Computers, Things Become Easier

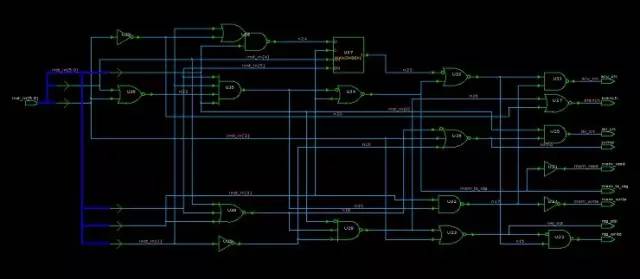

With a complete plan, the next step is to draw the flat design blueprint. In IC design, the logic synthesis step involves taking the confirmed HDL code and placing it into electronic design automation tools (EDA tools), allowing the computer to convert the HDL code into a logic circuit, producing the following circuit diagram. Afterward, repeatedly confirming whether this logic gate design diagram meets specifications and modifying it until the functionality is correct.

▲ Result after synthesizing the control unit.

▲ Result after synthesizing the control unit.

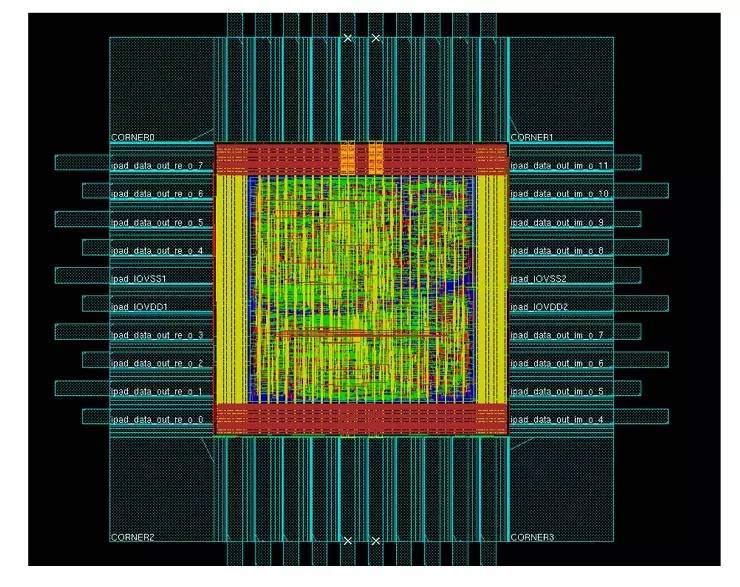

Finally, the synthesized code is placed into another set of EDA tools for circuit layout and routing (Place And Route). After continuous testing, the following circuit diagram will be formed. In the diagram, different colors such as blue, red, green, and yellow can be seen, with each color representing a different photomask. How to use these photomasks will be discussed next.

▲ Commonly used calculation chip – FFT chip, completed circuit layout and routing results.

▲ Commonly used calculation chip – FFT chip, completed circuit layout and routing results.

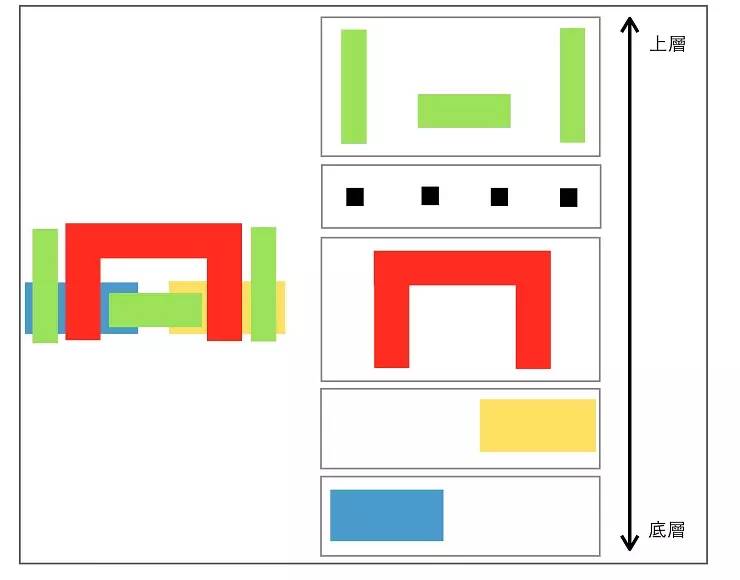

Layered Photomasks Build a Chip

First, it is already known that an IC will produce multiple photomasks, which have upper and lower layers, each with its own tasks. The following diagram is a simple example of photomasks, using the most basic component in integrated circuits, CMOS, as an example. CMOS stands for Complementary Metal-Oxide-Semiconductor, which combines NMOS and PMOS to form CMOS. As for what a metal-oxide-semiconductor (MOS) is, this widely used component in chips is difficult to explain, and it is harder for the average reader to understand, so it will not be further elaborated here.

In the diagram, the left side shows the circuit diagram formed after circuit layout and routing. As previously mentioned, each color represents a different photomask. The right side shows how each photomask is laid out. The production starts from the bottom layer, following the methods described in the previous IC chip manufacturing, layer by layer, until the desired chip is produced.

At this point, you should have a preliminary understanding of IC design. Overall, it is clear that IC design is a very complex profession, and thanks to the maturity of computer-aided software, IC design can be accelerated. IC design companies heavily rely on the wisdom of engineers, and each step described here has its specialized knowledge, which can independently form multiple specialized courses, such as writing hardware description languages not only requires familiarity with programming languages but also understanding how logic circuits work and how to convert the required algorithms into programs, and how synthesis software converts programs into logic gates.

At this point, you should have a preliminary understanding of IC design. Overall, it is clear that IC design is a very complex profession, and thanks to the maturity of computer-aided software, IC design can be accelerated. IC design companies heavily rely on the wisdom of engineers, and each step described here has its specialized knowledge, which can independently form multiple specialized courses, such as writing hardware description languages not only requires familiarity with programming languages but also understanding how logic circuits work and how to convert the required algorithms into programs, and how synthesis software converts programs into logic gates.

What is a Wafer?

In semiconductor news, wafers are often referred to by size, such as 8-inch or 12-inch wafers. However, what exactly is a wafer? What does 8 inches refer to? What difficulties are there in producing large wafers? Below we will gradually introduce the most important basics of semiconductors – what a “wafer” is.

A wafer is the foundation for manufacturing various computer chips. We can compare chip manufacturing to building a house with Lego, stacking layer by layer to achieve the desired shape (which represents various chips). However, without a good foundation, the house will be crooked and unsatisfactory. To create a perfect house, a stable substrate is needed. For chip manufacturing, this substrate is the wafer described next.

(Source: Flickr/Jonathan Stewart CC BY 2.0)

(Source: Flickr/Jonathan Stewart CC BY 2.0)

First, think back to when you played with Lego blocks as a child, where the surface of the blocks has small round protrusions that allow two blocks to be securely stacked together without glue. Chip manufacturing is done in a similar way, fixing the atoms and substrate added later. Therefore, we need to find a substrate with a smooth surface to meet the conditions required for subsequent manufacturing.

Among solid materials, there is a special crystal structure – single crystal (Monocrystalline). It has the characteristic of tightly arranged atoms, forming a smooth atomic surface. Therefore, wafers made of single crystals can meet the above requirements. But how to produce such materials? There are two main steps: purification and crystal pulling, after which such materials can be completed.

How to Manufacture Single Crystal Wafers

Purification is divided into two stages. The first step is metallurgical-grade purification, where carbon is added to reduce silicon dioxide to obtain silicon with a purity of over 98%. Most metal refining, such as iron or copper, is done in this way to obtain sufficient purity. However, 98% is still not enough for chip manufacturing, so further purification is needed. Therefore, the Siemens process is used for purification, obtaining the high-purity polysilicon required for semiconductor processing.

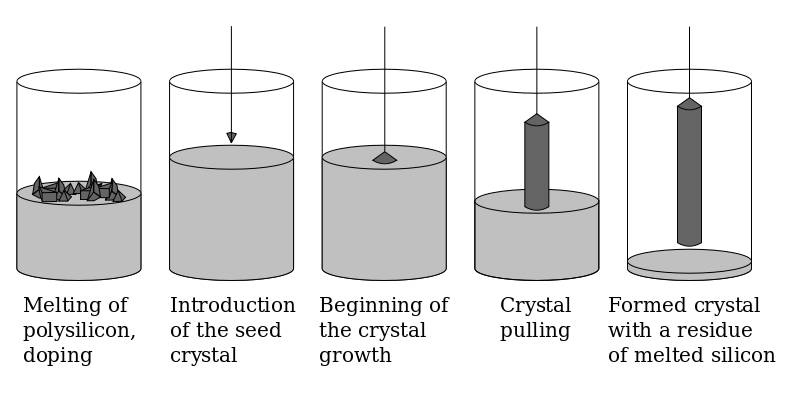

▲ Silicon rod manufacturing process (Source: Wikipedia)

▲ Silicon rod manufacturing process (Source: Wikipedia)

Next is the crystal pulling step. First, the high-purity polysilicon obtained earlier is melted to form liquid silicon. Then, a single crystal silicon seed is brought into contact with the liquid surface, and while rotating, it is slowly pulled upward. The reason for needing a single crystal seed is that the arrangement of silicon atoms is like people queuing, requiring a leader to guide the others on how to align correctly. The seed acts as this leader, helping the following atoms know how to line up. Finally, when the silicon atoms solidify after leaving the liquid surface, a neatly arranged single crystal silicon rod is completed.

▲ Single crystal silicon rod (Source: Wikipedia)

▲ Single crystal silicon rod (Source: Wikipedia)

However, what do 8-inch and 12-inch represent? They refer to the diameter of the circular slices cut from the silicon rod, which resembles the pencil body after being processed. What difficulties arise in producing large wafers? As mentioned earlier, the production process of the silicon rod is like making cotton candy, where it is shaped while rotating. Anyone who has made cotton candy knows that making large and solid cotton candy is quite difficult, and the crystal pulling process is similar. The speed and temperature control during the pulling process will affect the quality of the silicon rod. Therefore, as the size increases, the requirements for speed and temperature become higher, making it more difficult to produce high-quality 12-inch wafers compared to 8-inch wafers.

However, a complete silicon rod cannot be directly made into a substrate for chip manufacturing. To produce individual silicon wafers, the silicon rod needs to be cut into circular slices using diamond knives, and the slices are polished to form the silicon wafers required for chip manufacturing. After so many steps, the manufacturing of the chip substrate is successfully completed, and the next step is to stack the house, which is chip manufacturing. As for how to make chips?

Layered Construction of Chips

After introducing what silicon wafers are, we also know that manufacturing IC chips is like building a house with Lego, stacking layer by layer to create the desired shape. However, building a house involves many steps, and IC manufacturing is no different. What steps are involved in IC manufacturing? This article will introduce the process of IC chip manufacturing.

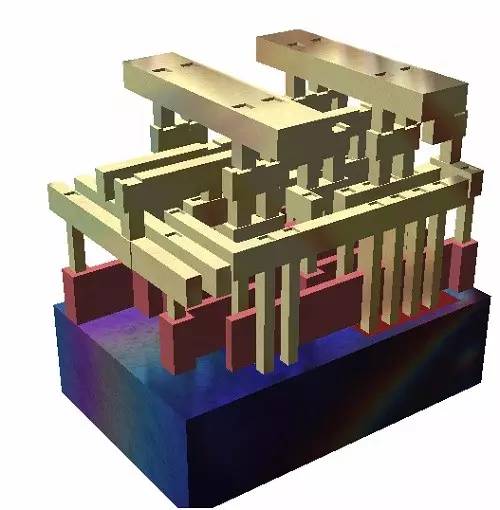

Before we begin, we need to understand what an IC chip is. IC, short for Integrated Circuit, indicates that it combines designed circuits in a stacked manner. This method allows us to reduce the area required for connecting circuits. The following diagram shows a 3D view of an IC circuit, from which it can be seen that its structure resembles the beams and columns of a house, stacked layer by layer, which is why IC manufacturing is compared to building a house.

▲ 3D cross-section of an IC chip. (Source: Wikipedia)

▲ 3D cross-section of an IC chip. (Source: Wikipedia)

From the 3D cross-section of the IC chip shown in the above image, the deep blue part at the bottom is the wafer introduced in the previous article. This image clarifies the important role of the wafer substrate in the chip. The red and brown parts are where the IC needs to be completed during the manufacturing process.

First, the red part can be likened to the lobby of a high-rise building. The lobby is the entrance of a house, where traffic flows in and out, and usually has more functionality. Therefore, compared to other floors, it is more complex to build and requires more steps. In the IC circuit, this lobby is the logic gate layer, which is the most important part of the entire IC, combining various logic gates to create a fully functional IC chip.

The yellow part resembles a typical floor. Compared to the first floor, it does not have a complex structure, and there are not many changes during construction. The purpose of this layer is to connect the logic gates in the red part. The need for so many layers arises because there are too many lines to connect, and if a single layer cannot accommodate all the lines, multiple layers must be stacked to achieve this goal. Within this, lines on different layers will connect vertically to meet wiring needs.

Layered Construction, Building Up Step by Step

Knowing the structure of ICs, the next step is to explain how they are made. Imagine that when making detailed drawings with a spray can, we first need to cut out a stencil to cover the paper. Then, we spray paint evenly over the paper, and after the paint dries, we remove the stencil. By repeatedly following this process, we can complete a neat and complex design. Manufacturing ICs is done in a similar way, layering up through masking techniques.

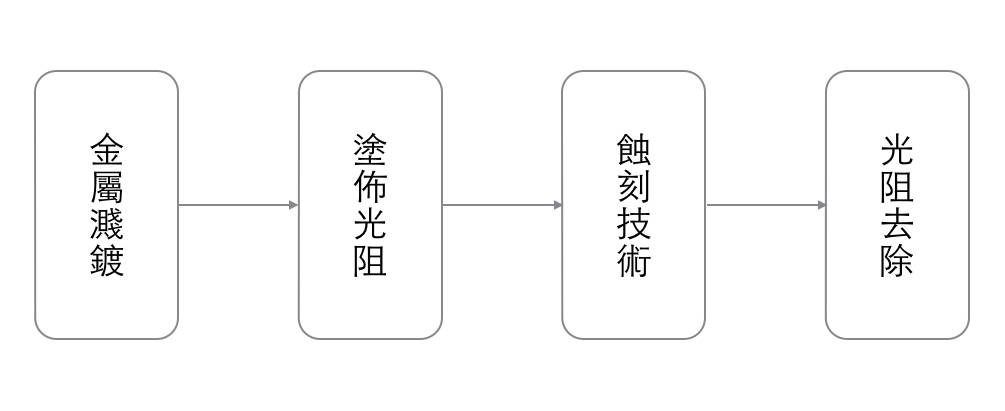

When manufacturing ICs, it can be roughly divided into the following four steps. Although the actual manufacturing process may vary, and the materials used may differ, they generally follow similar principles. This process is somewhat different from painting; in IC manufacturing, the coating is applied first, followed by masking, while in painting, masking is done before painting. The following will introduce each process.

Metal Sputtering: Evenly scatter the metal materials to be used onto the wafer to form a thin film.

Photoresist Coating: First, place the photoresist material on the wafer, and through a photomask (the principle of photomasks will be explained next time), project light onto the unwanted parts, destroying the structure of the photoresist material. Then, use chemical agents to wash away the damaged material.

Etching Technology: Etch the silicon wafer that is not protected by the photoresist using an ion beam.

Photoresist Removal: Use a photoresist remover to dissolve the remaining photoresist, thus completing one cycle of the process.

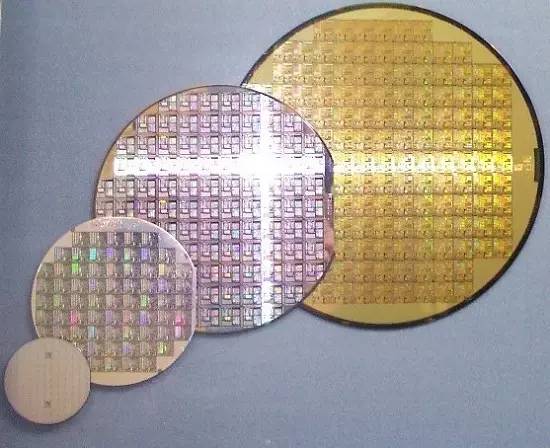

Finally, many IC chips will be completed on a single wafer, and the completed square IC chips can be cut off and sent to packaging factories for packaging. As for what a packaging factory is, it will be explained later.

▲ Comparison of various wafer sizes. (Source: Wikipedia)

▲ Comparison of various wafer sizes. (Source: Wikipedia)

What is Nanometer Process?

Samsung and TSMC are fiercely competing in advanced semiconductor processes, each wanting to gain an edge in wafer foundry to win orders, almost becoming a battle between 14 nanometers and 16 nanometers. However, what do these two numbers mean, and which part do they refer to? What benefits and challenges arise from shrinking the process? Below, we will briefly explain the nanometer process.

How Small is a Nanometer?

Before we start, we need to understand what a nanometer means. Mathematically, a nanometer is 0.000000001 meters, but this is a poor example, as we only see many zeros after the decimal point without any real feeling. If we compare it to the thickness of a fingernail, it may be more apparent.

Measuring with a ruler, we can find that the thickness of a fingernail is about 0.0001 meters (0.1 millimeters), meaning that if we try to cut a fingernail’s side into 100,000 lines, each line would be about 1 nanometer, giving a rough idea of how small 1 nanometer is.

Now that we know how small a nanometer is, we also need to understand the purpose of shrinking the process. The main goal of reducing transistor sizes is to fit more transistors into a smaller chip, preventing the chip from becoming larger due to technological advancements; secondly, it can increase the processing efficiency of the processor; furthermore, reducing the size can also lower power consumption; finally, a smaller chip can be more easily incorporated into mobile devices, meeting future demands for thinner and lighter designs.

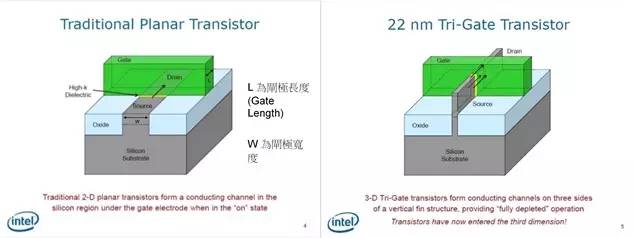

Returning to the nanometer process, taking 14 nanometers as an example, this process means that the smallest line in the chip can be made to a size of 14 nanometers. The following image shows the appearance of a traditional transistor, which serves as an example. The primary purpose of shrinking the transistor is to reduce power consumption. However, which part should be reduced to achieve this goal? The L in the lower left image is what we hope to shrink. By reducing the gate length, the current can take a shorter path from the Drain to the Source (if interested, you can search for MOSFET on Google for a more detailed explanation).

(Source: www.slideshare.net)

(Source: www.slideshare.net)

Moreover, computers perform calculations using 0 and 1. How can transistors achieve this? The method is to determine whether current is flowing through the transistor. When voltage is supplied at the Gate (the green square), current will flow from the Drain to the Source. If no voltage is supplied, the current will not flow, thus representing 1 and 0. (If interested in why we use 0 and 1 for judgment, you can look up Boolean algebra, which is the basis for computer operation.)

Physical Limits of Size Reduction

However, the process cannot be shrunk indefinitely. When we reduce the transistor size to around 20 nanometers, we encounter issues from quantum physics, leading to leakage current phenomena that offset the benefits gained from shrinking L. A solution to this problem is to introduce the FinFET (Tri-Gate) concept, as illustrated in the upper right image. According to explanations provided by Intel, by implementing this technology, leakage current caused by physical phenomena can be reduced.

(Source: www.slideshare.net)

(Source: www.slideshare.net)

More importantly, this method can increase the contact area between the Gate and the lower layer. In the traditional approach (the left upper image), the contact surface is only a flat plane, but after adopting the FinFET (Tri-Gate) technology, the contact surface becomes three-dimensional, easily increasing the contact area. This greatly aids in reducing size while maintaining the same contact area.

The main reason why it is said that major manufacturers face significant challenges when entering 10 nanometer processes is that the size of a single atom is about 0.1 nanometers. In the case of 10 nanometers, a line has fewer than 100 atoms; thus, manufacturing becomes extremely difficult. If there is a defect in a single atom, such as an atom falling out during production or impurities, it will produce unknown phenomena that affect product yield.

If you can’t imagine this difficulty, try a small experiment. Arrange 100 small beads into a 10×10 square on a table, then cut a piece of paper to cover the beads, and use a small brush to sweep away the beads around it, leaving a 10×5 rectangle. This will give you an understanding of the predicament faced by manufacturers and how challenging it is to achieve this goal.

As Samsung and TSMC recently completed mass production of 14 nanometer and 16 nanometer FinFET processes, both are vying for Apple’s next-generation iPhone chip foundry. We will witness exciting commercial competition while obtaining more power-efficient and thinner smartphones, thanks to the benefits brought by Moore’s Law.

What is Packaging?

After a long process, from design to manufacturing, we finally obtain an IC chip. However, an IC chip is quite small and thin; without external protection, it can be easily scratched or damaged. Furthermore, due to the small size of the chip, it is not easy to manually place it on a circuit board without a larger housing. Therefore, this article will describe packaging.

Currently, there are two common types of packaging: one is the black DIP packaging that looks like a centipede, commonly found in electric toys, and the other is the BGA packaging commonly seen when purchasing boxed CPUs. Other packaging methods include the PGA (Pin Grid Array) used in early CPUs or the improved QFP (Quad Flat Package) of DIP. Due to the numerous packaging methods, the following will introduce DIP and BGA packaging.

Traditional Packaging, Timeless

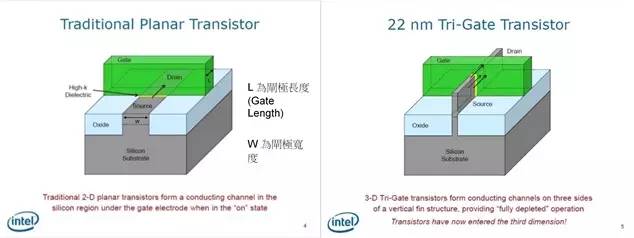

The first to introduce is the Dual Inline Package (DIP). As seen in the image below, IC chips using this packaging have dual rows of pins, resembling a black centipede, leaving a deep impression. This packaging method is the earliest adopted IC packaging technology and has the advantage of being cost-effective, suitable for small chips that do not require many connections. However, since most are made of plastic, the heat dissipation is poor, failing to meet the requirements of today’s high-speed chips. Therefore, those using this packaging are mostly timeless chips, such as the OP741 shown in the image below, or IC chips that are smaller and require fewer connection holes with lower speed requirements.

▲ The IC chip on the left is OP741, a common voltage amplifier. The right image is its cross-section, where the packaging connects the chip to the metal leads (Leadframe). (Source: Left image Wikipedia, Right image Wikipedia)

▲ The IC chip on the left is OP741, a common voltage amplifier. The right image is its cross-section, where the packaging connects the chip to the metal leads (Leadframe). (Source: Left image Wikipedia, Right image Wikipedia)

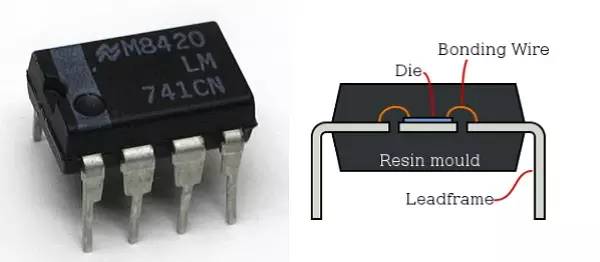

Compared to DIP, the Ball Grid Array (BGA) packaging is smaller and can be easily placed in compact devices. Additionally, since the pins are located beneath the chip, it can accommodate more metal pins than DIP, making it suitable for chips needing more connection points. However, this packaging method is more costly and complex, so it is mostly used in high-priced products.

▲ The left image is a chip with BGA packaging. The right image is a schematic of BGA packaging using flip-chip technology. (Source: Left image Wikipedia) Mobile devices are on the rise, and new technologies are taking the stage.

However, using the aforementioned packaging methods consumes a significant amount of space. With the rise of mobile devices, wearables, and other components, if each component is independently packaged, it will occupy a considerable amount of space. Therefore, there are currently two methods to meet the demand for reduced size: SoC (System On Chip) and SiP (System In Package).

When smartphones first emerged, the term SoC could be found in many financial magazines. But what exactly is SoC? Simply put, it integrates originally separate functional ICs into a single chip. This method not only reduces size but also shortens the distance between different ICs, improving the chip’s computing speed. As for the manufacturing method, during the IC design phase, different ICs are placed together, and through the previously introduced design process, a photomask is created.

However, SoC is not without drawbacks. Designing an SoC requires considerable technical collaboration. When IC chips are packaged separately, each has external protection, and the distance between ICs is greater, reducing the likelihood of interference. However, when all ICs are packaged together, it becomes a nightmare. IC design companies must transition from simply designing ICs to understanding and integrating various functional ICs, increasing the workload for engineers. Additionally, many situations may arise, such as high-frequency signals from communication chips potentially affecting other functional ICs.

Moreover, SoC must obtain IP (intellectual property) licenses from other manufacturers to incorporate pre-designed components into the SoC. Since creating an SoC requires access to the design details of the entire IC to create a complete photomask, this also increases the design costs of the SoC. Some may question why not design a new one? Designing various ICs requires a wealth of knowledge related to that IC. Only financially strong companies like Apple can afford to hire top engineers from various well-known companies to design a brand-new IC, making collaboration and licensing more cost-effective.

Compromise Solution: SiP Emerges

As an alternative, SiP has taken the stage in integrated chips. Unlike SoC, it involves purchasing ICs from various manufacturers and packaging them together in the final step, thus eliminating the need for IP licensing, significantly reducing design costs. Additionally, since they are independent ICs, the degree of interference between them is greatly reduced.

▲ The Apple Watch adopts SiP technology to package the entire computer architecture into a single chip, not only meeting the expected performance but also reducing size, allowing more space for the battery. (Source: Apple Official Website)

▲ The Apple Watch adopts SiP technology to package the entire computer architecture into a single chip, not only meeting the expected performance but also reducing size, allowing more space for the battery. (Source: Apple Official Website)

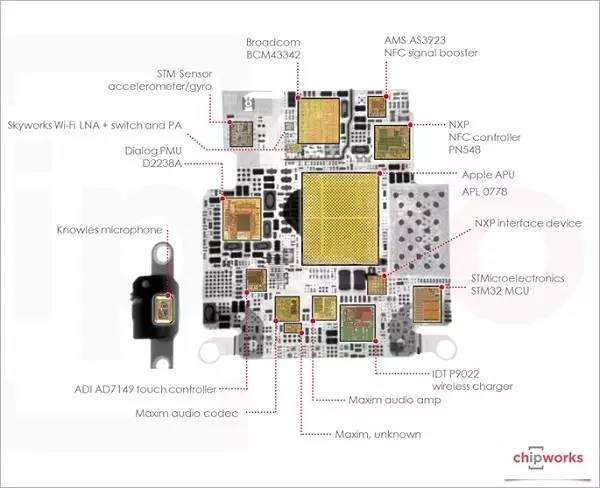

Products using SiP technology, the most famous of which is the Apple Watch. Due to the small internal space of the watch, traditional methods cannot be used, and the high design cost of SoC makes SiP the primary choice. By using SiP technology, not only can the size be reduced, but the distance between ICs can also be shortened, making it a feasible compromise solution. The following image shows the internal configuration of the S1 chip used in the Apple Watch, where many ICs are included.

▲ Configuration diagram of the S1 chip used in the Apple Watch (Source: chipworks)

▲ Configuration diagram of the S1 chip used in the Apple Watch (Source: chipworks)

After packaging, the next step is testing, where it is necessary to confirm whether the packaged IC operates normally. Once confirmed to be correct, it can be shipped to assembly factories to be made into the electronic products we see. At this point, the semiconductor industry has completed the entire production task.

Source: Wu Zhengdao TechNews

Recent Popular Articles Top 10

↓ Click the title to view ↓

1. Everything You Need to Know About Physics

2. Understanding Fourier Transform in Simple Terms

3. Seeing is Believing? Understanding the Cover Story

4. Mathematical Beauty of Sunflowers

5. All-New Energy Systems Invented! Efficiency Beats Solar Power

6. Which Radiations in Daily Life Are Harmful?

7. Physicists Teach You How to Cross Correctly! This Is Not Science Fiction…

8. Why Is the Earth Round?

9. Can Raindrops Hurt People? | Not Just Speed Factors

10. Looking at the Splendor and Strength of Love Through the Eyes of Chemistry

Click on the “Top 10” menu in the public account to view the past monthly popular articles Top 10