▲ Click the above Leifeng Network to follow

For RISC-V to succeed like x86 and Arm, building the ecosystem is crucial.

Written by | Bao Yonggang

Launched in 2010, the RISC-V instruction set saw its first user manual officially released in 2014. From facing skepticism to gaining widespread optimism, many globally renowned companies such as NVIDIA, Western Digital, Qualcomm, HiSilicon, Alibaba, and Samsung have joined the RISC-V Foundation to promote its development. However, for RISC-V to succeed like x86 and Arm, building the ecosystem is crucial. This is because companies like Western Digital and HiSilicon need to launch RISC-V processors and related product toolchains more quickly.

As a significant driving force behind RISC-V development, in February of this year, Western Digital released its self-developed general-purpose architecture, SweRV, based on the RISC-V instruction set. This is part of Western Digital’s efforts to lead the ISA (Instruction Set Architecture) and its ecosystem, as well as their transition to unlicensed CPU cores.

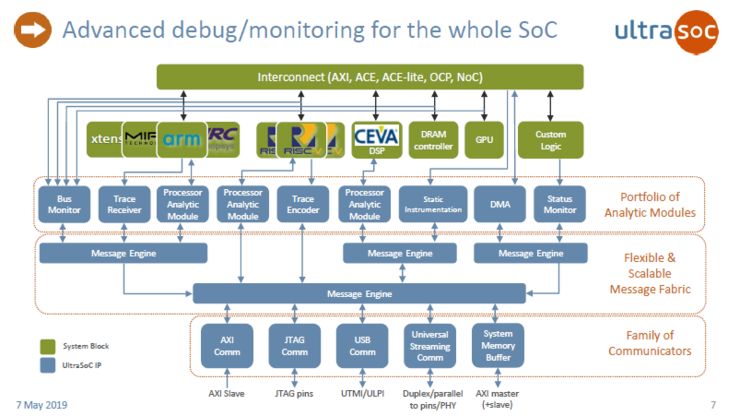

It is noteworthy that while Western Digital released the general-purpose architecture SweRV, semiconductor IP provider UltraSoC also announced comprehensive support for Western Digital’s RISC-V SweRV Core processor and the related OmniXtend cache coherence interconnect structure within its embedded analytics architecture, which will support Western Digital’s internal development team and third-party partners who choose to develop their applications using the SweRV Core processor.

RISC-V Software Support Becomes Key

UltraSoC CEO Rupert Baines recently stated in an interview: “Three years ago, RISC-V only had one architecture; two years ago, processor cores began to emerge, and now there are seven or eight commercial RISC-V companies. Clearly, having only RISC-V cores is not enough; many companies are now developing around RISC-V cores, and the RISC-V ecosystem is improving. As one of them, we also hope to benefit and are very happy to grow the RISC-V software ecosystem together with other companies.”

UltraSoC CEO Rupert Baines

Dr. Fang Zhixi, Chairman of the Advisory Committee of the RISC-V Foundation in China, stated in an exclusive interview with Leifeng Network: “RISC-V is just getting started, and building the entire RISC-V ecosystem involves a lot of software, especially system software.”

Rick O’Connor, Executive Director of the RISC-V Foundation, has also stated: “RISC-V is redefining the value proposition of SoCs: one key part is to build a more open and robust ecosystem than the developers’ usual solutions. On a technical level, comprehensive supply of processor tracking IP is a key part of this developmental ecosystem. Within the RISC-V Foundation, we are working on standardizing interfaces connected to RISC-V cores, including processor tracking capabilities provided in the interface specifications.”

Processor Tracking Technology is Key to Accelerating RISC-V

Leifeng Network has learned that while mature Arm already has processor tracking capabilities, RISC-V does not yet have a standard processor tracking feature. How important is processor tracking? Due to interactions with software from other cores, peripherals, real-time events, immature integration, or some combination of these factors, software does not always run as expected or at the expected time, resulting in impacts on real-time behavior. Therefore, having detailed, instruction-level visibility into program behavior is a critical requirement for system developers.

In increasingly complex SoC designs, processor tracking is playing an increasingly important role in improving design efficiency and accelerating time-to-market.

A UK semiconductor IP provider, UltraSoC, established in 2011, has filled this gap in RISC-V functionality. In June 2017, UltraSoC announced that it had developed processor tracking technology that supports RISC-V architecture. In February 2018, UltraSoC officially launched the industry’s first commercial RISC-V processor tracking technology IP, with five core suppliers, including Andes Technology, Codasip, Roa Logic, SiFive, and Syntacore, announcing support for UltraSoC’s new tracking specification.

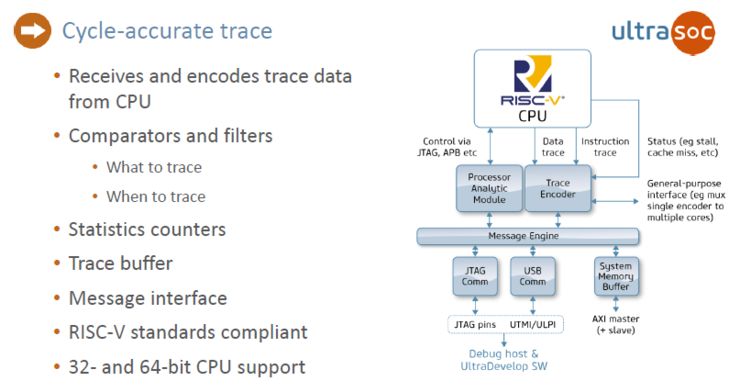

Specifically, UltraSoC’s RISC-V tracking encoder supports both 32-bit and 64-bit RISC-V designs. The IP module can be integrated with other parts of the UltraSoC product suite, supporting open architecture and industry-standard architecture approaches, and setting up self-analysis capabilities in the core part of the SoC. This can help applications in automotive, enterprise IT, and IoT manage complexity and improve time-to-market, design costs, reliability, and security capabilities.

What Will Cycle-Accurate Tracking Technology Bring?

Rupert Baines stated that for software engineers, as long as the application runs correctly, they do not care about performance on every cycle. However, for some specific applications, knowing the specific timing is necessary, and timestamps must correspond. To this end, our latest offering is cycle-accurate tracking technology, which, by adding cycle-accurate tracking capabilities, allows developers not only to see what is happening inside the device but, more importantly, to see when certain events occur.

He further stated that accessing this cycle-accurate tracking information means that customers dedicated to deep embedded applications will be able to accurately view the number of cycles their code executes, whether there are stalls and dependencies, and how long they last. With this information, system designers can further optimize their designs and achieve maximum efficiency gains.

So, which specific applications require cycle-accurate tracking technology? Rupert Baines cited examples, stating that due to the very fast transmission speed of 5G, the interval between two frames of data is very short, so cycle-accurate tracking technology is needed for the modems of 5G base stations. Additionally, companies like Western Digital and Seagate, which produce high-speed storage, want their engineers to process data more and faster with each cycle to enhance system performance, where cycle-accurate tracking technology can also play an important role.

However, beyond improving system performance, security is also critical. Rupert Baines stated that processor tracking technology can also enhance processor security. Because when the processor executes instructions, it accesses memory addresses, and the tracker will have corresponding records. When the processor accesses illegal address ranges, it will trigger an alarm.

In addition, UltraSoC not only provides instruction tracking but also offers data, unordered, and out-of-order tracking, enabling tracking technology to meet not only simple tracking needs but also the demands of high-performance RISC-V processors.

Leifeng Network Summary

RISC-V is now receiving widespread attention, but whether it can succeed like x86 and Arm depends on software and hardware support, which is the key to ecosystem building. Currently, RISC-V has core providers, but the toolchain is still not complete. As a semiconductor IP provider, UltraSoC clearly sees the future development of RISC-V. Their processor tracking functionality will not only be applied in the processor design phase but will also play a role in actual applications. According to Leifeng Network (WeChat public account: Leifeng Network), 50% of UltraSoC’s revenue last year came from RISC-V, and 40% came from Arm, with the Chinese market being their second-largest revenue market, second only to the United States.

Different eras have produced different instruction sets, from the x86 of the PC era to the Arm of the mobile internet era. RISC-V is considered the instruction set for the IoT and AI era, but this open-source instruction set still faces many challenges to succeed. However, we can see that giants like Western Digital, Alibaba, HiSilicon, and NVIDIA are all promoting the development of RISC-V, and UltraSoC is also working as part of the software ecosystem to build the RISC-V software ecosystem together with other manufacturers.

– END –

◆ ◆ ◆

Recommended Reading

Google I/O 2019 Full Record: AI Stunning, Android Q Tasty, and Two New Hardware

Microsoft Build 2019: Windows 10 Retreats, IE Reborn, Azure Takes Center Stage

Lenovo Responds to Online Rumors; WeChat Drift Bottle Function Officially Offline; Cook: Does Not Want Users to Be Addicted to iPhone

Academician Ling Xiaofeng of the Canadian Academy of Engineering: Chinese Students Lack a Spirit of Inquiry and Innovation

Alibaba Responds to “Dismantling the Middle Platform”; Buffett and Munger: Missing Google is a Huge Mistake; The World’s Second Largest Dark Web Trading Platform Destroyed

For summit ticket information, click “Read the original text” for details~