Introduction

✦

The main gap between RISC-V and ARM currently lies in the upstream and downstream industrial ecosystem and large-scale applications, which is the biggest challenge and difficulty facing the players in the RISC-V camp.

✦

✦

We command computers to work, and we cannot simply say to the computer, “Hey, run a program for me.” Because computers can only understand instructions made up of 0s and 1s (machine language), do humans need to input thousands of 0s and 1s to operate a computer? Friends who know a bit about programming understand that using a programming language to make the computer output “hello, world” only requires a simple line of code:

printf(“hello, world\n”); // C language description

print(“hello, world”) # Python language description

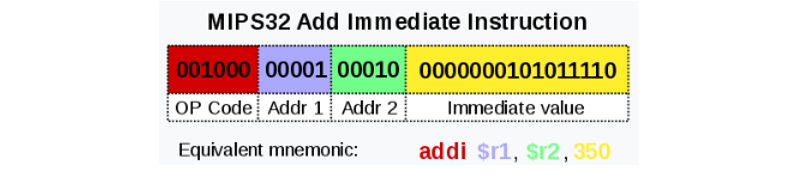

This is much simpler and clearer than just using 0s and 1s. In fact, when the computer runs this line of code, the CPU still receives a string of commands made up of only 0s and 1s. The change in between is the instruction set architecture (ISA) and programming languages (assembly + high-level) helping us translate; the instruction set is the “translator” that is closest to machine language. In simple terms, the instruction set is a collection of binary machine language instructions, and the language used to describe these binary instructions is called assembly language. Later, many compilers and high-level languages emerged to help programmers code more easily. The RISC-V and ARM discussed in this article are both types of instruction sets.

Add Immediate Instruction (binary machine language)

Add Immediate Instruction (binary machine language)

Image Source | Wikipedia

To design a processor, the first step is to determine which instruction set the processor will use. The instruction set determines how the chip calculates when it is working; the numerous and complex transistors on the chip essentially fix the instruction set with circuits.

In summary, the instruction set is extremely important for the chip, as it directly determines the layout of the chip’s circuits. It is a series of instruction systems defined at the design stage of every new CPU that works in conjunction with hardware circuits. The advancement of the instruction set also relates to the performance of the CPU, making it an important indicator of CPU performance.

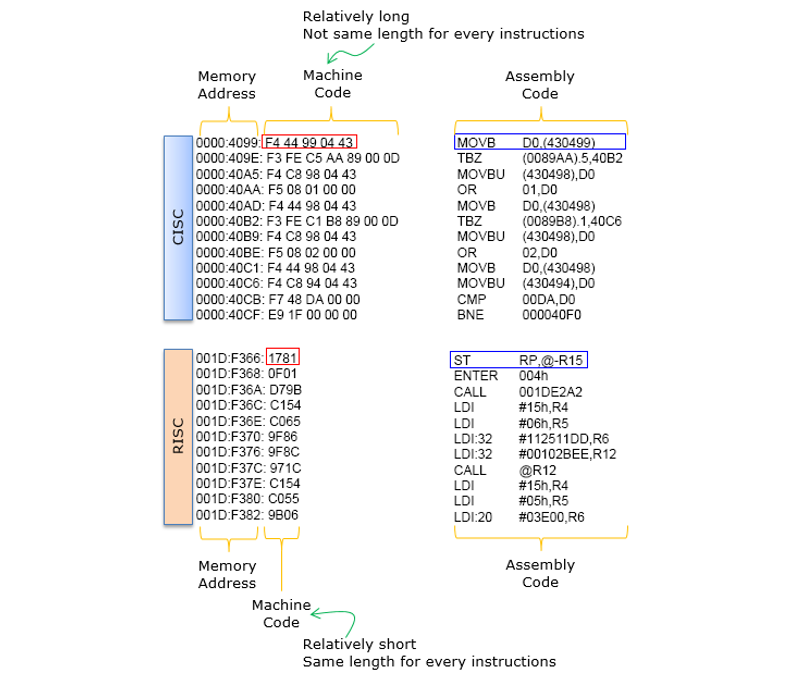

Currently, instruction sets are divided into two categories: Reduced Instruction Set (RISC) and Complex Instruction Set (CISC), but their difference is not in the length of the binary commands.

CISC vs. RISC

When instruction sets were first created, they were quite complicated. People optimized them by packing some instructions together and changing some commonly used functions originally implemented in software to be implemented through hardware instruction systems to improve the execution speed of computers. This type of instruction set is called Complex Instruction Set Computer (CISC). In CISC, memory read, storage, and computation operations are often concentrated in a single instruction. The characteristics of CISC are that it has many complex instructions, and the instruction lengths are not equal, requiring the computer to interpret them, which incurs additional performance costs.

In the 1980s, to address performance deficiencies in computers, people found another way to optimize instruction sets. Chip designers chose to retain only some simple, fast-executing commands and implemented complex programs with a segment of code. This type of instruction set is called Reduced Instruction Set Computer (RISC). RISC belongs to fixed-length instruction sets, allowing the CPU to execute instructions quickly and maintain stable performance. Compared to CISC, RISC is easier to implement instructions such as function calls, returns, and loops, has better instruction-level parallelism, and higher compiler efficiency.

Differences Between RISC and CISC Instructions

Differences Between RISC and CISC Instructions

Image Source | Tech Journeyman

Since RISC has such obvious advantages, does it mean that RISC will inevitably replace all CISC instruction sets?

Not necessarily. Compared to CISC, RISC instruction sets also have their shortcomings. Although RISC instructions are simpler, they have fewer instructions, which means that more instructions need to be executed to complete certain tasks. This also makes the length of RISC code significantly longer than CISC during compilation, thus requiring more memory and increasing compilation difficulty. Industry experts have analyzed RISC’s shortcomings: “To perform the same function, a RISC program is 30% longer than a CISC program. At the same time, RISC has higher requirements for the compiler; optimizing the compiler is an extremely complex and highly technical task that must be compiled by the RISC machine manufacturer itself. Without detailed original information on RISC, it is impossible to produce the target code for the compiler program. This will lead third-party companies to incur additional software support costs.”

In essence, there is no superiority or inferiority between RISC and CISC, only different applicable scenarios. For example, the x86 architecture, which belongs to CISC, allows Intel and AMD processors to maintain an absolute advantage in the CPU field. Desktop or server processors can afford to consider less about power consumption and battery life compared to mobile processors, so their performance is sufficiently strong and not hindered by the characteristics of CISC, allowing them to execute complex tasks more efficiently. However, processors for mobile computers (such as smartphones and tablets) must consider power consumption and heat dissipation alongside performance during their design, which gives RISC instruction sets development space. Therefore, during the explosion of the mobile market, the ARM architecture, which belongs to the RISC instruction set, emerged and currently occupies the largest share of the mobile market. The well-known Qualcomm Snapdragon series and Samsung Exynos series chips both use ARM’s IP core.

8086 CPU, marking the birth of the x86 architecture

8086 CPU, marking the birth of the x86 architecture

Image Source | Baidu Encyclopedia

The Birth of RISC-V and ARM

The birth of ARM chips is quite dramatic.

In 1981, Acorn Computers, which had just been established for three years, received an order from the BBC to produce computers. However, at that time, processors were in the transition from 8-bit to 16-bit, and Acorn did not have a suitable chip. They turned to Motorola for help. Although Motorola provided a 16-bit chip, it failed the evaluation due to excessive interrupt response time. Acorn then sought Intel’s help, hoping to obtain some design data and samples of the 80286 processor, but was refused. Frustrated, Acorn decided to manufacture their own chip. After years of hard work, two scientists from Cambridge University finally completed their chip design and named it the Acorn RISC Machine, or ARM chip, where RISC refers to the Reduced Instruction Set mentioned earlier. On November 27, 1990, Acorn officially restructured into ARM Computer Company.

After years of development, today’s ARM is no longer the small company that was “beaten” by Intel. The current ARM Cortex core is widely recognized in the market, covering everything from children’s watches and smartphones to digital TVs, smart cars, and CT machines. Chips based on the ARM architecture have reached a wide range of electronic devices. ARM has effectively gained the position in the mobile sector that Intel once held in the processor field.

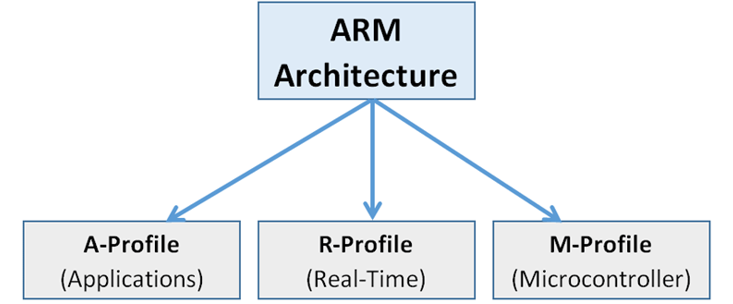

Classification of ARM Processor Architectures

Classification of ARM Processor Architectures

Image Source | Circuit Digest

The slayer of dragons ultimately becomes the “dragon”; how will RISC-V, this “warrior,” challenge ARM? Let’s first understand RISC-V and compare their differences.

RISC-V is the fifth version of the RISC ISA designed by the University of California, Berkeley. The Roman numeral “V” indicates “variant” and “vector,” signifying its support for a series of computer architecture research. In 2010, Professor Krste Asanović from the Computer Science Department at UC Berkeley aimed to establish an open-source computer system specification similar to Linux. With the help of David Patterson, they began designing RISC chips in the 1990s, ultimately forming RISC-V. Later, the RISC-V Foundation was established to maintain, promote, and manage RISC-IV IP and assist manufacturers in collaboration. Following the U.S. restrictions on advanced chip exports, the RISC-V Foundation moved from California to Switzerland. Currently, it has about 1,000 members (companies) in 50 countries and regions, including heavyweight enterprises such as Huawei, Alibaba, Google, NVIDIA, and IBM.

Image Source | Circuit Digest

RISC-V vs. ARM

Like ARM, RISC-V is also a type of RISC instruction set. Many media outlets have analyzed the differences between these two instruction sets regarding open-source vs. closed-source, free vs. paid. Today, let’s take a look at their architectural similarities and differences.

In terms of memory interaction, both RISC-V and ARM use a load-store architecture, meaning that memory can only be accessed when storing and retrieving data; arithmetic operations are completed within the CPU, and the final computation results are written back to memory. However, the byte order (Endianness) of the two instruction sets is different. Byte order refers to the arrangement of bytes in memory or during transmission over digital links, which can be classified into two types: big-endian (high-order first) or little-endian (low-order first). ARM processors default to little-endian but also support big-endian, while RISC-V only supports little-endian. There is no inherent superiority between the two modes; they simply have different advantages in data processing.

In terms of architectural complexity, RISC-V is inherently simple, with only over 40 basic instructions, and with other modular extension instructions totaling several dozen instructions. Its specification document is only 145 pages long, and the “privileged architecture document” is also only 91 pages long. ARM, being a closed instruction set architecture, does not allow manufacturers to modify the chip based on existing designs after adopting ARM IP cores; companies can only adjust their needs to fit the ARM core. After many years of development, the ARM instruction set has become extremely complex and cumbersome, with corresponding architectural documents spanning thousands of pages. This indirectly leads to a much higher R&D threshold for ARM processors than for RISC-V.

Regarding customization, RISC-V has not been overly optimized for any function, architecture, or target, making it suitable for almost all computing scenarios. ARM is more optimized for smartphones than for laptops, desktops, and servers. Thus, ARM chips have an unshakeable dominance in the mobile sector.

Conclusion

From the above content, it can be seen that although RISC-V and ARM are both RISC instruction sets, they have different characteristics in their instruction sets. In addition to being open-source and free, the simplicity and low development threshold are also RISC-V’s killer features in challenging ARM.

Currently, the main differences between RISC-V and ARM lie in the upstream and downstream industry ecosystem and large-scale applications, which present the biggest challenges and difficulties for the players in the RISC-V camp.

References:

ARM vs RISC-V

https://techjourneyman.com/blog/arm-vs-risc-v/

Understanding RISC-V Architecture and Why it could be a Replacement for ARM

https://circuitdigest.com/article/understanding-risc-v-architecture-and-why-it-could-be-a-replacement-for-arm

The Relationship Between Processor Architecture, Instruction Sets, and Assembly Language

https://www.zhihu.com/question/23474438

The Development History of ARM Chips

https://zhuanlan.zhihu.com/p/370771150

– END –

The reproduced content only represents the author’s viewpoint

Editor: Liu Kuaiqian