By | Zhang Jiahua

Edited by | Cheng Manqi

Half a month ago, Google announced that Android would fully support the RISC-V instruction set, which will encourage mobile phone and chip manufacturers to consider RISC-V chips more seriously. RISC-V has opened the door to a market worth hundreds of billions of dollars annually, adding billions of potential users.

This is the first time that a chip instruction set not controlled by a single commercial entity has gained such significant industrial ecosystem support. Not being controlled by a single commercial entity means it is not influenced by the will of the country where that company is located.

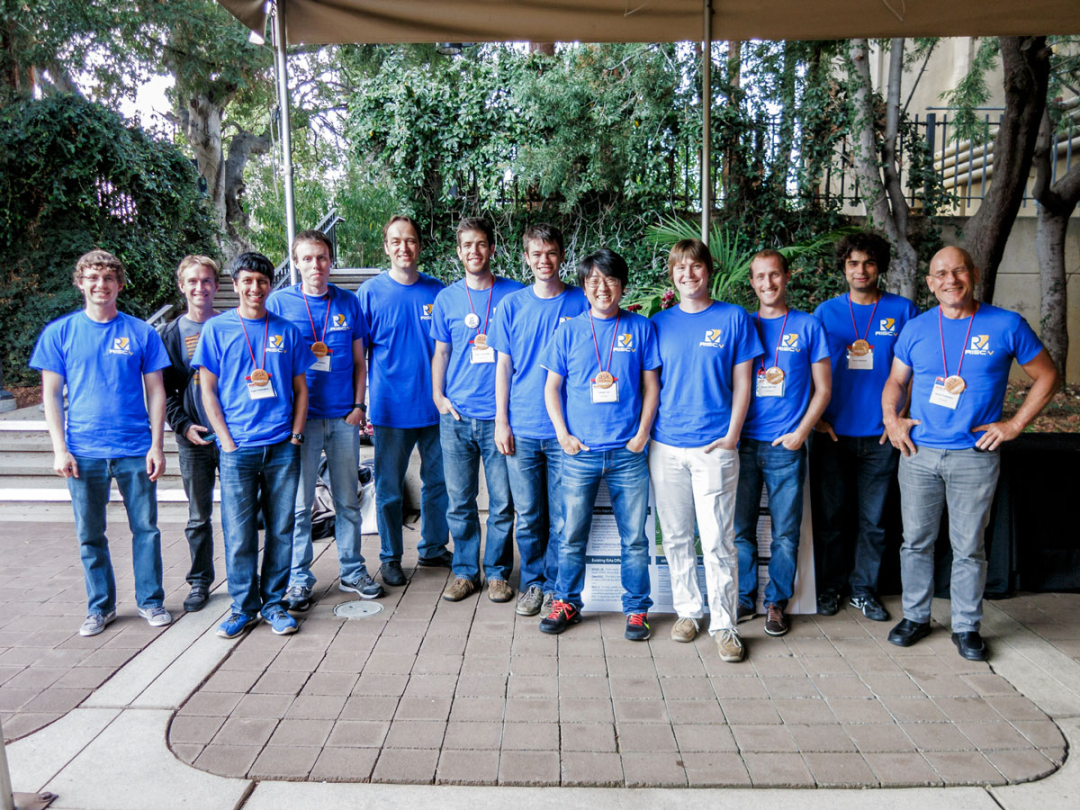

Ten years ago, RISC-V was an unremarkable project. At the Hot Chips conference in 2014, held in the United States, a dozen students and professors from the RISC-V project team promoted this new open-source instruction set born on the Berkeley campus to attendees. They did not have a booth in the main hall and were not invited to speak; instead, they set up a small tent outside the venue, displayed a few posters, handed out flyers, and distributed small badges.

The small badges bore a grand slogan: “Instruction sets want to be free!”

A group photo of the participants from the Berkeley Par Lab RISC-V project team at the conference, including David Patterson (far right), the inventor of the reduced instruction set, a professor in the Computer Science Department at Berkeley, Krste Asanovic (fifth from the left), a professor in the Computer Science Department at Berkeley and chief architect at SiFive, Andrew Waterman (fourth from the right), chief scientist at SiFive, and CTO Li Yunshep (fifth from the right). Swipe right to see the badge designed for RISC-V at that time.

In the history of the semiconductor industry, no one has ever realized this vision. Instruction sets are like the “language” of the chip world; they define the design specifications between chips and corresponding software and are important industry standards.

Before RISC-V, mainstream instruction sets were monopolized by companies in Europe and America: the x86 instruction set invented by Intel dominated the CPU market in personal computers and data centers, while the ARM instruction set invented by Arm has long been leading in mobile devices such as smartphones.

Less than a decade after that inconspicuous promotion at Hot Chips, RISC-V has grown into a potential “third pole” of instruction sets that can compete with x86 and ARM. Since its invention in 2010, the shipment of RISC-V-based chips has reached 10 billion units. ARM instruction set chips took nearly 30 years to reach the same shipment volume.

This year, RISC-V continues to accelerate its development. In addition to Android’s support, chip giants or major demanders such as Google, Intel, Pingtouge, Samsung, MediaTek, Qualcomm, Infineon, and Bosch are investing in RISC-V by forming ecological alliances or establishing new companies.

RISC-V is particularly important for China. After the U.S. government imposed new restrictions on chip exports in October last year, the impact was not limited to high-end GPUs like A100 and H100 used for training AI large models and autonomous driving systems, but also included high-end CPUs essential for servers, most of which are based on Intel’s x86 architecture. The open-source RISC-V has become one of the important breakthroughs for the Chinese supply chain to secure server CPUs.

The overall primary market in China is currently sluggish, but there is still an influx of funds into the RISC-V field. From last year to this year, RISC-V companies such as Yiswei Computing, Saifang Technology, ChipRise Technology, and Jindie Space have completed new financing. Among them, Yiswei Computing completed 3 billion RMB in Series D financing in July this year, and Jindie Space completed two rounds of financing within a year. New companies are still emerging, such as Blue Core Computing, Zhixing Wujie, and Jingyuan Core.

At an industry event this year, Chinese Academy of Engineering academician Ni Guangnan said, “It is no exaggeration to say that today RISC-V is the most popular architecture in China’s CPU field.”

Some people have begun to worry about the overheating of the industry. At a closed-door meeting of the RISC-V summit in Beijing this August, a CEO of a startup said, “We need to be cautious about whether the current prosperity of RISC-V is ‘false prosperity.'”

From being an obscure summer project in schools to becoming a sought-after industrial force, RISC-V has only taken ten years. What is even rarer is that it has achieved all this through open source.

The Chinese chip industry, which hopes to find its own space, is an important force accelerating RISC-V, but not the only one. There are also ideals of open source, speculative hype, profit desires, cost reduction, and the urgency to break free from monopolies, along with the dedication of technical personnel and strategies of collaboration. This is a story of various forces and demands colliding in an increasingly severe global technological cooperation environment, helping “naivety” enter reality.

Unintentional Outcomes

The birth of RISC-V at the Berkeley Par Lab is an unintentional “byproduct.”

Par Lab was founded in 2005 by David Patterson and his student Krste Asanovic.

David Patterson, a staunch supporter of open source and free software, initially aimed to make a good profit. He was the first college student in his family, originally studying mathematics at UCLA to become an insurance actuary, but he encountered computers in an elective course taken to earn credits. Finding his passion, Patterson bid farewell to his actuarial plans and entered Berkeley, the top computer science department in the U.S., in 1970 to pursue a master’s and doctoral degree, remaining at the university to teach after graduation.

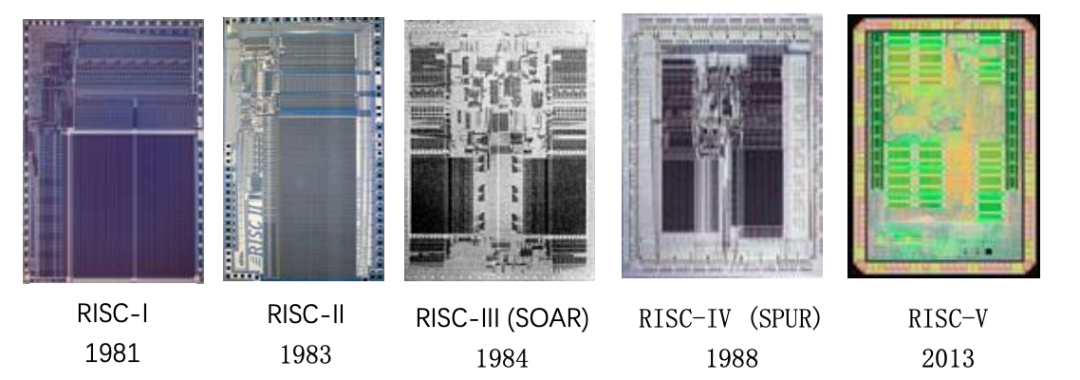

In the late 1970s, when Patterson began his academic career, almost all CPUs were based on the complex instruction set (CISC) x86 invented by Intel, making it very difficult for new companies to develop CPUs. In 1981, Patterson created a new instruction set significantly different from CISC based on IBM’s PowerPC, known as the “Reduced Instruction Set” (RISC), which has only dozens of instructions, making it more agile and energy-efficient than complex instruction sets with hundreds of instructions, effectively reducing hardware development costs and shortening development cycles. In 2017, Patterson received the Turing Award for his contributions to RISC.

The first company to realize the immense commercial value of the reduced instruction set was Arm, founded in 1990 in the UK, which opened up the IP licensing model (selling chip design IP to downstream chip design companies) and, together with TSMC, which pioneered the foundry model, reshaped the division of labor in the chip industry: a chip company no longer needs to build its own factory but can focus on chip design with lower asset thresholds, which is known as Fabless. A number of giants have thus emerged, and Nvidia, Qualcomm, and Apple’s self-developed chips are products of this new pattern and also its promoters.

Patterson himself intersected with the industrialization of the reduced instruction set nearly 30 years after he invented it.

In 2010, several young PhD students at Par Lab were busy with a summer project on parallel computing, needing to make some modifications to the underlying chip instruction set, but they could not find a ready-made free and modifiable instruction set, leaving only one path: to develop a new instruction set.

Tan Zhangxi, founder of RISC-V International Open Source (RIOS) Laboratory and an executive director, was a member of the project team at that time. He graduated from Tsinghua University’s Department of Electronic Engineering in 2005 and entered Berkeley for his PhD under Patterson’s guidance.

Tan Zhangxi told LatePost that Patterson had extensive experience with reduced instruction sets and had developed several generations of RISC before; under his guidance, developing RISC-V took only two to three months, and it had only about 50 instructions, making it very lightweight.

The origins of RISC-V can be traced back to 1981. David Patterson and Carlo H. Sequin at Berkeley designed the RISC-I processor using a reduced instruction set.

Initially, Par Lab only regarded RISC-V as a research and teaching tool, using it in undergraduate and graduate courses in the Berkeley Computer Science Department, which is the fate of most instruction sets born in universities. In 2011, they further put RISC-V online, open-sourcing it for everyone, with the original intention of promoting more academic exchanges.

Tan Zhangxi stated that Par Lab had long planned to open-source RISC-V. Patterson, who had long abandoned the goal of making money, often encouraged students to pursue influence, and open-sourcing was a great way to expand technological influence.

Open source also aligns with the Berkeley culture that values freedom and equality. RISC-V uses one of the most open-source licenses, the BSD license, which allows developers to freely and freely use, modify, and redistribute software source code, sell products developed based on RISC-V, and even without the need to indicate the use of RISC-V. The BSD open-source license, known as Berkeley Software Distribution, originated from Berkeley. The Berkeley administration also agreed to waive patent rights to RISC-V.

Unexpected feedback began to come from all directions. Tan Zhangxi recalled that in 2012, Indian developers wrote to them, hoping that the instruction set would not be modified frequently because they were already trying to develop products based on RISC-V. In January 2015, the first RISC-V workshop was held in a classroom at MIT, attended by only over 40 people, but companies had already presented products, such as the American chip company Bluespec, which introduced an open-source chip designed based on RISC-V at the meeting. Around the same time, another chip company, Rumble Development, also attempted to deliver chips containing RISC-V cores to customers.

Patterson, Asanovic, and others began to seriously consider pushing RISC-V into the industry. Commercial companies value the stability of instruction sets and cannot change them arbitrarily; schools focus on exploring new technological directions, and it was time for RISC-V to step out of the campus.

In August 2015, the RISC-V Foundation was officially established, registered in Nevada, USA. The foundation does not own RISC-V; its income comes from membership fees. The foundation is responsible for organizing meetings, reviewing community developers’ suggestions for the RISC-V instruction set, and ultimately deciding whether to add or modify instructions, ensuring orderly version iterations.

Patterson and Asanovic have high hopes for RISC-V. In 2014, they published a detailed paper introducing RISC-V titled “Instruction Sets Should Be Free,” in which they wrote: “Just as Linux has become the standard operating system for most computing devices, we hope RISC-V will become the standard instruction set for all computing devices.”

Not many people shared the same optimism. Tan Zhangxi recalled that Bill Dally, chief scientist at Nvidia, often visited Berkeley for discussions at that time. He asked Par Lab members: Why reinvent the instruction set? x86 and ARM have dominated the industry for many years, and there seems to be no gap for a new instruction set.

In 2015, two students from the project team, Yunsup Lee and Andrew Waterman, wanted to establish a commercial company for RISC-V. Krste Asanovic, who later became the chief architect of that company, said: The more you understand semiconductor industry investors, the faster they reject you.

Even those who experienced the RISC-V project found it hard to imagine its future success. A student from the Chinese Academy of Sciences told LatePost that when they encountered some technical issues while developing the RISC-V compiler in 2018, they contacted a student of Patterson, who replied, “I no longer work on RISC-V.”

Asanovic, however, still encouraged everyone: “As long as something is not completely unfeasible, you will want to try it.” Because “one of the greatest forces in the universe is the naivety of graduate students.”

Gradually Gaining Momentum

The naive graduate students Waterman and Lee were fortunate to secure funding. After obtaining $5 million from SHV, a Silicon Valley venture capital firm focused on early-stage technology investments, they established SiFive, now a leading company in the RISC-V field, in July 2015.

No obvious environmental factors indicated that RISC-V would develop rapidly; it appeared to be a weak frontier trend. Its space lies in the differentiation it creates with ARM, which cannot be easily changed: ARM is like a lavish banquet already served; whether you can eat it or not, you have to pay that much money. ARM’s licensing agreement does not allow customers to arbitrarily change or customize the instruction set; RISC-V, on the other hand, provides you with a menu, allowing you to order freely without paying. This is attractive to commercial companies looking to reduce costs and increase product flexibility.

RISC-V is particularly suitable for lower-performance, simpler products, such as embedded CPUs and MCUs (microcontrollers), which are mainly used in IoT devices like smart speakers and fitness bands. At that time, the software toolchain for RISC-V was not yet mature, making it difficult to enter scenarios requiring more supporting software, such as mobile phones and computers; IoT chips are also more sensitive to costs, amplifying RISC-V’s advantage of being free.

The Chinese chip industry quickly followed the RISC-V trend. Companies like Espressif, which mainly produce Wi-Fi and Bluetooth chips, and Zhongtian Micro, which produces embedded CPUs, became members of the RISC-V Foundation in 2016, the second year after its establishment. That same year, the first RISC-V International Workshop was held in China, with over 270 registered participants, and the auditorium, which could accommodate more than 300 people, was packed.

The founder of China’s first RISC-V community, CNRV, Guo Xiongfei, summarized in a blog post in 2017: “Many of the domestic RISC-V participants are private enterprises, and their level of participation is not inferior to that of research institutions. Unlike in the past, where only a few were funded by the state and local governments. This is inevitably a profound industrial and market-driven behavior.”

Alibaba was one of the first Chinese tech giants to invest in RISC-V. In 2017, Alibaba acquired Zhongtian Micro, absorbing its RISC-V team. In 2018, Alibaba integrated the chip team from Damo Academy and Zhongtian Micro to establish a chip subsidiary, Pingtouge. The following year, Pingtouge launched the RISC-V CPU IP core Xuantie C910, which can be used in various IoT, 5G, and edge AI scenarios such as smart cameras and smart speakers. By the end of 2021, shipments of CPUs based on Xuantie had reached 2.5 billion units, contributing to a quarter of RISC-V’s total shipment of 10 billion units.

Xuantie has driven more Chinese chip companies to develop RISC-V products, such as Allwinner Technology, which established a RISC-V department in 2019 and developed the video decoding chip D1 based on Xuantie.

A number of Chinese startups have also been established. In 2018, to better promote its business in China, SiFive established a joint venture with a local team, Shanghai Saifang Technology, which has the distribution rights for SiFive IP and achieved sales of 40 million RMB in its second year.

Researchers Zhang Lei and Wang Yuantao from the Ubiquitous Computing Systems Research Center at the Institute of Computing Technology, Chinese Academy of Sciences, who are also students of Patterson, began attempting to design chips using RISC-V and tape out since 2014. In March 2018, the two co-founded Zhongke Wuqishi.

In August of the same year, Tan Zhangxi sold the lidar chip company OURS, which he had previously founded in the U.S., to the well-known autonomous driving company Aurora and returned to China to establish Ruisi Xinke, believing that there were far more opportunities to make chips in China than in the U.S. A month later, Hu Zhenbo, the R&D manager of the New Thinking ARC series processor core and author of the first RISC-V processor design book in China, established ChipRise Technology in Wuhan.

Some larger companies are also incubating new RISC-V businesses. In September 2019, Yiswei Technology Group established a subsidiary, Yiswei Computing, to enter the RISC-V field; in January 2020, a co-founder of a certain company established SuanNeng Technology, with a team coming from the original AI-specific business. These are two private enterprises with very different backgrounds. Yiswei Technology was founded by Wang Dongsheng, who had long presided over state-owned enterprises, while the latter originated from the cryptocurrency boom in 2017, mainly manufacturing mining chips and machines, while also operating mining pools and farms, with a solid financial foundation for new business investments.

At this time, many of the companies established initially focused on IoT RISC-V IP cores or chips. For example, Zhongke Wuqishi provides IoT chips and development platforms based on RISC-V, and Yiswei Computing develops RISC-V embedded CPUs. Zhang Lei told LatePost that the IoT product market is highly fragmented with diverse demands, and chip design needs to be more flexible, making RISC-V, characterized by modularity, well-suited for this field.

Outside of China, the global industry is also applying RISC-V to chips with relatively low performance and software ecosystem requirements, which was originally the market for ARM’s M series and other IPs.

Western Digital has been using RISC-V chips in solid-state drive controllers since 2017, with annual shipments exceeding 1 billion units. Qualcomm has been using RISC-V control and security cores in its SoCs (System On a Chip) since the launch of the Snapdragon 865 in 2019; Apple has also started replacing ARM architecture controllers with RISC-V in small modules that do not carry major user functions, such as Wi-Fi, Bluetooth, and charging interfaces. By the end of 2022, Qualcomm had shipped 650 million RISC-V cores.

Early-stage investment firm YaoTu Capital’s founding partner Bai Zongyi categorized the application scenarios for RISC-V chips into three types: first, consumer-grade MCUs and hardware control chips with low computing power and simple designs, which have been commercialized on a large scale but face thin profits and competition from large companies; second, edge-side CPU/AI chips with relatively high computing power requirements, such as chips for processing visual information; and the third type involves scenarios with even higher computing power requirements, such as server CPUs, but achieving this still requires the software and developer ecosystem to mature further.

He believes that if a startup has strong high-performance RISC-V IP development capabilities and SoC chip design capabilities, the best opportunity lies in the second category, which is where RISC-V’s performance and ecosystem can currently reach, a market with certain technical barriers, scale, and profit potential.

Originally, RISC-V might have gradually accumulated more developers, improved the toolchain, expanded the ecosystem, and slowly and painstakingly entered higher-end scenarios such as computers, mobile phones, and servers based on IoT and edge high-performance chips. However, two forces that emerged almost simultaneously have dramatically changed the trajectory of RISC-V’s fate, accelerating its growth rhythm globally, especially in the Chinese market.

Great Power Competition

The first significant driving force accelerating RISC-V is the increasingly fierce Sino-U.S. technological competition, with a key point being the chip export restrictions imposed by the U.S. government in October 2022.

At that time, the market’s focus was on the imminent supply cut of high-end GPUs A100 and H100 used for AI computing in data centers, but the actual restrictions also affected high-end server CPUs. To meet the rapidly exploding demand for AI computing power, not only GPUs are needed, but also CPUs, which are the task scheduling hub in servers. Supercomputers used for cutting-edge scientific research also require server CPUs.

Intel was naturally affected, and the British company Arm was not spared either. The new restrictions imposed by the U.S. government are based on indicators such as computing power and bandwidth, with products exceeding the limits being affected, and licenses required for over 40 countries outside the U.S. According to a report by the Financial Times last December, Arm had suspended licensing its Neoverse server CPU architecture to companies in mainland China, and from February this year, companies in mainland China must apply for permission to purchase Neoverse licenses.

Under the new restrictions, RISC-V has become the best remaining choice: it is not controlled by a single country or commercial entity and is aligned with the global chip industry, avoiding the risks of closed-door development.

Therefore, since 2020, especially after 2022, the trend in China’s RISC-V industry has been to challenge higher-end, more powerful markets in advance, especially server CPUs.

Alibaba’s Pingtouge has launched three series of eight RISC-V CPU cores, among which Xuantie C910 can also be used to develop server CPUs for high-performance scenarios such as AI.

It is understood that another internet giant that began exploring self-developed chips in 2020 has adjusted its R&D approach, shifting from procuring ARM CPU IP cores and developing on that basis to directly developing server CPU IP cores and buses (data transmission channels between CPUs and memory or other devices) based on RISC-V code, forming a more complete product.

Some previously established startups have begun to increase their server CPU product lines, such as Saifang Technology, which released the high-performance RISC-V IP “Fang·Tianshu” at the end of 2021, targeting scenarios including servers and data centers; SuanNeng Technology began developing RISC-V AI server CPUs in 2022, with its first product using Pingtouge’s Xuantie C910 IP core.

Newly established companies are directly challenging the server CPU direction. At the end of 2021, Chen Zhijian, the main developer and application leader of Pingtouge’s Xuantie series, and Sun Yanbang, the RISC-V leader at Allwinner Technology, co-founded Jindie Space, with the first generation of products being embedded CPUs, now in development for server CPUs. Blue Core Computing, established in May this year, is also focused on RISC-V server CPUs, founded by Lu Shan, the former head of the RISC-V server chip project at ByteDance, who has also worked at Qualcomm and Intel and is an expert on the advisory committee of the China Open Instruction (RISC-V) Alliance.

Among Chinese startups, SuanNeng is progressing the fastest in developing server CPUs. Its first server CPU product, SOPHON SG2042, was released in March this year, using the Pingtouge Xuantie C910 core, and has already secured its first batch of customers, including operators and universities, such as Shandong University, which has purchased 1,024 SuanNeng CPUs for simulation computing.

There is competition among chip companies in China, as well as between chip companies and cloud vendors and tech giants willing to develop their own chips. However, overall, many companies investing in RISC-V are cooperating more than competing; their common adversaries are ARM and x86, especially x86. Until last year, x86 still accounted for 90% of the server CPU market.

These companies share a favorable environment. Customer procurement willingness is strengthening, demand from central state-owned enterprises is being stimulated, and cloud computing companies are also considering domestic solutions more from the perspective of supply chain security. A company developing RISC-V server storage and interconnect chips told LatePost, “In the past, when customers came to you, they asked about price and usage scenarios; this year, customers will directly ask, do you have RISC-V chips?”

Ecological barriers are gradually dissolving under the joint efforts of all parties. An engineer at the Institute of Computing Technology, Chinese Academy of Sciences, told LatePost that in early 2018, when they were developing compilers for RISC-V chips, the available toolchains and supporting software were almost zero, and they had to develop software tools from scratch. By the second half of 2023, the RISC-V compiler, debugger, and various toolchain components are relatively complete, allowing developers to get started more quickly; a number of companies in the industrial chain have also been established, such as Kampaile providing IDEs and Zhaosong Technology providing editors.

Since 2017, Alibaba’s Pingtouge has promoted the establishment of 29 global RISC-V standards, the most among Chinese companies. In October 2021, before Android officially supported RISC-V, Pingtouge was the first in the world to complete the overall adaptation of RISC-V with Android; Pingtouge has also adapted mainstream operating systems such as Ubuntu, Tongxin, and Fedora, which will promote server manufacturers and computer manufacturers to procure RISC-V chips.

In March this year, Pingtouge held the first Xuantie RISC-V Ecological Conference, with hundreds of domestic and foreign companies participating, and the exhibition area was crowded with practitioners exchanging ideas.

Chinese universities and research institutions are investing in talent cultivation, which has a slower return on investment. Bao Yungang, secretary-general of the China Open Instruction Ecosystem (RISC-V) Alliance and a researcher at the Institute of Computing Technology, Chinese Academy of Sciences, promoted the establishment of the “One Chip, One Life” program in 2019, introducing chip development into undergraduate education. In June 2020, the first five undergraduate students in the “One Chip, One Life” program completed the entire process from design to tape-out and production, graduating with their own designed chips. Last year, the third phase of the “One Chip, One Life” program saw over 700 applicants.

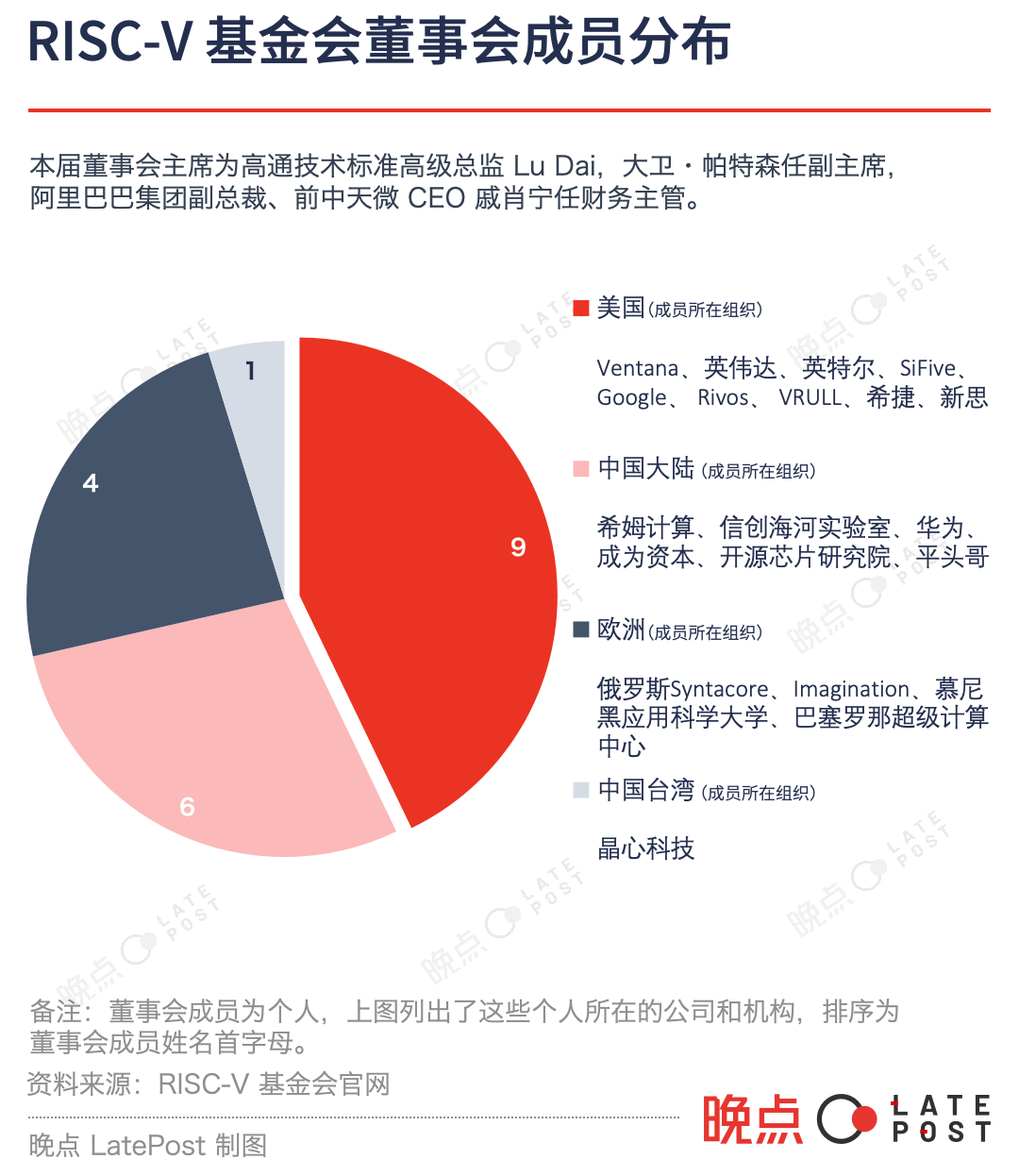

The RISC-V Foundation welcomes the participation of Chinese forces. To dispel concerns among Chinese and Russian members about potential geopolitical impacts, in 2019, the RISC-V Foundation moved its registration from the U.S. to the neutral country of Switzerland. “The board of directors of the foundation unanimously agreed to this move,” said RISC-V Foundation CEO Calista Redmond.

Patterson and Asanovic have also visited China from time to time to engage with the industry. A chip industry practitioner who has interacted with them commented: “As long as the RISC-V ecosystem can thrive, they don’t care who makes it happen.”

By the end of 2019, the RISC-V Foundation had 435 members, which grew to 3,180 by the end of 2022, and exceeded 4,000 this year, with nearly half of the members from China; among the 22 senior members, 12 are from mainland China; and among the 20 board members, 6 are from China, whereas all board members were from the U.S. at the end of 2019.

At the beginning of this year, the Chinese Ministry of Science and Technology and the National Natural Science Foundation of China announced a call for proposals related to RISC-V research. Bao Yungang commented that in the past few years, most RISC-V work was completed from the bottom up, and the government’s attention and support represent a significant change.

A founder of a RISC-V company commented that now at least dozens of companies in China claim to be working on RISC-V CPUs: “Pigs are lining up to fly.”

On the other hand, many practitioners are well aware that the large-scale commercialization of RISC-V server CPUs will not happen immediately.

High-end chip development requires significant investment, and a sufficient market scale is needed to form a positive cycle of “revenue → profit → R&D.” A company that has released server CPU products and secured early customers believes that 2025 could be a turning point, expecting that by then, servers using RISC-V CPUs could account for 1% of the total server market, corresponding to an $8 billion server market scale.

An engineer from a major internet company observed from the customer’s perspective that the stability of RISC-V server CPUs still needs to be verified: “Just because 1 million CPUs run without issues doesn’t guarantee that 10 million will also run without issues.” Tech giants tend to prefer conservative solutions when making large-scale purchases of data center chips.

A CEO of a RISC-V company compared the process of ARM entering the server market: After 2013, companies like Qualcomm attempted this path but failed to break through; the real turning point was when cloud computing giant Amazon AWS released and began using its self-developed ARM server CPU Graviton in 2019. Similarly, RISC-V’s entry into the server market will also require support from key large customers, but he believes this cannot be achieved through forced procurement by state-owned enterprises; rather, it should encourage market competition.

“Holding on to it is useless; the companies that are propped up will ultimately hit a dead end. It’s better to let everyone compete first and see how the top one or two perform,” he said.

Global Willingness

Outside of China, the global RISC-V ecosystem is also accelerating its development, directly driven by ARM’s changes; the deeper motivation is that after experiencing long-term monopolies at the instruction set level, chip design companies and demanders are seeking more open and cost-effective alternatives.

In recent years, ARM, originally mainly used in mobile devices, has gradually entered the computer and server markets with the support of companies like Apple and Amazon, challenging Intel’s dominance in the x86 market.

However, ARM, which was acquired by SoftBank and then went public again, now faces greater profit pressure. According to a report by the Financial Times in March this year, ARM plans to change its charging model from charging licensing fees based on chip value to charging based on the final device value. This will significantly increase licensing fees—Qualcomm’s average mobile chip price is $40, while the average smartphone price exceeds $300. ARM also plans to prohibit companies like Qualcomm from replacing and adding GPU, NPU, and ISP submodules starting in 2024, which is similar to forced bundling sales, further limiting the freedom of chip design companies.

This is pushing ARM’s customers to accelerate their departure, giving RISC-V more support from major players.

In June of this year, 13 companies, including Google, Intel, Pingtouge, Samsung, MediaTek, and Qualcomm, launched a global RISC-V software ecosystem initiative called “RISE” to promote the implementation of RISC-V processors in fields such as mobile communications, data centers, edge computing, and autonomous driving. Two months later, Infineon, Qualcomm, Bosch, Nordic Semiconductor, and NXP announced that they would jointly establish a new RISC-V company in Germany, initially focusing on automotive chips and later expanding to mobile phones and IoT scenarios.

At the end of October, Android officially announced support for RISC-V. Android currently supports over 3 billion mobile devices globally, adding billions of potential users for RISC-V. Google has also taken action, announcing in October this year a collaboration with Qualcomm to develop RISC-V chips for wearable devices, which will be used in the next generation of Google Wear OS watches.

The RISC-V entrepreneurial ecosystem in Europe and America is also becoming more active. Ventana, a U.S. company founded in 2018, released the high-performance server CPU Veyron V1 in January this year, one of the few companies that can provide a complete solution including the bus, helping to increase customer procurement willingness; SiFive also released a new RISC-V CPU core P870 in October, which is one of the most powerful RISC-V CPUs available.

Jim Keller, a well-known chip engineer who has participated in the design of Apple’s A series and AMD’s Zen architecture, joined the Canadian AI chip startup Tenstorrent in 2021. This company is developing RISC-V video codec chips and server CPUs. In May of this year, Tenstorrent announced its video codec chips would collaborate with LG, and in August, it received $100 million in investment from Hyundai Group and Samsung’s investment fund.

“I believe open source will win, just as once people turn to Linux, they won’t look back; it’s a one-way street,” Jim Keller said in an interview this year regarding RISC-V.

Calista Redmond, CEO of the RISC-V International Foundation, stated in September this year that there are more startups in the RISC-V field than in any other architecture in history.

Driven by the ideals of open-source technology or the desire to make big profits, this group believes that a globally cooperative and open chip industry is a better chip industry. They are collectively resisting a more closed and fragmented environment and are likely to break through the limitations.

In October this year, Reuters reported that several U.S. lawmakers requested the Biden administration to take action: if U.S. companies want to collaborate with Chinese companies on RISC-V technology, they must obtain permission in advance.

Most practitioners believe that even if such restrictions occur, it will be difficult to curb the momentum of RISC-V’s development. Like technologies such as 5G, Wi-Fi, and USB, RISC-V has gradually become a global common standard. The U.S. can restrict a product, but it is difficult to restrict a standard. Chen Zhijian, founder of Jindie Space, believes that even if a ban comes, it will at most only limit U.S. companies from selling RISC-V IP to Chinese companies, but it cannot restrict China from using the RISC-V standard, which would instead weaken the competitiveness of U.S. companies and shrink their market, benefiting Chinese companies.

The Chinese chip industry now needs to reduce its dependence on the U.S. across the entire chain from devices, materials, manufacturing to design. The instruction set layer where RISC-V resides does not involve manufacturing issues, but breakthroughs and autonomy in this area remain an important piece of the puzzle.

The past open-source movements in the semiconductor field have been very weak. In universities, new instruction sets are written every year, mainly for teaching demonstrations, and they have historically struggled to transition from campus to industry.

Now, in a rapidly changing environment, people from different countries and regions around the world, driven by technological, commercial, and security considerations, mixed with speculation, hype, and competition for profits and control, have created a realistic space for the ideals of open source and openness.

This is one of the few good news stories in the increasingly harsh chip and global technological cooperation environment: the open-source ideal in the semiconductor field is closer to realization than ever before. Behind it is a simple but often obscured rule: openness, communication, and cooperation can accelerate the overall efficiency of technology and innovation.