On July 17, 2025, the 2025 RISC-V China Summit officially opened in Zhangjiang, Shanghai, China. Professor Bao Yungang, Deputy Director of the Institute of Computing Technology, Chinese Academy of Sciences, Secretary-General of the RISC-V Open Instruction Ecosystem Alliance, and Chief Scientist at the Beijing Open Source Chip Research Institute, shared his observations and thoughts on the industrial applications of RISC-V, and introduced a series of high-performance RISC-V IP cores, interconnect IP, and computing subsystems that he led in development.

△Professor Bao Yungang

1. The Future of RISC-V is Bright, but Real-World Implementation Faces Many Challenges

According to SHD Group’s forecast, the global market size will reach $92.7 billion by 2030, with an average annual growth rate of 47.4%. The RISC-V Foundation also predicts that from 2021 to 2027, Chinese RISC-V cores will continue to account for 50% of global shipments. Although these forecasts suggest a bright future for RISC-V and significant development opportunities for the Chinese RISC-V industry, promoting RISC-V currently faces various difficulties.

Professor Bao Yungang also pointed out that RISC-V will become a mainstream ISA in the future, but there are many challenges in reality. For example, some companies find that their downstream customers do not know what RISC-V is when promoting it. Others ask why they should switch to RISC-V when they are already using ARM effectively. Some companies inquire about the scenarios that RISC-V chips target, while others mention that the software their customers need cannot be installed. Additionally, some companies ask if there are any Turn-Key solutions and how much cheaper they are compared to ARM. Others question how software development can be profitable when there are costs associated with porting and developing software on RISC-V chips. Lastly, some companies note that while many people understand ARM solutions, finding RISC-V technical support is challenging.

Professor Bao summarized these issues into four categories:

First, there is a lack of products and solutions. Currently, there are still too few competitive RISC-V products and solutions in the market, giving a feeling of much noise but little action. For instance, there is currently no RISC-V chip that can match the performance of the RK3588 while being 25% cheaper.

Second, the toolbox is relatively lacking. The RISC-V software and hardware toolbox is not rich enough and needs to quickly achieve efficiency in terms of speed, quality, and cost. For example, the OpenEuler software package has over 30,000 packages for X86 and ARM, but less than 3,000 for RISC-V.

Third, there is a shortage of talent. There is a lack of talent at all levels, including chip design, verification, solutions, and technical support.

Fourth, there is a lack of benchmark cases, which are needed to build industry confidence. Currently, there are no large-scale deployments of high-end RISC-V chip cases.

2. How to Solve the Challenges of RISC-V Implementation?

So, how can we address these various issues?

Professor Bao Yungang shared his four viewpoints:

First, many companies believe that RISC-V is a direct replacement for ARM, which is incorrect. This perspective buries the true advantages of RISC-V and does not leverage its openness and customizability.

Second, the openness of RISC-V enables open-source implementations and open-source toolchains, which structurally reduce costs and can foster new business models. Just like in the software field today, open-source software has become the norm, with Linux + RedHat being a very successful solution.

Third, the customizability of RISC-V means we can achieve extreme optimization of hardware and software, lowering development barriers through agile development and fostering new models. For example, today there are 9 million apps worldwide, and developing an app has become very easy. In the future, could we not add two or three more people to create a hardware and software solution? This is not impossible; RISC-V is providing us with such opportunities.

Fourth, AI brings us new opportunities. The new characteristics of computing power demand for AI inference will make RISC-V + AI a new combination in the future.

Fifth, we need to find a new way for software developers to profit. Currently, in the RISC-V ecosystem, the discussions often revolve around RISC-V chip companies making money, with some having gone public and others raising significant funds, but software developers have not benefited from this.

3. Open-Source RISC-V CPU Can Significantly Reduce Chip Design Costsby 33%

In Professor Bao Yungang’s view, in addition to its openness, customizability, and suitability for AI demands, open-source RISC-V CPUs can also significantly reduce chip design costs.

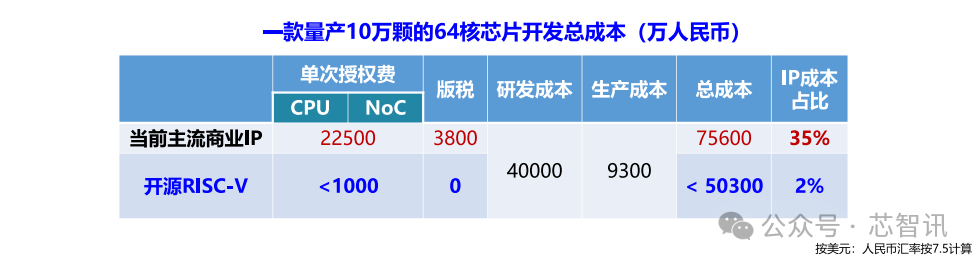

For example, developing a 64-core server chip for mass production of 100,000 units using the traditional Arm licensing model costs about 750 million RMB, with IP licensing fees and royalties accounting for about 250 million RMB, totaling 35%. Among these, the licensing fees for high-performance CPU IP and on-chip interconnect IP total $30 million (225 million RMB); royalties generally account for 2%-4%, with a single-core royalty of about $0.8, totaling $5.12 million (3.8 million RMB) for 100,000 64-core chips.

Professor Bao Yungang stated: “In contrast, if we adopt a collaborative development model based on open-source RISC-V CPUs, it can save enterprises 250 million RMB in R&D costs (a reduction of 33%). Companies can use this money in other areas to create better innovative solutions. These are the new opportunities that RISC-V brings us.”

Additionally, Professor Bao Yungang mentioned that open-source RISC-V CPUs can structurally help companies reduce costs. Currently, 96% of software codebases in open-source software contain original code, with 77% being open-source code. In the future, the proportion of open-source IP in chips is expected to break through 0, and this proportion will continue to rise, which will help the entire industry reduce costs and enhance corporate competitiveness.

4. Latest Progress of the Open Chip Institute in RISC-V Research and Development

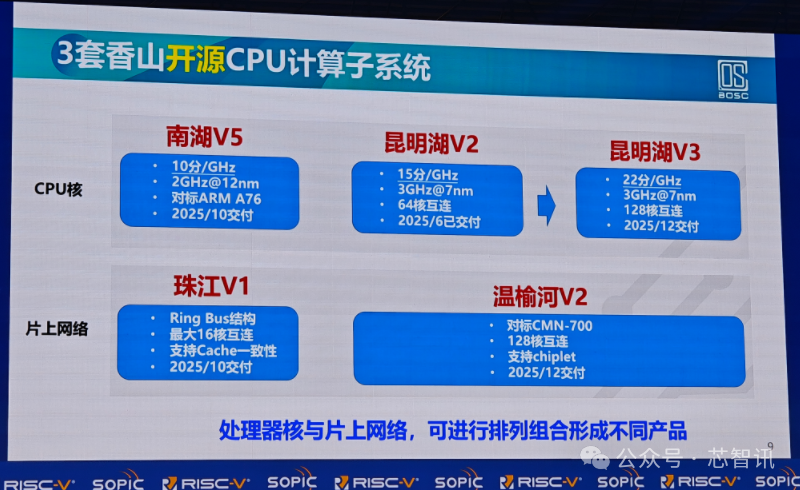

As the largest promoter of domestic open-source RISC-V cores, the Beijing Open Source Chip Research Institute (referred to as “Open Chip Institute”) has launched multiple sets of “Xiangshan” open-source computing subsystems, which include a series of high-performance RISC-V CPU core IPs as well as on-chip interconnect IP.

1. Three High-Performance RISC-V Core IPs: “Kunming Lake” Can Benchmark ARM Neoverse N2

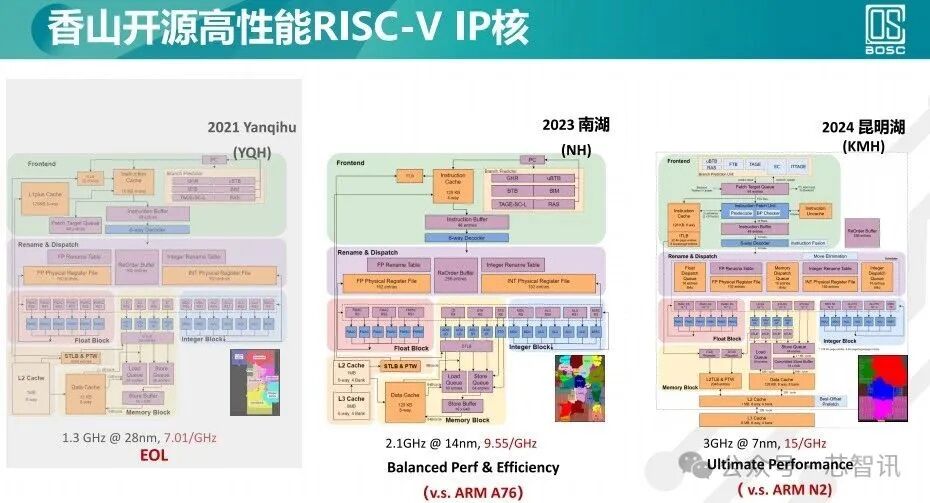

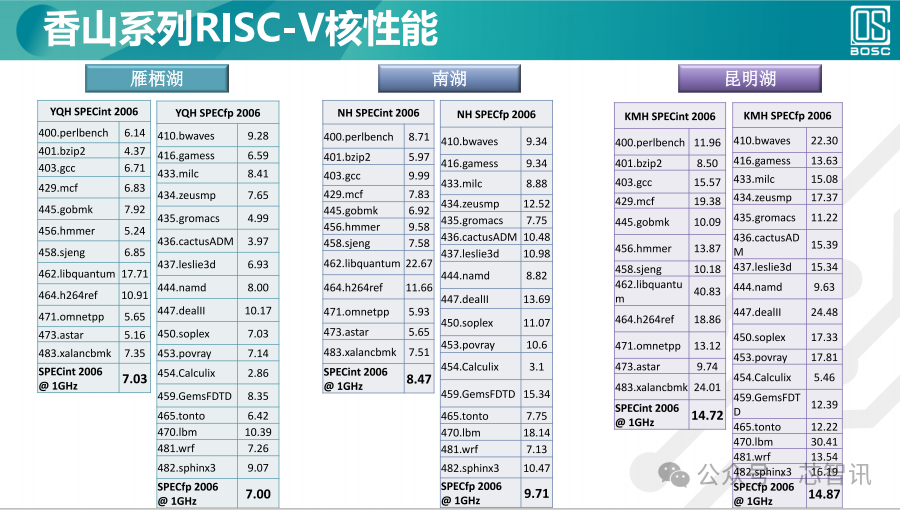

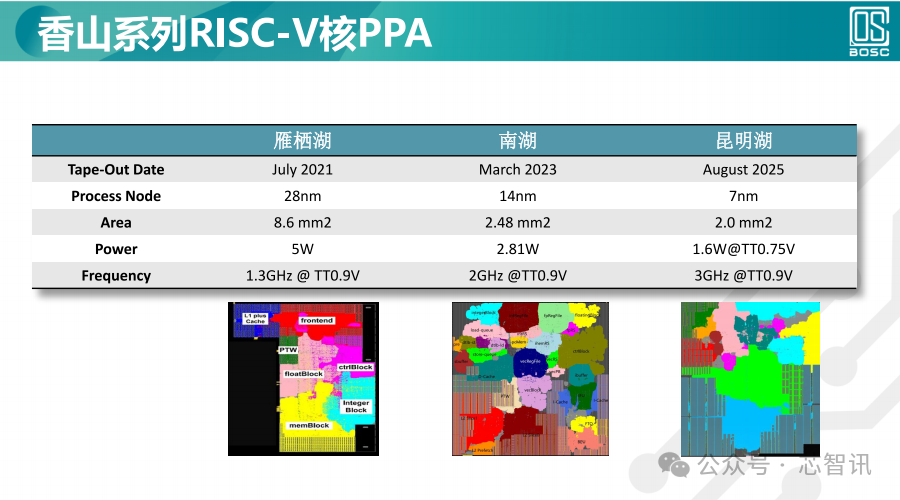

Specifically, in terms of the Xiangshan open-source high-performance RISC-V CPU core IPs, there are mainly three models: Yanqi Lake, Nanhu, and Kunming Lake. Among them, “Nanhu” benchmarks at the level of ARM Cortex-A76, while Kunming Lake benchmarks at the level of ARM Neoverse N2. Moreover, these core IPs are continuously iterating and evolving.

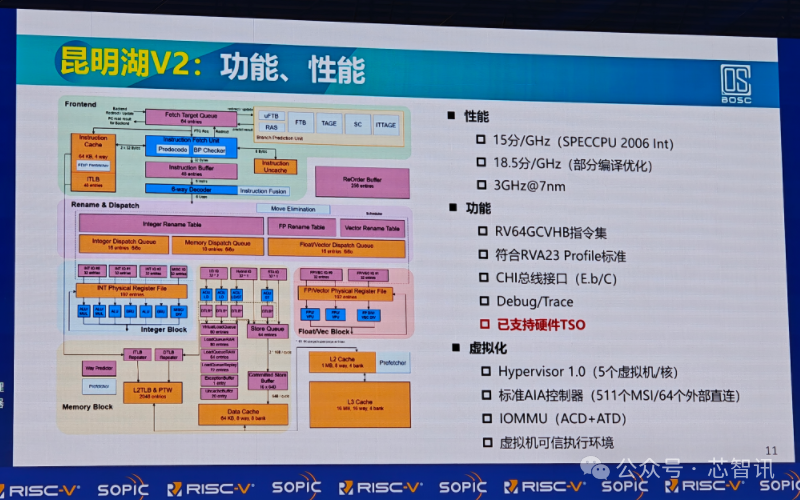

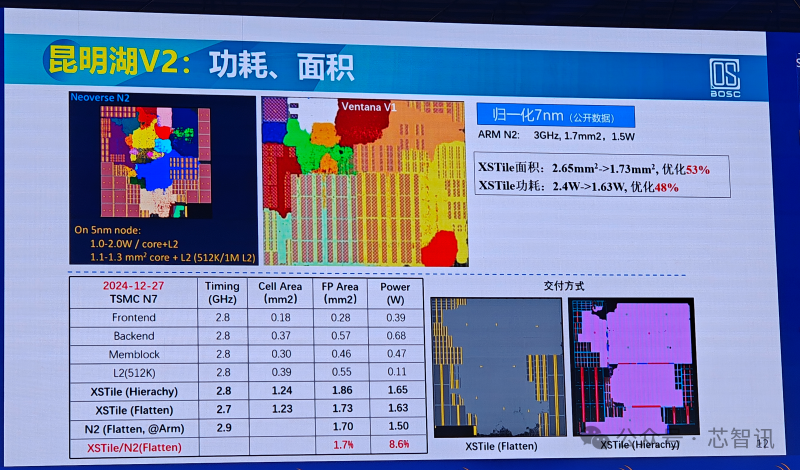

Professor Bao Yungang pointed out that the “Kunming Lake” aimed at the server field has already iterated to version V2, achieving a frequency of 3GHz based on a 7nm process, with a performance of 15 points/GHz (SPEC CPU 2006 int).

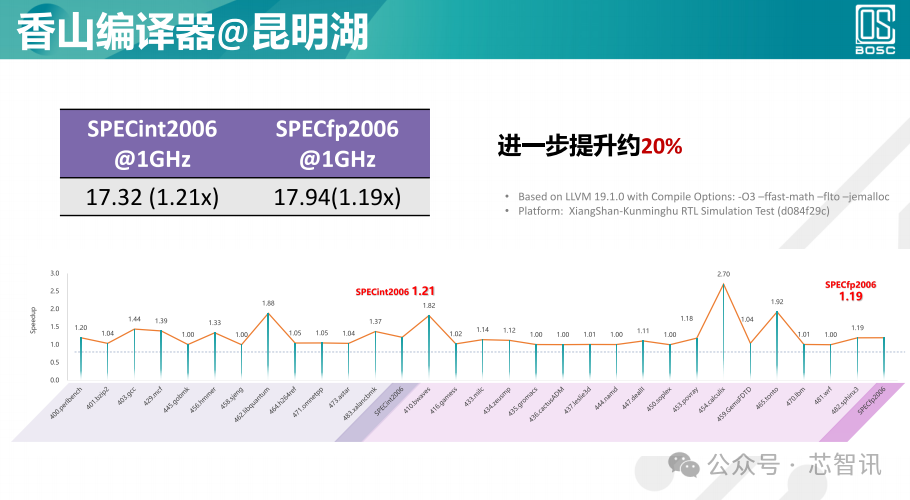

If combined with the “Xiangshan” compiler optimization, the performance of “Kunming Lake V2” can be further improved by 20%, reaching 18.5 points/GHz, and it fully supports the latest RVA23 standard, as well as virtualization.

Compared to ARM Neoverse N2, the performance of “Kunming Lake V2” still has a gap, but it has narrowed to about 8%.

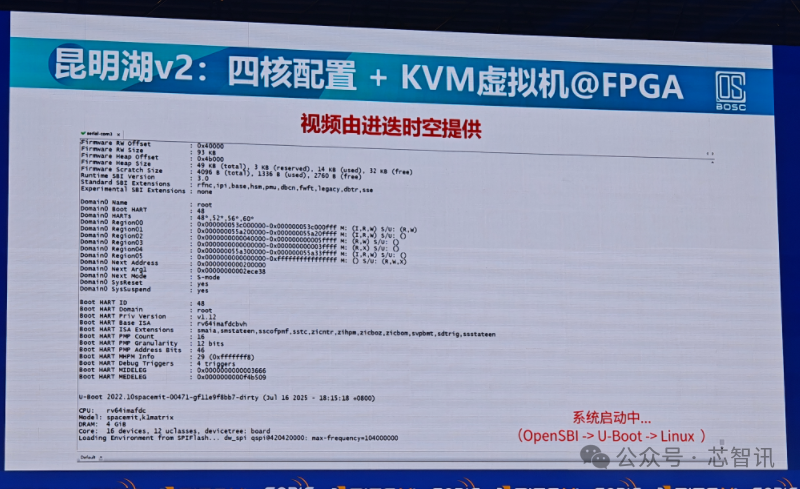

It is reported that Jinde Shikong has integrated the “Xiangshan” core IP into its SoC, with a 4-core configuration, and has successfully booted the virtual machine. It is expected to complete tape-out in September this year, and is currently finalizing the last phase of physical design optimization.

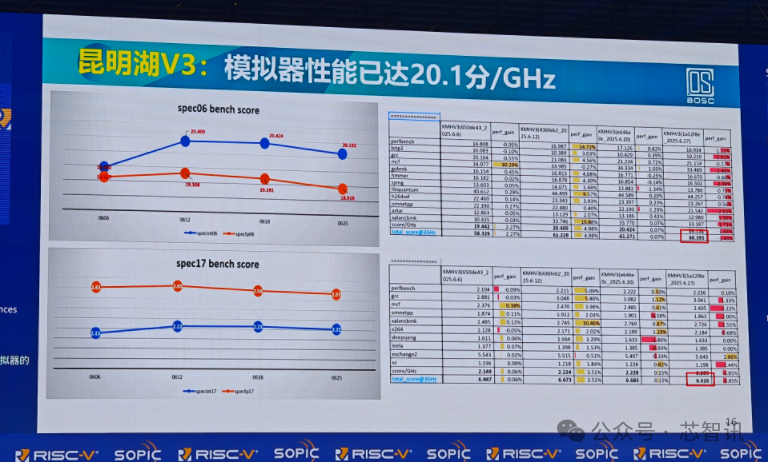

Professor Bao Yungang also revealed that the latest generation of the RISC-V CPU architecture “Kunming Lake V3” is currently under exploration. After discussions with multiple companies, “Kunming Lake V3” will comply with the RVA23 Profile specification, fully supporting CPU/memory/interruption/IO virtualization, with a performance target of 22 points/GHz (SPEC CPU 2006 int) for architectural exploration. Currently, it has achieved 20.1 points/GHz on the simulator, and although there is still a gap to 22 points/GHz, it is expected to reach this target in the next six months with the support of partners.

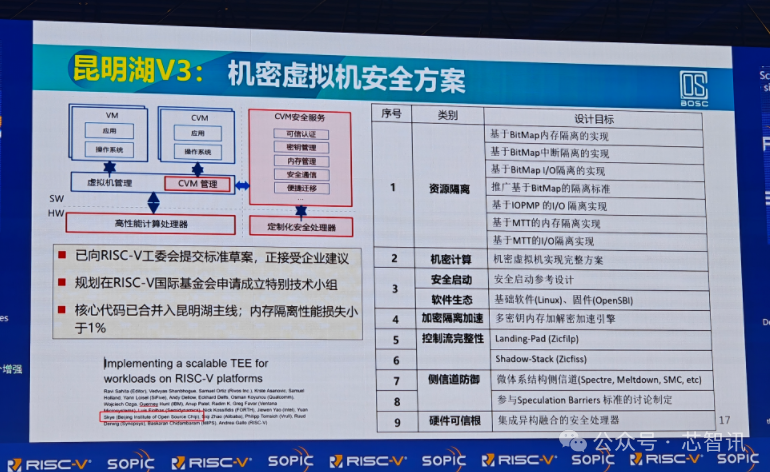

At the same time, “Kunming Lake V3” has also enhanced security features, such as supporting confidential virtual machine security solutions, with memory isolation performance loss of less than 1%. This solution has been submitted to the RISC-V Working Group as a draft standard and is currently accepting corporate suggestions. Additionally, there are plans to apply to the RISC-V International Foundation to establish a special technical group, which is expected to form an international standard in the future.

2. Two On-Chip Network IPs and Computing Subsystem Combinations

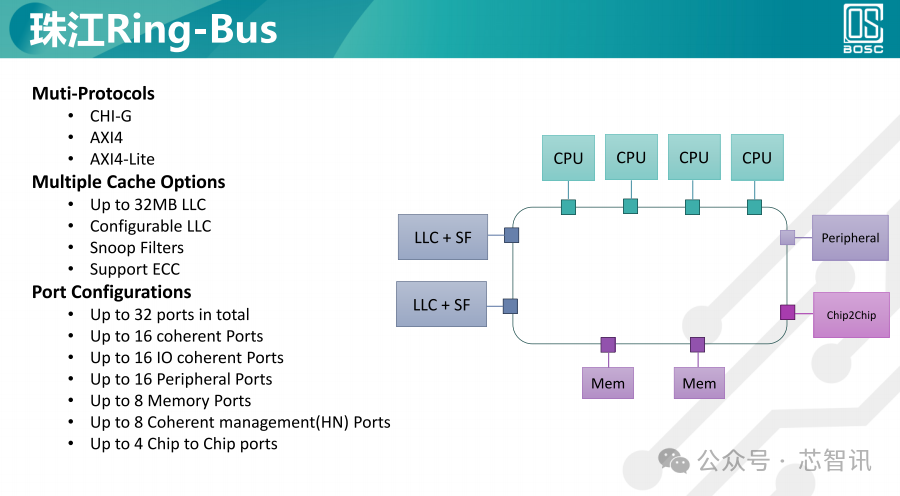

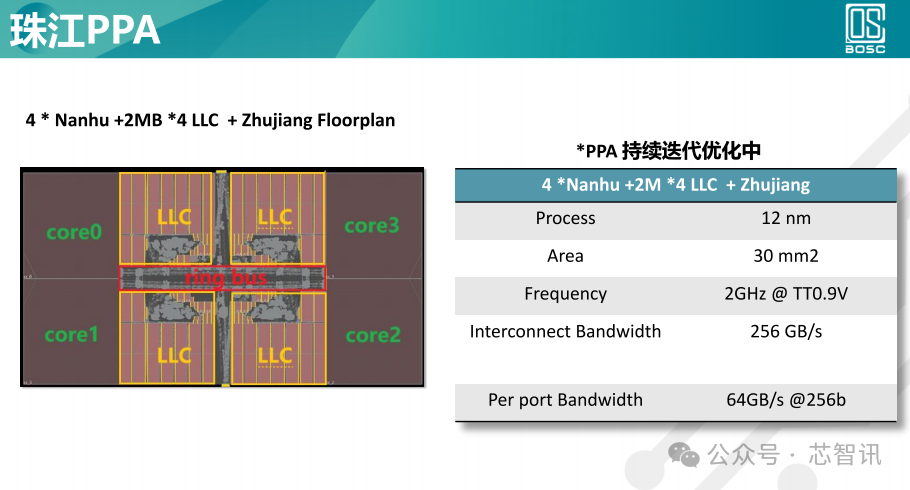

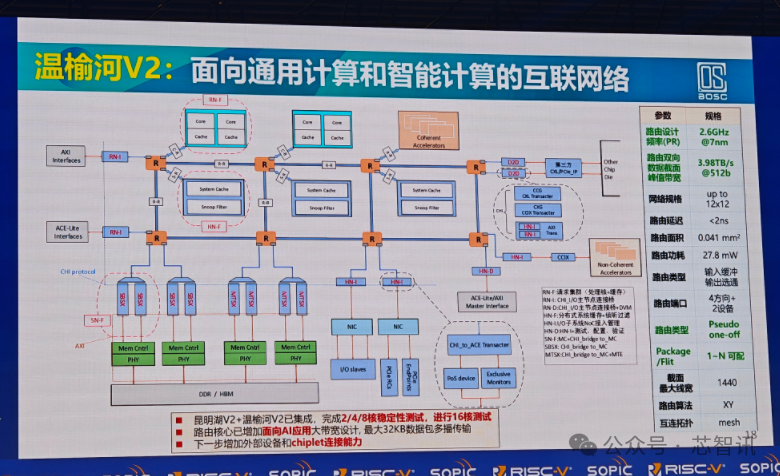

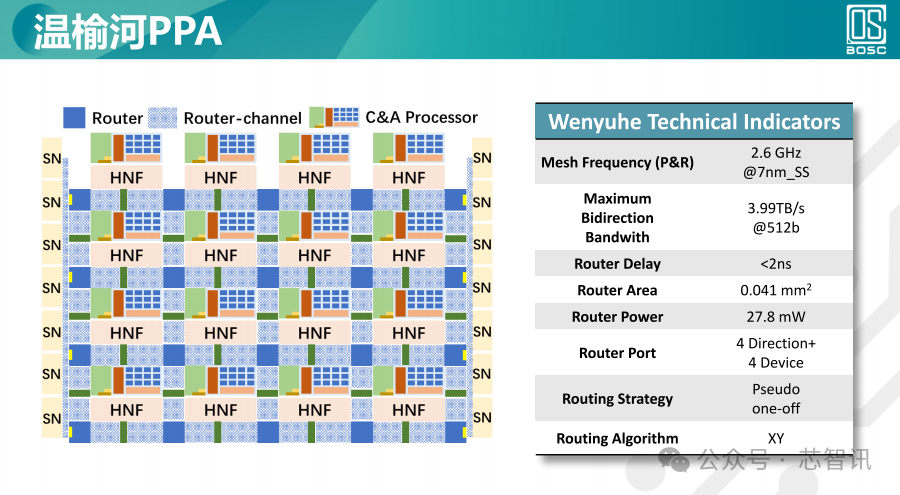

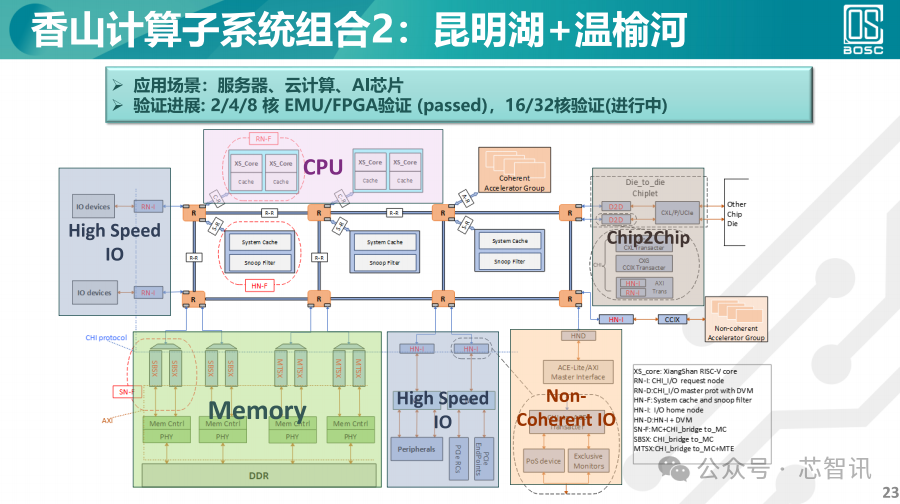

In terms of on-chip network IP, the Open Chip Institute has also launched two IPs, “Pearl River” and “Wenyu River”, which can be arranged and combined to form different products.

Among them, “Wenyu River” has developed to the second generation, which is an interconnect network aimed at general and intelligent computing, supporting a maximum of 12×12 mesh. An important aspect of the design of “Wenyu River” is the special enhancements made for intelligent computing, with routing cores designed for high bandwidth applications in AI, supporting a maximum of 32KB data packet multicast transmission. The Open Chip Institute is also conducting some physical design evaluations.

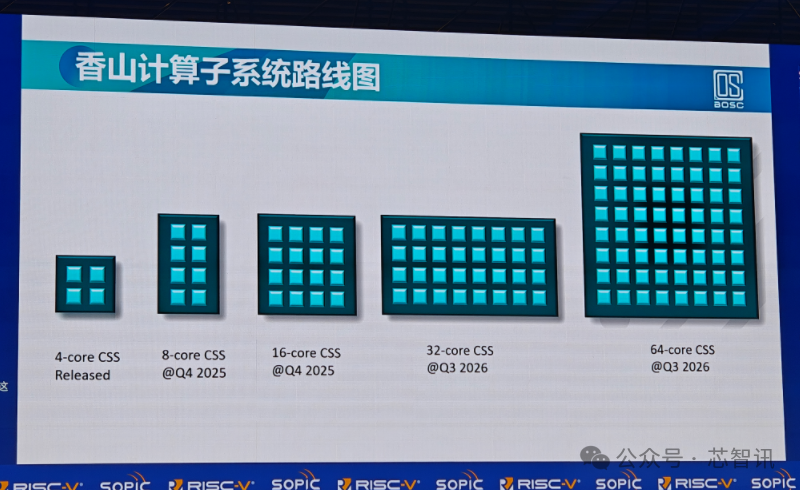

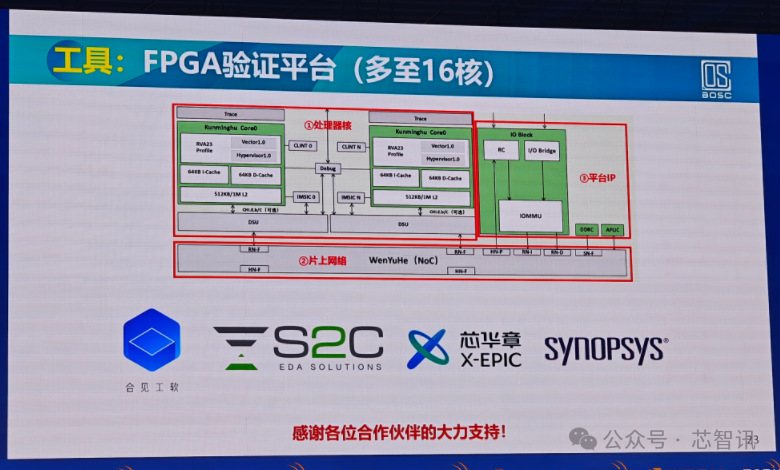

Currently, the Open Chip Institute is working on the “Xiangshan” and “Wenyu River” computing subsystems, having completed stability tests for 2-core, 4-core, and 8-core configurations, with 16-core testing underway. The Open Chip Institute also plans to complete 32-core testing in the third quarter of 2026 and 64-core testing in the same period.

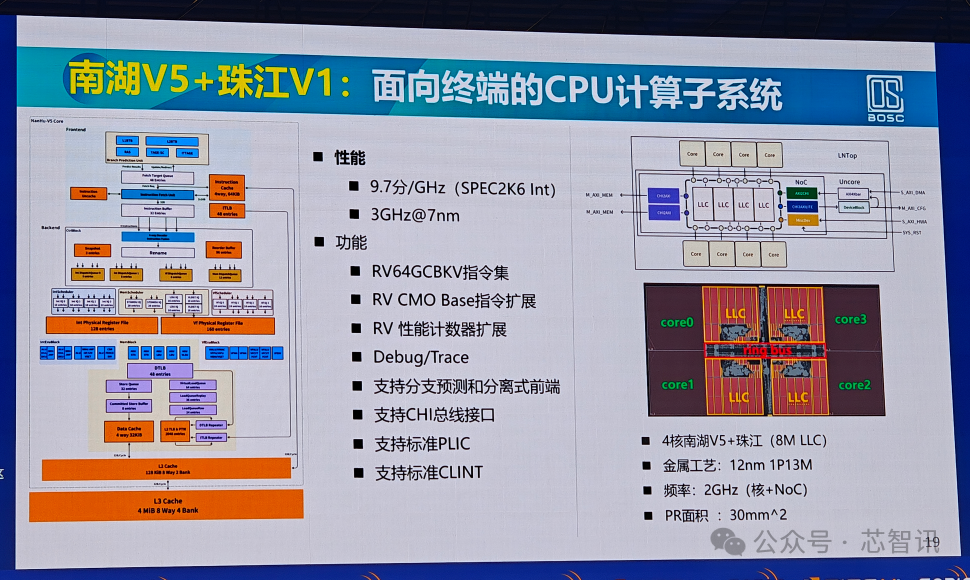

In addition to the computing subsystem designed for the server field, the Open Chip Institute also has a terminal-oriented computing subsystem, “Nanhu V5 + Pearl River V1”, which can achieve a more cost-effective design with lower area and power consumption, suitable for edge computing, AIPC, embodied intelligence, and intelligent driving applications. Currently, 2/4/8-core configurations have been validated, and 16-core validation is ongoing.

5. Open-Source RISC-V CPUs Can Also Achieve High Quality

Many users believe that while open-source RISC-V cores can be obtained for free and save a lot of costs, they often worry about the difficulty of achieving high-quality designs.

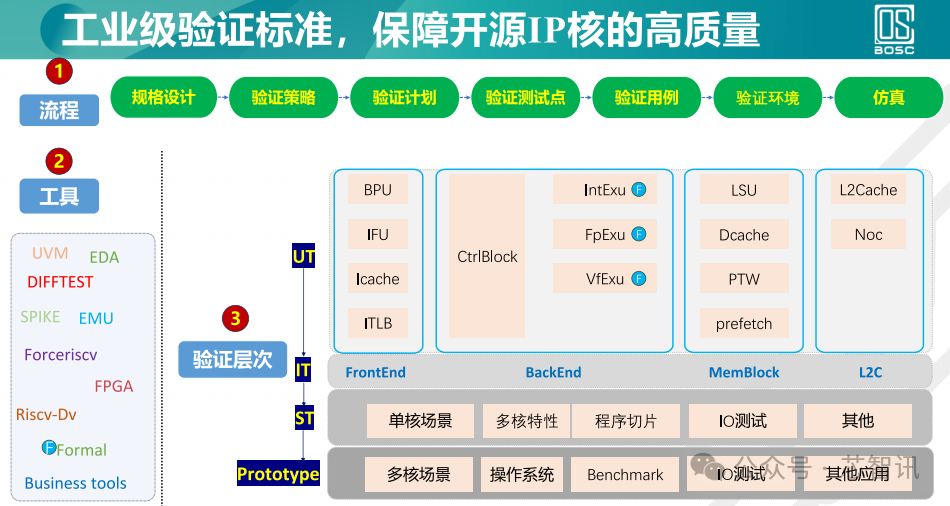

In response, Professor Bao Yungang emphasized, “Open-source does not equate to low quality; open-source can absolutely deliver high-quality product-level outputs. This is because we adopt industrial-grade verification standards.”

It is reported that over the past year, with the support of many companies, “Xiangshan” has undergone extensive testing, with over 20,000 test cases formed, covering everything from unit-level testing to integration testing to system-level testing. Among them, users and companies of “Xiangshan” have contributed nearly 1,600 test cases.

“These test cases have conducted very comprehensive coverage testing, achieving 100% functional point coverage for various modules, as well as integration testing across multiple IT modules and system-level multi-core testing, which are all in full progress and have basically completed complete test coverage,” said Professor Bao Yungang.

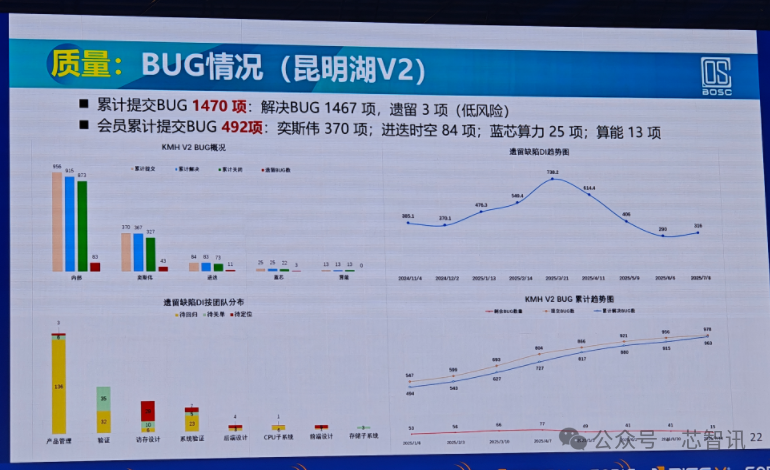

In terms of bug resolution, for example, “Kunming Lake V2” has cumulatively completed the discovery and repair of 1,470 bugs. Companies such as Yiswei, Jinde Shikong, Lanchip Computing, and Suan Neng have contributed one-third of the bug discoveries, with nearly 500 bugs.

“In this process, we would like to especially thank the support of our partner companies. For instance, in the Kunming Lake V2 version, partners include Yiswei, Suan Neng, Jinde Shikong, and Lanchip Computing. Partners for Kunming Lake V3 include Tencent, Jinde Shikong, ZTE Microelectronics, and Zhihe Computing. Moving forward, we hope to have more companies participate, just like Linux did back in the day, which became a mainline open-source operating system through collective efforts and supported the development of the industry,” said Professor Bao Yungang.

In terms of testing and verification tools, companies such as Hejian Gongruan, Xinhua Zhang, Synopsys, and Sierxin have provided strong tools for the Open Chip Institute. Professor Bao Yungang emphasized, “Without these tools, we would not be able to conduct large-scale evaluations and testing of 16-core designs; they have provided significant support during the verification process of ‘Xiangshan’.”

Editor: Chip Intelligence – Lang Ke Jian

Previous Exciting Articles$35 Billion! Synopsys Completes Acquisition of Ansys!ASML Earnings Warning, Stock Price Plummets 8.33%!US ITC Rules in Favor of Samsung, BOE OLED May Face Sales Ban?Wentai Technology Chairman, Vice President, and Secretary Resign!H20 Unlocked! Jensen Huang Visits China Again, This Time in a Leather Jacket!Official Announcement! NVIDIA H20 Will Resume Sales to China and Launch New GPU Models!Intel Lays Off 2,329 Employees at Oregon Wafer PlantGlobalFoundries Acquires MIPS, Is It for RISC-V?Deepening for Nearly 40 Years! NXP’s China Strategy Fully Upgraded: Building a Fully Domestic Supply Chain!Huawei Pangu Large Model “Plagiarized” Alibaba Qwen? Official ResponsePlans to Raise 8 Billion Yuan! Moer Thread IPO Accepted: Cumulative Loss Exceeds 5 Billion Yuan Over 3 Years!Plans to Raise 3.9 Billion Yuan! Muxi Shares IPO Accepted: GPU Cumulative Sales Exceed 25,000 Units!Unisoc Completes IPO Counseling Filing: Valuation May Reach 70 Billion Yuan!Pre-investment Valuation of 14 Billion Yuan? Rumored Biran Technology Secures 1.5 Billion Yuan Financing, Plans to IPO in Hong Kong!

For industry communication and cooperation, please add WeChat: icsmart01

Chip Intelligence Official Group: 221807116