Layout

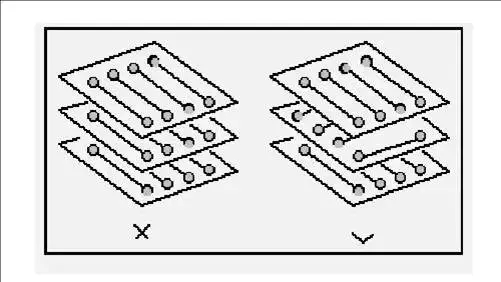

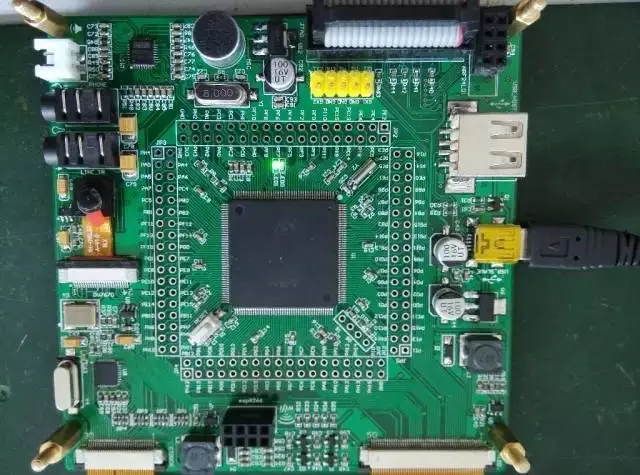

In design, layout is an important aspect. The quality of the layout directly affects the wiring results, so it can be said that a reasonable layout is the first step to successful PCB design. Especially pre-layout, which is the process of considering the entire circuit board, signal flow, heat dissipation, structure, and other architectures. If the pre-layout fails, all subsequent efforts are in vain.

1. Considering the overall success of a product, one must focus on both inherent quality and overall aesthetics; both must be perfected for the product to be considered successful. On a PCB, the layout of components must be balanced, orderly, and cannot be top-heavy or bottom-heavy.

-

Will the PCB deform?

-

Is there a process edge reserved?

-

Is there a MARK point reserved?

-

Is panelization needed?

-

How many layers of the board can ensure impedance control, signal shielding, signal integrity, economy, and feasibility?

2. Eliminate basic errors: Does the printed board size match the processing drawing size?

Can it meet PCB manufacturing process requirements? Are there position marks? Are there conflicts between components in two-dimensional or three-dimensional space? Is the component layout orderly and neat? Is everything laid out? Can frequently replaced components be easily replaced? Is it convenient for the plug-in board to be inserted into the device? Is there adequate distance between thermal-sensitive components and heating components? Is it easy to adjust adjustable components? Is a heatsink installed in areas needing heat dissipation? Is airflow smooth? Is the signal flow smooth and the interconnections shortest? Are plugs, sockets, etc., in conflict with mechanical design? Has the interference problem of the circuits been considered?

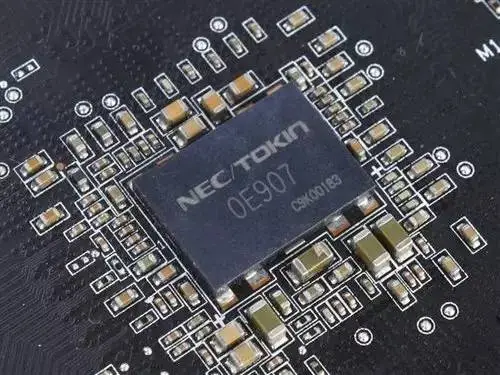

3. Bypass or decoupling capacitors

During wiring, both analog and digital devices require these types of capacitors to be connected close to their power pins with a bypass capacitor, typically valued at 0.1μF. Keep the leads as short as possible to reduce inductance, and place them as close to the device as possible.

Adding bypass or decoupling capacitors on the circuit board, as well as their placement on the board, is basic knowledge for both digital and analog design, but their functions differ.

In analog wiring design, bypass capacitors are usually used for bypassing high-frequency signals on the power supply. Without bypass capacitors, these high-frequency signals can enter sensitive analog chips through the power pins. Generally, the frequency of these high-frequency signals exceeds the ability of analog devices to suppress high-frequency signals.

If bypass capacitors are not used in analog circuits, noise may be introduced into the signal path, and in more severe cases, it may even cause oscillation.

For digital devices like controllers and processors, decoupling capacitors are also needed, but for different reasons. One function of these capacitors is to act as a “mini” charge reservoir, because in digital circuits, switching gate states (i.e., switching) usually requires a large current, and when switching, transient currents are generated on the chip and flow through the circuit board; having this extra “reserve” charge is beneficial. If there is not enough charge during the switching action, significant changes in power supply voltage can occur. Excessive voltage changes can cause digital signal levels to enter an uncertain state, potentially leading to incorrect operation of state machines in digital devices. The switching current flowing through the circuit board traces will cause voltage changes, and due to parasitic inductance in the traces, the voltage change can be calculated using the following formula: V=Ldl/dt where V=voltage change, L=trace inductance, dI=current change through the trace, dt=time of current change. Therefore, for various reasons, applying bypass (or decoupling) capacitors at the power supply or at the power pins of active devices is a very good practice.

4. For input power, if the current is relatively large, it is recommended to reduce the length and area of the traces, and not to run them all over the board.

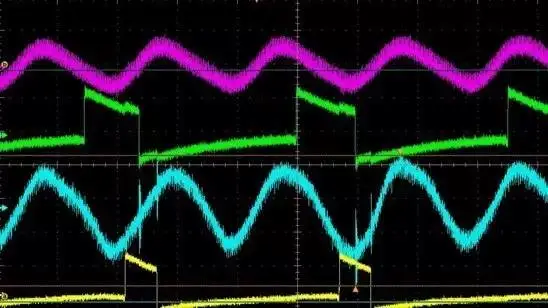

Switching noise on the input couples to the power output plane. The switching noise of the output power MOSFET affects the input power of the previous stage. If there are many large current DC-DC converters on the circuit board, there will be different frequencies and large current high-voltage switching interference.

So we need to minimize the area of the input power to meet the current flow. Therefore, when laying out the power supply, consider avoiding running the input power all over the board.

5. Power and ground lines

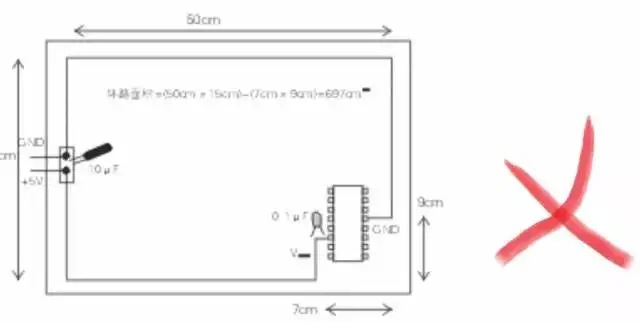

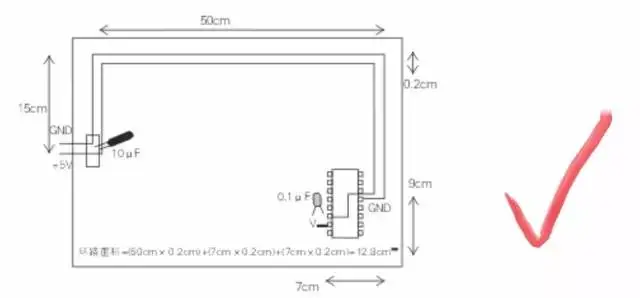

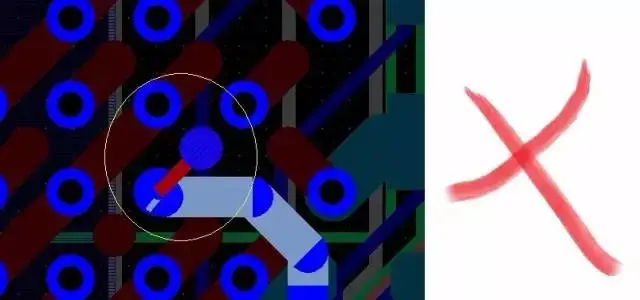

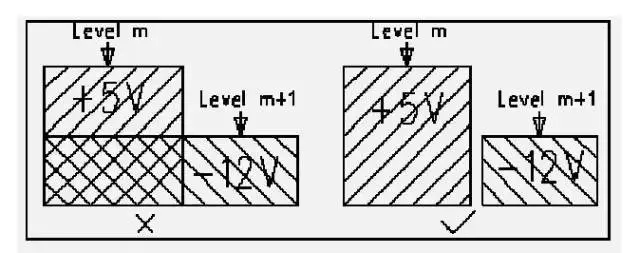

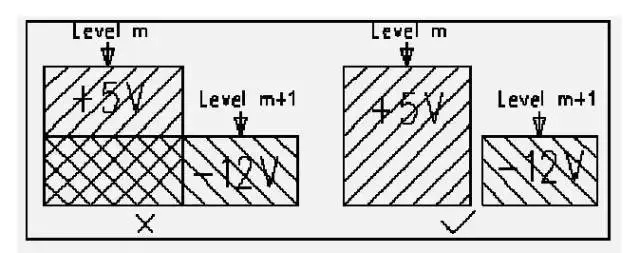

The good positioning of power and ground lines can reduce the possibility of electromagnetic interference (EMI). If the power and ground lines are not properly matched, it can create system loops and likely generate noise. An example of improper PCB design where power and ground lines are mismatched is shown in the figure. On this circuit board, different routes are used to lay out power and ground lines, and due to this improper matching, the electronic components and traces on the circuit board are more likely to be subjected to electromagnetic interference (EMI).

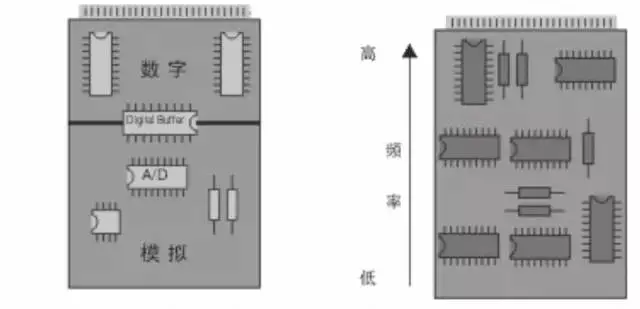

6. Separation of digital and analog

In every PCB design, the noisy parts of the circuit and the “quiet” parts (non-noise parts) must be separated. Generally, digital circuits can tolerate noise interference and are not sensitive to noise (because digital circuits have a large voltage noise margin); conversely, analog circuits have a much smaller voltage noise margin. Among the two, analog circuits are most sensitive to switching noise. In wiring for mixed-signal systems, these two types of circuits should be separated.

The basic knowledge of wiring on circuit boards applies to both analog and digital circuits. A basic rule of thumb is to use a continuous ground plane; this basic principle reduces dI/dt (current change over time) effects in digital circuits, as dI/dt effects can cause ground potential and let noise enter analog circuits. The wiring techniques for digital and analog circuits are fundamentally the same, with one exception. For analog circuits, another point to note is to keep digital signal lines and return loops in the ground plane as far away from the analog circuit as possible. This can be achieved by connecting the analog ground plane separately to the system ground connection point, or placing the analog circuit at the far end of the circuit board, at the end of the traces.This is to minimize the external interference that the signal path is subjected to. This is not necessary for digital circuits, which can tolerate a significant amount of noise on the ground plane without issues.

7. Heat dissipation considerations

During the layout process, consider heat dissipation channels and dead spots;

Do not place heat-sensitive components behind heat sources. Prioritize the layout position of components like DDR that are difficult to dissipate heat. Avoid repeated adjustments due to thermal simulations not passing.

Wiring

In PCB design, wiring is an important step in completing product design; it can be said that all previous preparations are made for it. In the entire PCB, the design process of wiring is the most limited, the most skillful, and the most labor-intensive.

PCB wiring can be single-sided, double-sided, or multi-layered. There are two methods of wiring: automatic wiring and interactive wiring. Before automatic wiring, it is possible to use interactive wiring to pre-wire lines with stricter requirements; the edge lines of the input and output should avoid being adjacent and parallel to avoid reflection interference. Ground isolation should be added if necessary, and the wiring of two adjacent layers should be perpendicular to each other, as parallel wiring easily creates parasitic coupling.

The wiring pass rate of automatic wiring relies on good layout; wiring rules can be preset, including the number of bends in the traces, the number of vias, and the number of steps, etc. Generally, exploratory wiring is performed first to quickly connect short lines, followed by maze wiring, which optimizes the global wiring path of the connections to be wired. It can disconnect already wired lines as needed and try to rewire to improve overall results.

1. Handling of power and ground lines

Even if the wiring throughout the PCB is done well, interference caused by inadequate consideration of power and ground lines can lead to a decrease in product performance and sometimes even affect the success rate of the product. Therefore, the wiring of power and ground lines should be taken seriously to minimize noise interference generated by power and ground lines to ensure product quality.

Every engineer engaged in electronic product design understands the causes of noise generated between power and ground lines. Here, only a description of noise suppression measures will be provided:

(1) It is well known to add decoupling capacitors between power and ground lines. (2) Try to widen the power and ground line widths; it is best for the ground line to be wider than the power line. Their relationship is: ground line > power line > signal line; the signal line width is typically: 0.2-0.3mm, with the finest width reaching 0.05-0.07mm, and the power line width being 1.2-2.5mm. For digital circuit PCBs, a wide ground trace can form a loop, which constitutes a ground network for use (analog circuit grounds cannot be used this way).

(3) Use large copper areas as ground lines, connecting all unused areas of the printed board to ground. Alternatively, create a multi-layer board where power and ground lines each occupy one layer.

2. Common grounding treatment of digital and analog circuits

Nowadays, many PCBs are no longer single-function circuits (digital or analog) but are composed of mixed digital and analog circuits. Therefore, when wiring, one must consider their mutual interference, especially noise interference on the ground line.

Digital circuits have high frequencies, while analog circuits are highly sensitive; for signal lines, high-frequency signal lines should be kept as far away from sensitive analog circuit components as possible. For ground lines, the entire PCB has only one connection point to the outside world, so it is necessary to internally handle the common ground issue between digital and analog circuits, where digital ground and analog ground are actually separated inside the PCB and do not connect with each other, only connecting at the interface with the outside world (such as plugs, etc.). There is a short connection between digital ground and analog ground; please note that there is only one connection point. There are also cases where the PCB does not share a ground, which is determined by system design.

3. Signal lines are laid on the (ground) layer

When wiring in multi-layer printed boards, if there are few remaining lines on the signal layer, adding more layers will cause waste and increase production workload and costs. To resolve this contradiction, consider wiring on the (ground) layer. The power layer should be considered first, followed by the ground layer, as it is best to maintain the integrity of the ground layer.

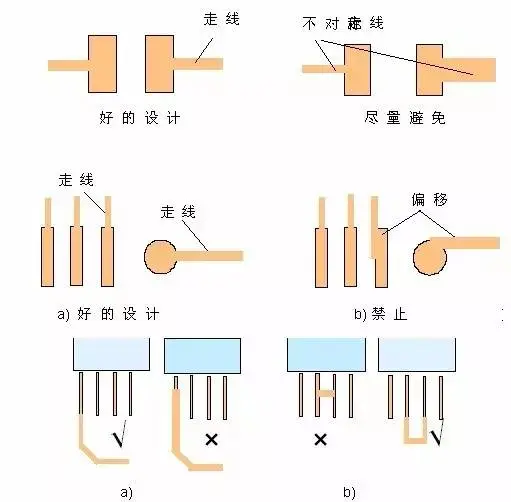

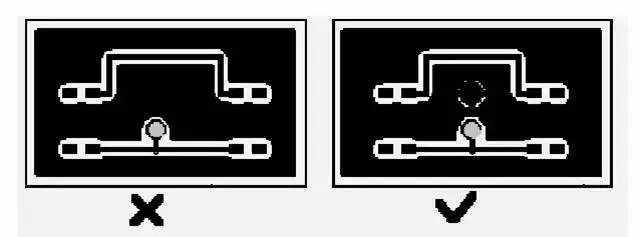

4. Handling of connection legs in large area conductors

In large ground (power) areas, the connection of common component legs needs to be considered comprehensively. In terms of electrical performance, it is better for the pad of the component leg to be fully connected to the copper surface, but there are some adverse hidden dangers for the assembly of component soldering, such as: (1) Soldering requires a high-power heater. (2) It is easy to cause cold solder joints. Therefore, to balance electrical performance and process needs, make a cross-shaped pad, called thermal isolation (heat shield), commonly known as thermal pad; this can greatly reduce the likelihood of cold solder joints caused by excessive heat dispersion during soldering. The processing of component legs in the connection (ground) layer of multi-layer boards is the same.

5. The role of the network system in wiring

In many CAD systems, wiring is determined based on the network system. A dense grid increases the number of paths, but if the steps are too small, the data volume of the graphic field will be too large, which will inevitably require higher storage space for the equipment and greatly affect the computing speed of electronic products. Some paths are ineffective, such as those occupied by component leg pads or installation holes, positioning holes, etc. A sparse grid greatly affects the pass rate of wiring. Therefore, a reasonably dense grid system should be in place to support wiring.

The distance between standard component legs is 0.1 inches (2.54mm), so the basis of the grid system is generally set to 0.1 inches (2.54 mm) or an integer multiple smaller than 0.1 inches, such as: 0.05 inches, 0.025 inches, 0.02 inches, etc.

6. Design Rule Check (DRC)

After the wiring design is completed, it is necessary to carefully check whether the wiring design meets the rules set by the designer, and also confirm whether the rules set meet the production process requirements of the printed board. Generally, the checks include the following aspects:

(1) Whether the distance between lines, lines and component pads, lines and vias, component pads and vias, and vias and vias is reasonable and meets production requirements. (2) Whether the width of power and ground lines is appropriate, and whether power and ground lines are tightly coupled (low wave impedance)? Is there room in the PCB to widen the ground line? (3) Whether the best measures have been taken for critical signal lines, such as the shortest length, adding protective lines, and clearly separating input and output lines. (4) Whether the analog circuit and digital circuit sections have their own independent ground lines. (5) Whether graphics added to the PCB (such as icons, annotations) will cause signal short circuits. (6) Modifications to some undesirable line shapes. (7) Whether there are process lines added to the PCB? Whether the solder mask meets production process requirements, whether the solder mask size is appropriate, and whether character markings are pressed onto the component pads to avoid affecting assembly quality. (8) Whether the outer frame edge of the power ground layer in multi-layer boards is reduced, as exposed copper foil from the power ground layer can easily cause short circuits.

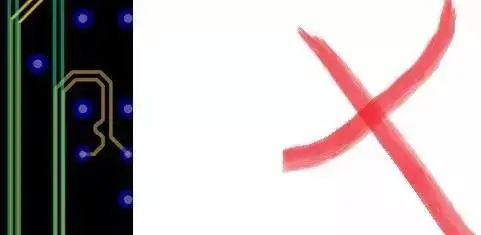

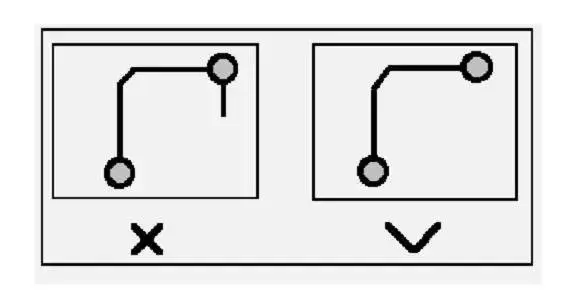

7. Check for sharp angles, impedance discontinuities, etc.

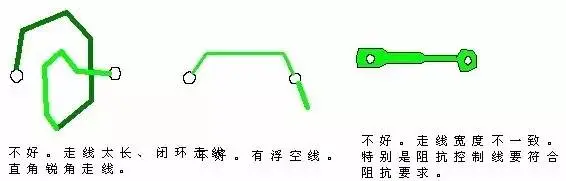

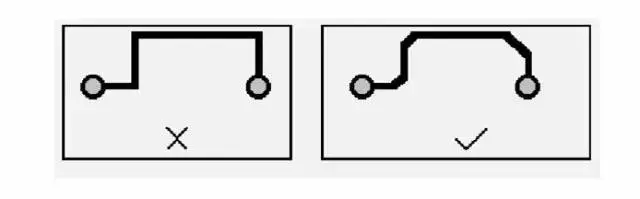

(1) For high-frequency currents, when the bends of the wires present right angles or even sharp angles, the magnetic flux density and electric field strength near the bend are relatively high, which will radiate strong electromagnetic waves, and the inductance at this point will be larger than that of obtuse angles or round angles.

(2) For the bus wiring of digital circuits, the bends should present obtuse angles or round angles, and the area occupied by the wiring should be relatively small. Under the same line spacing conditions, the total width occupied by the line spacing is less than that of right-angle bends by 0.3 times.

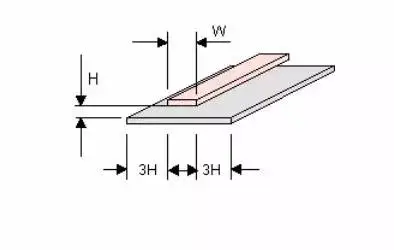

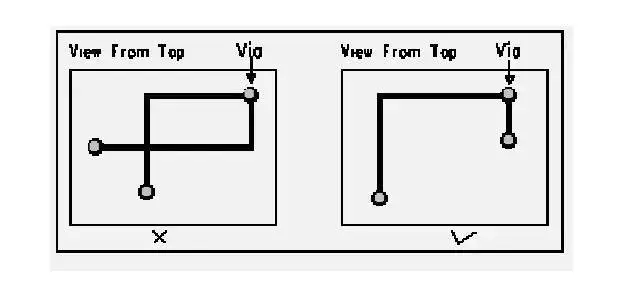

8. Check the 3W and 3H principles

(1) Clock, reset, signals above 100M, and some key bus signals must satisfy the 3W principle; there should be no long parallel traces on the same layer and adjacent layers, and the number of vias on the link should be minimized. (2) The number of vias for high-speed signals is a strict requirement in some component manuals. In terms of interconnection principles, aside from the necessary pin fanout vias, no extra vias should be drilled in the inner layers; they have routed 8G of PCIE 3.0 traces and only drilled 4 vias without issues. (3) The center distance of clock and high-speed signals on the same layer must strictly meet the 3H principle (H is the distance from the routing layer to the return plane); signals on adjacent layers must not overlap, and it is also recommended to meet the 3H principle. Tools are available to check the above crosstalk issues.

RF single board stacking structure

Wiring constraints: Basic requirements

(1) The wiring should be as short as possible, avoid closed loops, and avoid sharp angles and right angles; the width of the lines should be consistent, with no floating lines.

(2) Differential signal lines are generally high-speed signals, and they must meet the symmetry of impedance; differential lines must not cross; the length difference must not exceed 100 mils, and the spacing between differential lines and between a single differential line and ground must meet impedance requirements. The number of vias for differential traces must not exceed 4. The spacing between differential lines must meet the 3W rule.

(3) General oscillators, PLL filter components, analog processing signal processing chips, inductors, and transformers are prohibited from running clock lines, control lines, and electromagnetically sensitive lines underneath.

(4) Analog signals and digital signals, power lines and control signal lines, weak signals and any other signals must not run in parallel; they should be layered (preferably with ground isolation) or run at a considerable distance apart. If adjacent layers must cross, they must not run in parallel. To reduce crosstalk between lines, ensure that the line spacing is sufficiently large; when the center spacing between lines is not less than 3 times the line width, 70% of the electric field will not interfere with each other, referred to as the 3W rule. To achieve 98% of the electric field not interfering with each other, a 10W spacing can be used.

Note: When routing clock lines, be sure to pay attention to effective isolation from data lines and control signal lines; the greater the distance, the better; try not to route on the same layer.

(5) High radiation signal lines (high frequency, high speed, especially clock lines) should not be near interfaces, pull handles, etc., to prevent external radiation.

(6) Sensitive signals (mainly referring to weak signals, reset signals, input signals of comparators, reference power for AD, filter signals of phase-locked loops, and filtering parts of PLL circuits inside chips) should be wired as short as possible, away from strong radiation signals, and not placed at the board’s edge, more than 15mm away from external metal frames. For long-distance wiring, ground wrapping can be used (note that wrapping ground may cause impedance changes), and inner layer wiring is recommended. Additionally, for traces of chips that are weak against ESD, it is recommended to use inner layer wiring to reduce the chance of chip damage.

Wiring constraints: Power

(1) Pay attention to power decoupling and filtering to prevent interference between different units through power lines; power wiring should isolate power lines from other strong interference lines (such as CLK) using ground lines.

(2) The power wiring of small signal amplifiers needs to be isolated with ground copper and grounding vias to avoid EMI interference from entering, thereby degrading the signal quality of the stage.

(3) Different power layers should avoid overlapping in space. This is mainly to reduce interference between different power supplies, especially between power supplies with significant voltage differences; the overlapping of power planes must be avoided, and when it cannot be avoided, a ground layer in between may be considered.

Wiring constraints: Power current capacity

(1) The number of vias for the printed lines of the power section in layer-to-layer transitions must meet the current-carrying requirements (1A/Ф0.3mm via).

(2) The copper foil size of the POWER section of the PCB must meet the maximum current flowing through it and consider a margin (generally referenced as 1A/mm line width).

Wiring constraints: Grounding methods

(1) Grounding lines should be short and straight to reduce distributed inductance and minimize interference caused by common ground impedance.

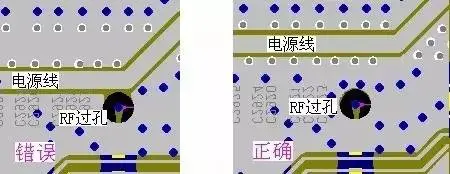

Adjust the direction of the filtering capacitors in each group to minimize the ground loop. As shown in Figure 15, the three filtering capacitors should be grounded towards the relevant RF device direction, especially the high-frequency filtering capacitors.

(2) When grounding devices on the main RF signal path, and when power filtering capacitors need to be grounded, to reduce the grounding inductance of the devices, they should be grounded nearby.

(3) Some components have grounded metal shells at the bottom; it is necessary to add some grounding holes within the projection area of the components, and no signal lines or vias should be routed in the surface layer within the projection area;

(4) When grounding lines need to run a certain distance, they should be widened, and the length of the run should be shortened, avoiding proximity to and exceeding 1/4 of the guided wavelength to prevent antenna effects that lead to signal radiation;

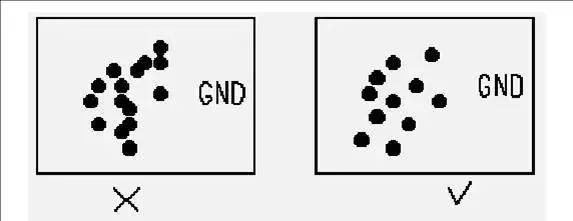

(5) Except for special purposes, there should be no isolated copper areas; grounding vias must be added to copper areas;

(6) For certain sensitive circuits and circuits with strong radiation sources, they should be placed in shielded cavities, and during assembly, the shielded cavity should press against the PCB surface. During PCB design, a “via shielding wall” should be added, which is grounding vias added to the areas closely attached to the walls of the shielding cavity. As shown in the figure, there should be more than two rows of vias, with the two rows staggered, and the spacing between vias in the same row should be about 100 mils.

Wiring constraints: General rules

(1) RF signals should be routed on the top layer of the PCB, and the plane layer beneath RF signals must be a complete ground plane, forming a microstrip structure. To ensure the integrity of the microstrip structure, the following must be done: within the same layer, microstrip lines should be treated with ground copper, and it is recommended that the edge of the ground copper be 3H away from the edge of the microstrip line. H represents the thickness of the dielectric layer. Within the 3H range, no other signal vias should be present. RF signal traces are prohibited from crossing gaps in the second layer of the ground plane. Ground copper should be added between non-coupling microstrip lines, and grounding vias should be added to the ground copper.

The distance from the microstrip line to the shielding wall should be maintained at over 3H. Microstrip lines should not cross the dividing line of the second layer ground plane.

(2) The spacing between ground copper and signal traces must be ≥3H.

The edges of the ground copper should have grounding holes, with a spacing of about 100 mils, arranged uniformly and neatly;

The edges of the ground copper must be smooth and flat, with no sharp burrs;

(5) Except for special purposes, RF signal traces should not extend beyond the excess line ends.

(6) If there are other RF signal lines around RF signal wiring, ground copper should be added between the two for isolation, and a grounding via should be added every 100 mils or so on the ground copper.

(7) If there are other unrelated non-RF signals (such as routing power lines) around RF signal wiring, ground copper should be added between the two, and a grounding via should be added every 100 mils or so.

(8) RF signal vias should be kept away from other wiring in the inner layers. For instance, if a routing power line is close to an RF signal via, EMI interference on the power line can leak into RF wiring, so the correct wiring method should be adopted by adding ground copper and grounding vias between the power line and RF signal via for isolation. Sometimes, if the RF signal line in the inner layer is close to other signals with strong interference (such as routing power lines), the same method should be used to add ground copper and grounding vias for isolation.

(9) When the mounting holes for components are non-metalized holes, RF signal wiring should be kept away from component mounting holes. Ground copper should be added between RF signal wiring and mounting holes, along with grounding vias.

1. Wiring priority

Key signal lines are prioritized: power, analog small signals, high-speed signals, clock signals, and synchronous signals should be wired first.

The density priority principle: start wiring from the components with the most complex connections on the board. Begin wiring from the areas with the densest wiring on the board.

2. Automatic wiring

When the quality of wiring meets design requirements, an automatic wiring tool can be used to improve work efficiency. Before automatic wiring, the following preparations should be completed: the automatic wiring control file (do file) should be defined in detail to better control the wiring quality. These rules can be defined in the software’s graphical interface, but the software provides better control methods, which is to write an automatic wiring control file (do file) based on the design situation, and the software runs under the control of this file.

3. Try to provide dedicated wiring layers for key signals such as clock signals, high-frequency signals, and sensitive signals, and ensure their minimum loop area. If necessary, manual priority wiring, shielding, and increasing safety spacing should be adopted to ensure signal quality.

4. The EMC environment between power layers and ground layers is poor, so sensitive signals should be avoided.

5. Networks with impedance control requirements should be placed on impedance control layers.

Rules that PCB design should follow

(1) Ground loop rules:

The minimum loop rule states that the area of the loop formed by the signal line and its return loop should be as small as possible; the smaller the loop area, the less radiation it emits, and the less external interference it receives. In accordance with this rule, when dividing the ground plane, consider the distribution of the ground plane and important signal traces to prevent issues caused by ground plane slots. In double-layer board design, while leaving enough space for the power supply, the remaining part should be filled with reference ground, and some necessary vias should be added to effectively connect the double-sided ground signals. For some key signals, ground isolation should be used as much as possible, and for designs with higher frequencies, special attention should be paid to the ground plane signal loop issues, and it is recommended to use multi-layer boards.

(2) Crosstalk control:

Crosstalk refers to the mutual interference caused by long parallel wiring between different networks on the PCB, mainly due to the distributed capacitance and inductance between parallel lines. The main measures to overcome crosstalk include:

-

Increase the spacing between parallel wiring, following the 3W rule.

-

Insert grounding isolation lines between parallel lines.

-

Reduce the distance between wiring layers and the ground plane.

3) Shielding protection

Corresponding to the ground loop rules, this is actually to minimize the area of the signal loop, often seen in important signals such as clock signals and synchronous signals; for particularly important signals with particularly high frequencies, consider using a copper shield cable structure design, i.e., isolating the routed line with ground lines on all sides, and also consider how to effectively combine the shield ground with the actual ground plane.

4) Direction control rules for wiring:

That is, the wiring direction of adjacent layers should be orthogonal. Avoid routing different signal lines in the same direction on adjacent layers to reduce unnecessary inter-layer crosstalk; when this situation is difficult to avoid due to board structure limitations (such as some backplanes), especially at higher signal rates, consider using ground planes to isolate each wiring layer and using ground signal lines to isolate each signal line.

5) Open loop check rules for wiring:

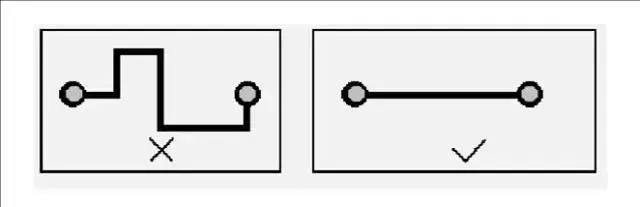

Generally, floating wiring (Dangling Line) at one end is not allowed, mainly to avoid the “antenna effect,” reducing unnecessary interference radiation and reception; otherwise, unpredictable results may arise.

6) Impedance matching check rules:

The wiring width of the same network should remain consistent; changes in line width will cause uneven characteristic impedance of the line, which can lead to reflections at higher transmission speeds. This situation should be avoided as much as possible in design. Under certain conditions, such as the lead wires of connectors, BGA package lead wires, and similar structures, it may be unavoidable to have changes in line width; the effective length of the inconsistent sections should be minimized.

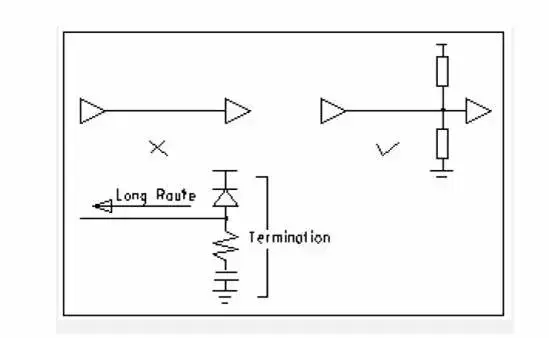

7) Termination network rules for wiring:

In high-speed digital circuits, when the delay time of PCB wiring is greater than 1/4 of the signal rise time (or fall time), the wiring can be regarded as a transmission line. To ensure that the input and output impedances match the impedance of the transmission line correctly, various matching methods can be adopted, and the selected matching method relates to the connection method of the network and the topological structure of the wiring.

A. For point-to-point (one output corresponds to one input) connections, series matching at the start or parallel matching at the end can be chosen. The former structure is simple and low-cost, but has greater delay. The latter matching effect is good, but the structure is complex and the cost is high.

B. For point-to-multipoint (one output corresponds to multiple outputs) connections, when the network topology is a daisy chain, terminal parallel matching should be chosen. When the network is star-shaped, reference can be made to point-to-point structures.

Star and daisy chain are two basic topological structures; other structures can be seen as variations of these basic structures, and some flexible measures can be taken for matching. In practical operations, cost, power consumption, and performance factors should be balanced; generally, complete matching is not pursued; as long as reflections and other interferences due to mismatches are kept within acceptable limits, it is sufficient.

8) Loop closure check rules for wiring:

Prevent signal lines from forming self-loops between different layers. This type of problem is common in multi-layer board designs, and self-loops will cause radiation interference.

9) Length control rules for branches in wiring:

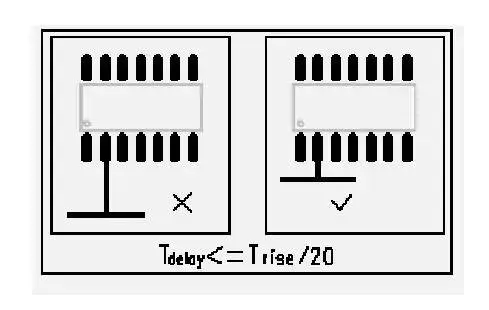

Control the length of branches as much as possible; the general requirement is Tdelay <= Trise/20.

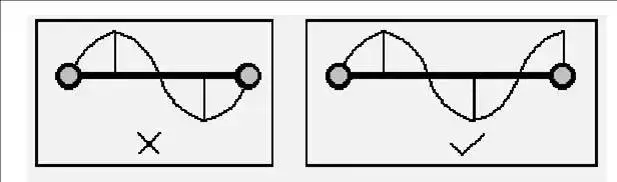

10) Resonance rules for wiring:

This mainly applies to high-frequency signal designs, where the wiring length should not be an integer multiple of its wavelength to avoid resonance.

11) Length control rules for wiring:

That is, the short line rule, which states that the wiring length should be kept as short as possible to reduce interference problems caused by excessive wiring length, especially for important signal lines such as clock lines. It is essential to place the oscillator close to the device. For situations where multiple devices are driven, the specific network topology structure should be determined based on the situation.

12) Chamfering rules:

PCB design should avoid producing sharp angles and right angles to prevent unnecessary radiation, and the process performance is also poor.

13) Component decoupling rules:

A. Add necessary decoupling capacitors on the printed circuit board to filter out interference signals on the power supply and stabilize the power supply signal. In multi-layer boards, the position of decoupling capacitors generally does not have very high requirements, but for double-layer boards, the layout of decoupling capacitors and the wiring method of the power supply will directly affect the stability of the entire system, sometimes even determining the success or failure of the design.

B. In double-layer board design, the current should generally pass through filtering capacitors for filtering before being used by devices, and also fully consider the impact of power noise generated by the devices on downstream devices. Generally, a bus structure design is better, and during design, consider the impact of voltage drop caused by long transmission distances on devices, and if necessary, add some power filtering loops to avoid potential differences.

C. In high-speed circuit designs, the correct use of decoupling capacitors is related to the stability of the entire board.

14) Component layout zoning/layering rules:

A. This is mainly to prevent mutual interference between modules of different operating frequencies while minimizing the wiring length of high-frequency parts. High-frequency parts are usually placed at the interface to reduce wiring length, of course, this layout must also consider potential interference from low-frequency signals. Additionally, consider the segmentation of ground planes for high/low frequency parts, typically using ground segmentation for both, and then connecting them at a single point at the interface.

B. For mixed circuits, analog and digital circuits are often arranged on opposite sides of the printed board, using different layers for wiring, with ground layers isolating them.

15) Control rules for isolated copper areas:

The appearance of isolated copper areas can lead to some unpredictable problems; therefore, connecting isolated copper areas with other signals helps improve signal quality, typically grounding or removing isolated copper areas. In actual production, PCB manufacturers often add copper foil to some empty areas of the board, which is mainly to facilitate PCB processing and also helps prevent PCB warping.

The appearance of isolated copper areas can lead to some unpredictable problems; therefore, connecting isolated copper areas with other signals helps improve signal quality.

Typically, isolated copper areas are grounded or removed. In actual production, PCB manufacturers often add some copper foil to the empty parts of the board, which is mainly to facilitate PCB processing and also helps prevent PCB warping.

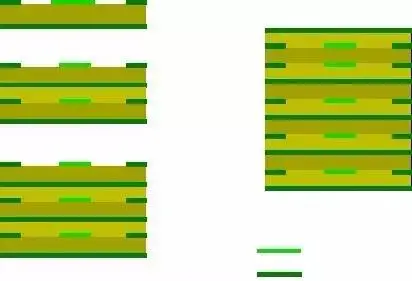

16) Integrity rules for power and ground layers:

In areas with dense vias, care should be taken to avoid vias connecting in the hollow areas of the power and ground layers, which can disrupt the integrity of the plane layers and thereby increase the loop area of signal lines in the ground layer.

17) Overlapping power and ground layer rules:

Different power layers should avoid overlapping in space. This is mainly to reduce interference between different power supplies, especially between power supplies with significant voltage differences; the overlapping of power planes must be avoided, and when it cannot be avoided, a ground layer in between may be considered.

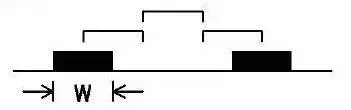

18) 3W rule:

To reduce crosstalk between lines, the spacing between lines should be sufficiently large; when the center spacing between lines is not less than 3 times the line width, 70% of the electric field will not interfere with each other, referred to as the 3W rule. To achieve 98% of the electric field not interfering with each other, a 10W spacing can be used.

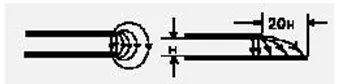

19) 20H rule:

Due to the changing electric field between the power layer and ground layer, electromagnetic interference radiates outward at the edges of the board. This is called the edge effect. The solution is to retract the power layer so that the electric field conducts only within the range of the ground layer. By retracting 20H (H being the thickness of the dielectric between power and ground), 70% of the electric field can be confined within the edges of the ground layer; retracting 100H can confine 98% of the electric field.

20) Five-Five rule:

The rule for selecting the number of layers for printed boards states that if the clock frequency is up to 5MHz or the pulse rise time is less than 5ns, the PCB must use a multi-layer board. This is a general rule; sometimes, due to cost considerations, a double-layer board structure is used. In this case, it is best to make one side of the printed board a complete ground plane layer.