Skip to content

The central controller, as the core component of autonomous driving, acts as the “brain” of the system, typically requiring external connections to multiple cameras, millimeter-wave radars, laser radars, and IMUs, among other devices, to perform functions including image recognition and data processing.

The domain controller, as an intelligent hardware, needs to handle complex AI computations and intelligent control. On the hardware side, it must support AI processing chips that meet the ultra-high computing power requirements for environmental perception and deep learning, CPUs responsible for control decisions and logical operations, and MCUs responsible for functional safety and vehicle control. On the software side, it includes operating systems, middleware, and application layer AI algorithms.

The three key chips on the hardware side are:

The first part is usually a GPU or TPU, which handles the large-scale floating-point parallel computing needs, primarily used for environmental perception and information fusion, including recognition, fusion, and classification of sensor information from cameras, laser radars, etc., such as the GPU unit of Xavier or Ascend 310.

The second part is mostly based on ARM architecture, similar to a CPU, mainly responsible for logical operations and decision control, handling high-precision floating-point serial calculations.

The third part is mainly responsible for reliability and vehicle control, which means functional safety and redundancy monitoring. It doesn’t require very high computing power, but reliability must be guaranteed, with ISO26262 level requirements reaching ASIL-D. Currently, commonly used chips include Infineon’s TC297 or TC397.

On the software side, application layer AI algorithms are generally developed by vehicle manufacturers or OEMs, reflecting the performance and differentiation of vehicles; middleware is generally provided by domain controller developers, similar to ROS, mainly containing some interface drivers and optimizations for the operating system.

Regarding operating systems, Huawei adopts its self-developed HarmonyOS, and the MDC platform supports compatibility with Adaptive AUTOSAR; QNX is currently the best and only choice for automotive-grade systems, but it faces high costs; Linux and Autoware, due to being open-source, have gained the most users, especially Linux, which benefits from a strong engineering background and ecosystem, along with years of application foundation of ROS, making Linux kernel-based operating systems very popular.

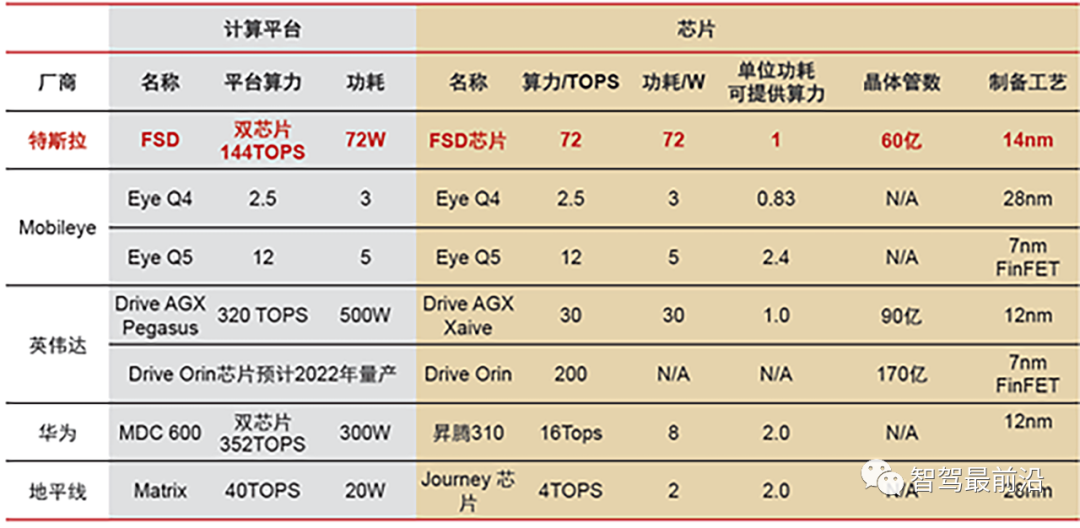

About Autonomous Driving AI Chip Selection

Currently, there are not many AI chips available on the market, especially those that have reached mass production status, with only Tesla, NVIDIA, and Mobileye. Except for Tesla’s self-developed and used chips which are not available externally, other brands can currently obtain test samples through cooperative development.

Taking NVIDIA Xavier as an example, relatively speaking, since NVIDIA Xavier was launched earlier and has a relatively complete ecological layout, it allows developers to quickly build systems and develop AI applications, so many companies design domain controllers based on the Xavier module.

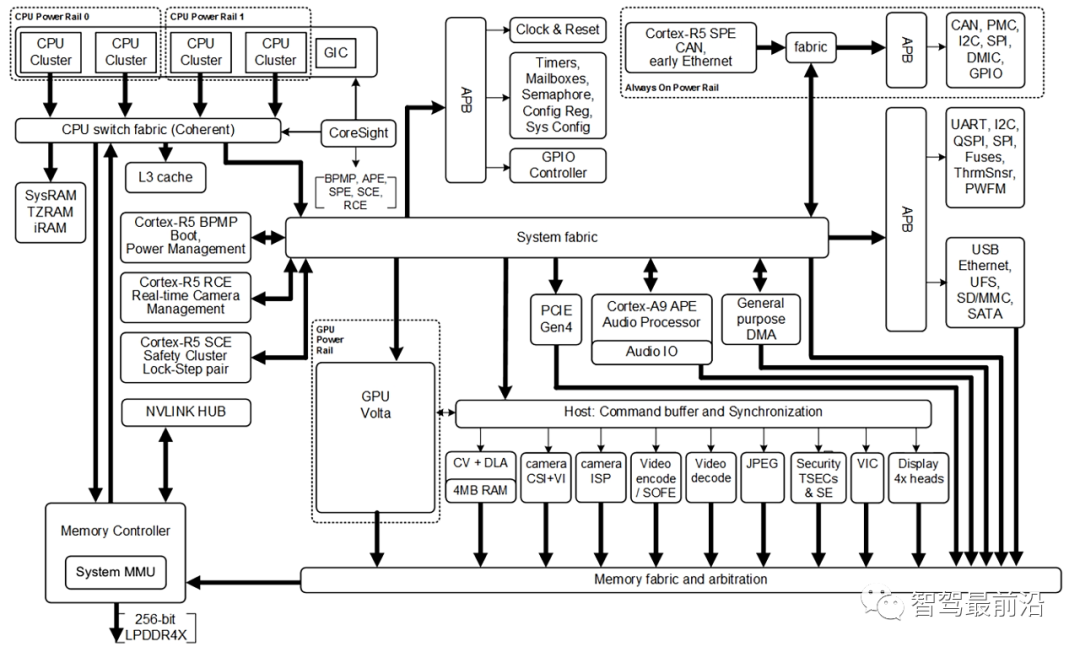

The Xavier SoC can achieve a maximum computing power of 30 TOPs, with Valta TensorCore GPU, an octa-core ARM64 CPU, dual NVDLA deep learning accelerators, image processors, vision processors, and video processors, allowing it to simultaneously and in real-time process dozens of algorithms for sensor data processing, environmental perception, positioning, mapping, and path planning.

The internal structure of the chip is shown in the figure below:

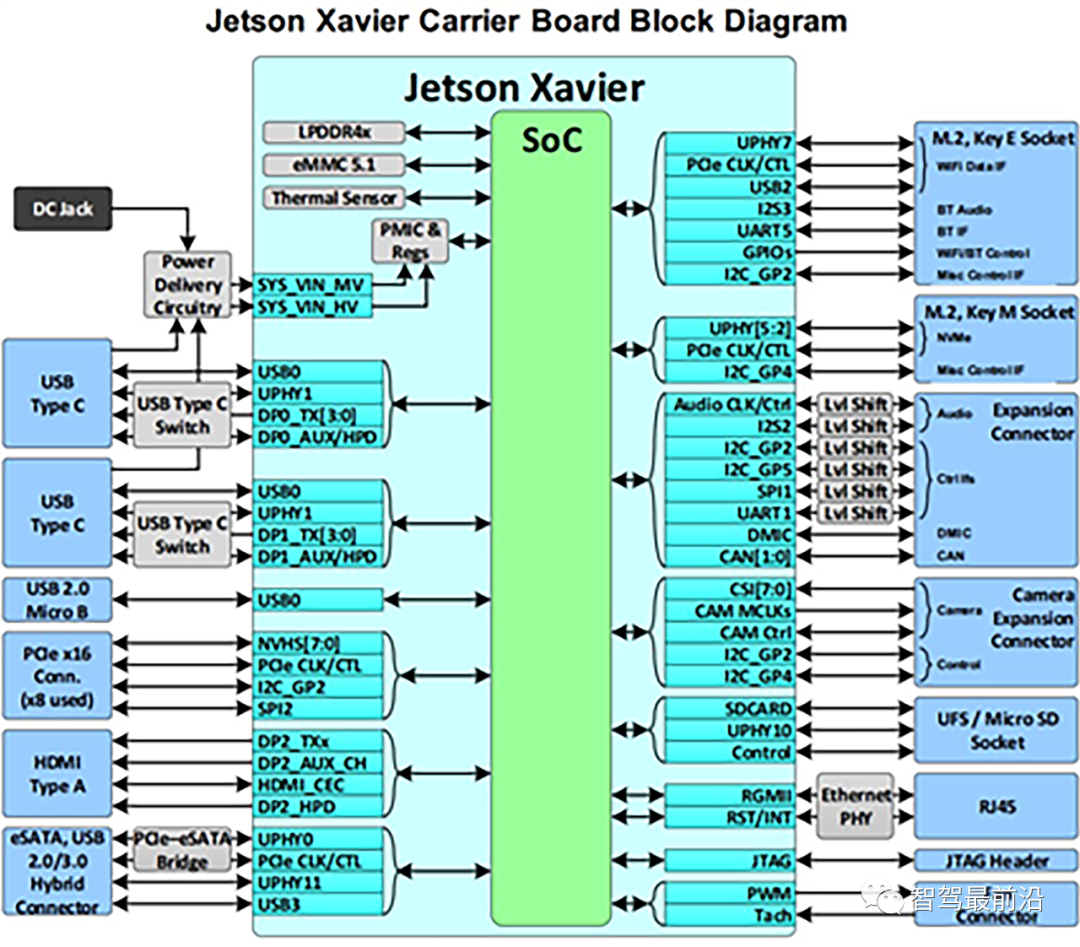

NVIDIA provides the core module of Xavier, and its interfaces are shown in the figure below:

The core is usually the central point. On one hand, it facilitates communication between the autonomous driving controller and peripheral sensors and actuators, while also protecting it. The core emphasizes the operational state, and the term “core-down” refers to issues with CPU calculations; the core emphasizes the core functions of the autonomous driving controller’s overall external functionality.

This is mainly used to measure integer computing capabilities. It includes the number of instruction sets that can be executed per second and the amount of work that can be achieved per second when implementing my test program, which is determined by the architecture of the CPU, memory access speeds, and other hardware characteristics. It is a unit that measures the relative performance of the CPU when running corresponding test programs (in many autonomous driving chip evaluation scenarios, people often use MIPS as the unit of this performance indicator).

The main functions of the memory management unit include: mapping virtual addresses to physical addresses, controlling memory access permissions, and supporting cache.

DataFlash is a large-capacity serial Flash memory product launched by ATMEL, manufactured using NOR technology, and can be used to store data and program code. Compared to parallel Flash memory, it requires fewer pins, is smaller in size, easy to expand, and connects simply with microcontrollers or controllers, working reliably. Therefore, serial Flash controllers similar to DataFlash are increasingly used in autonomous driving controller products and measurement and control system evaluations.

ISP, as the core of visual processing chips, includes functions such as AE (Auto Exposure), AF (Auto Focus), AWB (Auto White Balance), noise reduction, LSC (Lens Shading Correction), BPC (Bad Pixel Correction), and ultimately saves Raw Data to be passed to video codecs or CV. Through ISP, better image effects can be obtained, thus the requirements for ISP in autonomous vehicles are high, such as initially integrating dual-channel or even triple-channel ISPs. Generally, ISP is integrated in the AP (which is a key differentiating factor for many AP chip manufacturers), but with changing demands, independent ISPs have also emerged, mainly due to the need for more flexible configurations and to complement and cooperate with the ISP functions within AP chips.

The realization of autonomous driving relies on environmental perception sensors to collect information about the road environment, transmitting the collected data to the vehicle’s central processor for processing to identify obstacles, drivable roads, etc. Based on the recognition results, it plans paths and sets speeds to automatically control the vehicle’s operation. The entire process must be completed in an instant, with latency controlled to millisecond or even microsecond levels to ensure the safety of autonomous driving. To achieve instantaneous processing, feedback, decision-making, and execution, the computing power of the central processor must be very high.

In autonomous driving, the most computing-intensive task is visual processing, accounting for more than half of the total computing power demand, and for each increase in autonomous driving level, the computing power requirement increases at least tenfold. Level 2 requires 2 TOPS of computing power, Level 3 requires 24 TOPS, Level 4 requires 320 TOPS, and Level 5 requires over 4000 TOPS.

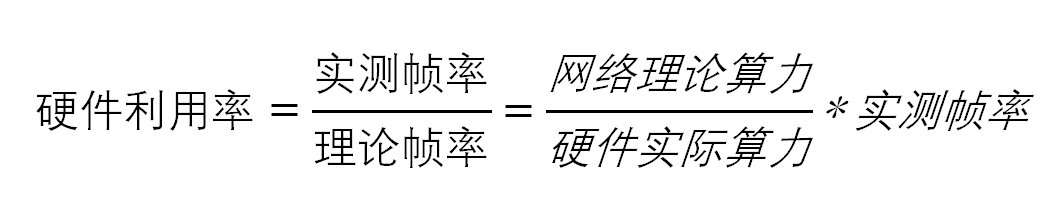

Having computing power alone is not enough. Considering the complexity of automotive applications, automotive processors also need to consider computing power utilization, whether they meet automotive regulations and safety standards, etc. The theoretical computing power depends on the precision of calculations, the number of MACs, and the operating frequency.

Theoretical computing power is derived from the multiplication operations accumulated in the Net convolution layer, with each multiply-accumulate (MAC) in the convolution layer counting as two OPS. Convolution operations account for over 90% of DL NET, while other auxiliary operations or operations from other layers are negligible. The total number of multiplication operations in all convolution layers of SSD is 40G MACs, so the theoretical computing power is 80GOPS.

The difference between real and theoretical values is significant. Considering other operation layers, the actual hardware utilization rate should be higher. The main factors determining the actual computing power are memory (SRAM and DRAM) bandwidth, actual operating frequency (i.e., supply voltage or temperature), and the batch size of the algorithm.

In the highest performance mode, if the power consumption level of the autonomous driving controller’s chip is high, even if its performance is strong, it can lead to unpredictable hazards, such as a significant increase in heat generation and power consumption. These results are undoubtedly a “nuclear bomb” for new energy vehicles. Therefore, we need to fully consider its power consumption indicators during the initial design of autonomous driving chips.

GPUs are designed for large throughput to handle large-scale parallel computing. The control unit of a GPU can merge multiple accesses into fewer accesses. GPUs use more transistors for execution units rather than for complex data caches and instruction control like CPUs. Due to the GPUs’ powerful floating-point computing capabilities, they are increasingly used in image or video processing applications at the front end of smart vehicles and are also mainstream in high-performance computing designs of central controllers.

9) Rich IO Interface Resources

The main control processor for autonomous driving needs a rich set of interfaces to connect various sensor devices. Currently, common autonomous driving sensors in the industry include: cameras, laser radars, millimeter-wave radars, ultrasonic radars, combined navigation, IMUs, and V2X modules, etc.

-

The interface types for cameras mainly include: MIPI CSI-2, LVDS, FPD Link, etc.

-

Laser radars are generally connected via standard Ethernet interfaces.

-

Millimeter-wave radars transmit data via CAN bus.

-

Ultrasonic radars are generally connected via LIN bus.

-

Combined navigation and inertial IMUs commonly use RS232 interfaces.

-

V2X modules also generally use Ethernet interfaces for data transmission.

In addition to the IO interfaces required for the above sensors, other common high-speed and low-speed interfaces are also needed, such as: PCIe, USB, I2C, SPI, RS232, etc.

As a local bus for CPUs, its biggest feature is high data transmission throughput and low latency.

The functional safety goal is the core design requirement of the entire autonomous driving central controller. Since it affects the single point failure analysis results in the overall design of the autonomous driving function, it must be fully considered during the early hardware design to ensure it can completely meet the system’s functional safety design requirements for hardware.

Remote upgrades allow users to fix software faults, significantly shortening the time for intermediate steps, enabling software to reach users quickly, while also adding new functions to vehicles, broadening the scope of “services” and “operations.” Therefore, whether the central controller chip supports OTA is essential for reducing costs for automotive manufacturers and users, including recall costs for manufacturers and time costs for users, enhancing user novelty, and increasing the added value of vehicles.

The size of the controller packaging, pin definitions, etc., affect the overall installation form of the driving controller and also influence the distribution of connections to peripheral components. Additionally, whether the interface is waterproof affects the installation environment of the controller, allowing for more freedom. However, current domain control interfaces are not waterproof.

The temperature control range of the controller includes its storage and operating environmental temperatures. If the actual vehicle confirms that the storage and operating environmental temperature in the previous millimeter-wave controller assembly area exceeds this value, adjustments need to be made to raise the range while meeting OEM requirements. Suppliers must ensure that no recalls occur due to hardware design flaws. Especially when computing power reaches above 100 and power consumption exceeds 60W, the rise in temperature may require active cooling to ensure heat can be dissipated in a timely manner, not affecting the normal operation of the controller. Active cooling generally includes: fan cooling and water cooling.

15) Automotive Regulations and Functional Safety

Compared to consumer electronics, automotive chips have the highest requirements for safety and reliability.

Automotive chips work for years in extreme environments of “-40℃ to 125℃” with severe vibrations. To ensure that automotive electronic products meet high standard quality requirements for operating temperature, reliability, and product lifespan, the Automotive Electronics Council (AEC) has established relevant quality certification standards, among which AEC-Q100 is the certification standard for pressure testing of automotive integrated circuits. The AEC-Q100 standard has become an industrial de facto standard for automotive electronic products in terms of reliability and product lifespan after years of development.

In addition to meeting automotive-grade requirements, autonomous driving chips must also meet the certification requirements defined by the ISO 26262 standard for “Functional Safety” (Fusa). Functional safety design requirements for chips aim to identify and correct chip failures as much as possible (divided into: system failures and random failures). System failures are essentially design flaws, primarily relying on design and implementation process specifications to ensure, while random failures depend more on special failure detection mechanisms in chip design to ensure.

ISO 26262 categorizes safety levels, commonly ASIL-B and ASIL-D. ASIL-B requires chips to cover 90% of single-point failure scenarios, while ASIL-D requires coverage of 99%. The larger the chip area and the more transistors, the higher the corresponding failure rate.

Whether the controller supports integrated control methods of MCU+MPU or only supports single-chip control forms.

17) Supply Chain Assurance

High market demand has led to a shortage of semiconductor supply chains and production capacity, with various “natural and man-made disasters” disrupting the normal production rhythm of semiconductors. The contradiction between demand and production capacity is difficult to resolve in the short term.

In the context of a tight global chip supply chain, supply chain assurance is also very challenging for domain controller suppliers. When selecting domain controller suppliers, the supply capabilities of their partner chip manufacturers are also an important consideration indicator.

In 2023, the chip shortage continues to impact the automotive industry, with some manufacturers starting to think of new semiconductor supply strategies, some even bypassing Tier 1 to directly approach chip design manufacturers. Deeper OEMs have begun to participate in the chip design and development process. For example, several automakers have established strategic partnerships with autonomous driving AI chip manufacturers like Horizon Robotics and Black Sesame. Some have even directly entered the semiconductor supply chain, bringing chip design into the OEMs, a model referred to as “OEM-Foundry-Direct,” represented by companies like Tesla and BYD.

Choosing what kind of main control chip to use depends first on the market positioning of the domain controller: what functions it intends to achieve and what price range it will be configured for.

If the target positioning is to develop an L1~L2 level product for assisted driving, and it is aimed at mass production, then cost sensitivity is high when selecting chips. Such domain control products can be based on mid-range to low-end chips.

If the target positioning is to create an L4 level unmanned driving under limited scenarios, then customers may be more inclined to create a customized product. For example, if the aim is to develop a Robotaxi operating model, the goal is to refine the algorithm first. The volume will not be particularly large, so cost sensitivity when selecting chips is relatively lower, but the performance must be good and stable enough.

Liu Wei, deputy general manager of Neusoft Ruichi, mentioned: “From the perspective of cooperation with chip companies, we look at whether they are mainstream chip manufacturers and whether they have a continuous product roadmap. For example, some chip manufacturers may develop a good chip, but do not have subsequent updates. Therefore, building a domain controller around that chip will face significant issues with future product iterations and upgrades.”

Similarly, Li Maoqing, the head of intelligent driving system design at Joyson Electronics, also mentioned the same viewpoint: “In the hardware solution selection of domain controller system design, in addition to focusing on the functional performance of the chip itself, it is also necessary to fully understand the product roadmap of the chip company, whether there is a flexible family of chip series, and whether subsequent chips can be PIN to PIN upgraded on the hardware platform, thus improving hardware performance while reducing development costs?”

20) Chip Ecosystem (Toolchain)

Whether the entire software toolchain of the chip or the development of some algorithms can meet customer needs. In other words, the ecosystem of the chip, whether it has a good ecosystem to support customers in practical development, is also one of the important considerations for OEMs or Tier 1 when choosing chips.

NVIDIA’s chip ecosystem is relatively advanced in the industry, encompassing developers, available application software, and rich tools and libraries:

-

It can provide abundant software algorithm talent for the automotive field;

-

A large number of algorithm models and related application software have been trained in the general AI field;

-

A unified hardware and underlying software interface architecture (CUDA-X) that can be easily ported to the automotive field;

-

Due to a large number of users, partners have contributed a wealth of libraries and tools to the CUDA platform.

The hardware R&D director of Zhixing Technology explained: “Currently, many OEMs are using NVIDIA’s Orin chip, not only because it is a high-performance computing platform, but also because it provides the entire software toolchain, even some low-level code and algorithm code can be provided; developers can adapt more on it, enabling better development of a practical high-level autonomous driving computing platform. Choosing a chip is not just about the chip itself, but more about choosing an ecosystem.”

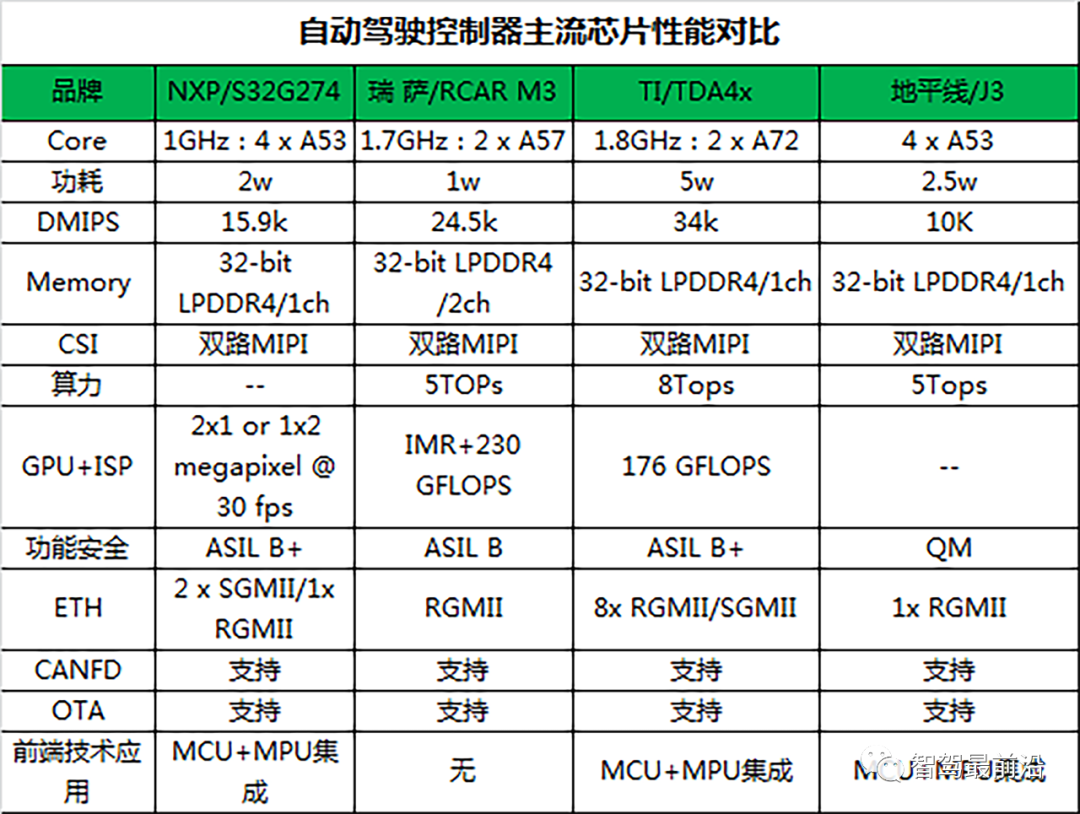

Based on the above important factors in the selection process of autonomous driving domain controllers, we conducted a statistical analysis of the mainstream controller chips in the market and obtained the following comparative analysis results.

Recently, due to work needs, I organized the key parameters of domain controllers for chip selection use.

Welcome all angel round enterprises in the entire automotive industry chain (including the power battery industry chain) to join the group,Around enterprises (to be recommended to 800 automotive investment institutions at top-tier agencies);There are communication groups for leaders of sci-tech innovation companies, and dozens of groups related to the automotive industry, including complete vehicles, automotive semiconductors, key components, new energy vehicles, intelligent connected vehicles, aftermarket, automotive investment, autonomous driving, and vehicle networking. Please scan the administrator’s WeChat to join the group (please indicate your company name).