Everyone knows that Altera’s FPGA can be configured using the EPCS flash memory configuration chip, and there are two methods to program the EPCS chip. One method is to directly program the POF file through the AS port, which requires a separate 10-pin socket in the circuit design. The other method is to use the JTAG port for programming, but it requires the configuration file (*.sof) to be converted into a JIC file in advance.

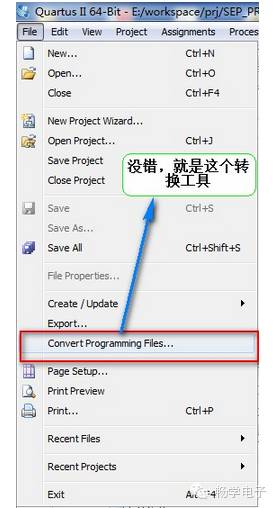

The method for converting to a JIC file is to generate the SOF file after a full compilation of the project, and then use the conversion tool found in the QII file menu, as shown in Figure 1.

Figure 1: Configuration File Conversion Tool

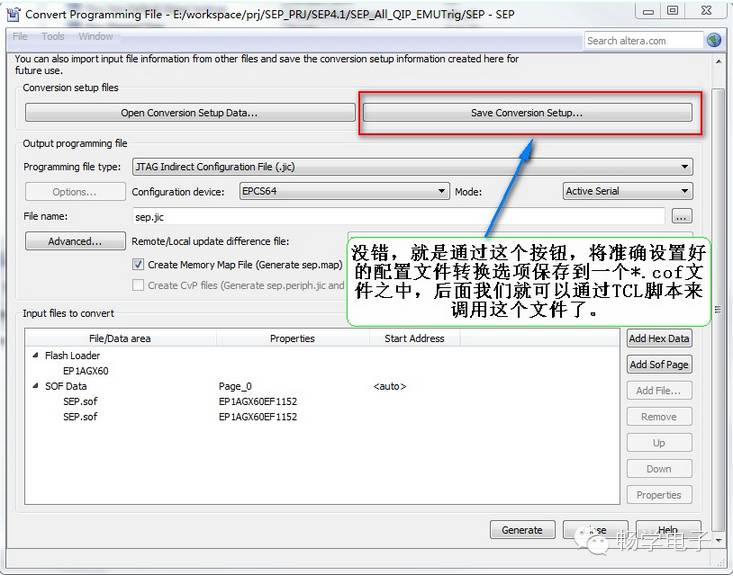

Today, I will introduce a method to automatically generate JIC files during the compilation process using a script in Quartus II. The prerequisite is that the designer must confirm a correct conversion setting (different designs may have different settings), and then save this setting to a *.cof file (named jicgen.cof here), as shown in Figure 2.

Figure 2: Accurately Set Configuration File Conversion Options and Save to COF File

Next, write a simple TCL script file, which contains just one line: “exec quartus_cpf -c jicgen.cof”.

The final step is to add the line “set_global_assignment -name POST_FLOW_SCRIPT_FILE ‘quartus_sh:JicGen.tcl'” in the project’s configuration file (*.qsf). This way, after the compilation is complete, the required JIC file will be automatically generated for us.