Welcome to leave a message, each message will be selected, and I will reply on the same day. Any errors in the article will also be updated in the reply.

#FPGA #SerialTransmission #BaudRateGeneration #TimingLogic

This article continues to detail the serial transmission module.

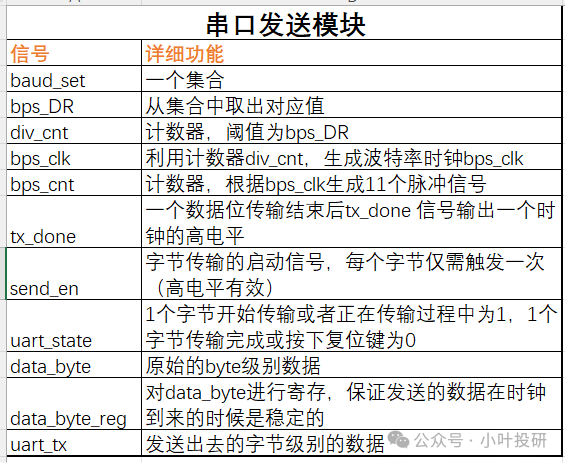

In the serial transmission module, baud_set selects the baud rate level, and bps_DR takes this value as the div_cnt counting threshold. Once the threshold is reached, bps_clk is generated to control the transmission rhythm. bps_cnt counts the bps_clk pulses (a total of 11), controlling the transmission process. send_en triggers byte transmission at a high level, uart_state indicates the transmission status (1 for ongoing), and tx_done goes high when one bit is transmitted. data_byte is the raw data, which is stabilized by data_byte_reg and sent bit by bit by uart_tx, ensuring accurate data output.

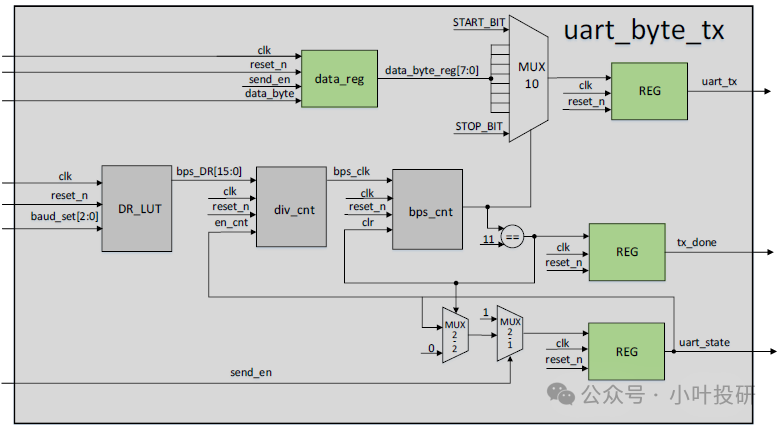

1. Structure Diagram of Serial Transmission

The serial transmission function is divided into several submodules, where the green boxes represent individual structural registers to achieve stable data input and output.

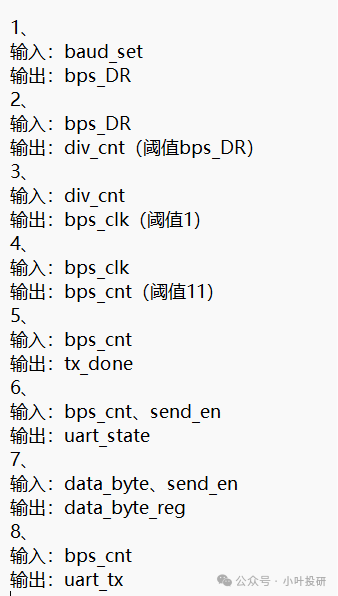

2. The serial transmission module can be divided into the 8 steps shown in the figure below

3. Detailed introduction of each signal

3. Detailed introduction of each signal