Hello everyone, today I want to talk about a very common communication protocol in embedded development—the SPI protocol.

However, we will not discuss its basic principles today, but rather explore a detail that many people may not have noticed: the 4-wire and 7-wire versions of the SPI protocol.

You might wonder, isn’t SPI just that common 4-wire connection? Why is there a distinction between 4-wire and 7-wire? Don’t worry, keep reading, and I will unveil this mystery for you.

Standard SPI Protocol

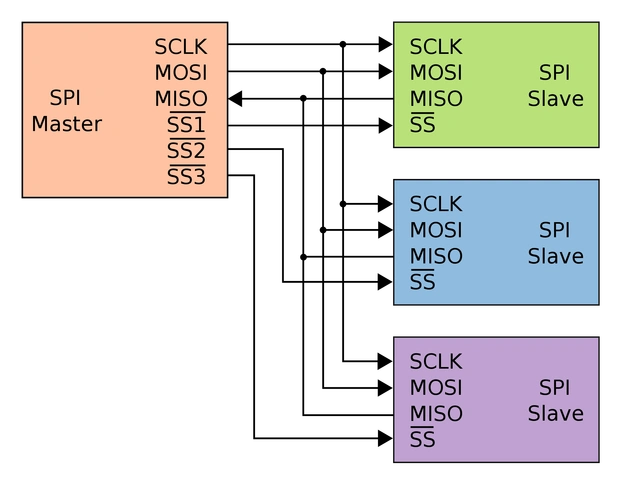

In a 4-wire SPI, the driver typically configures four main signal lines:

- MOSI (Master Out Slave In): The master writes data to the slave device.

- MISO (Master In Slave Out): The slave writes data to the master.

- SCLK (Serial Clock): The master generates the clock signal to control the data transmission rate.

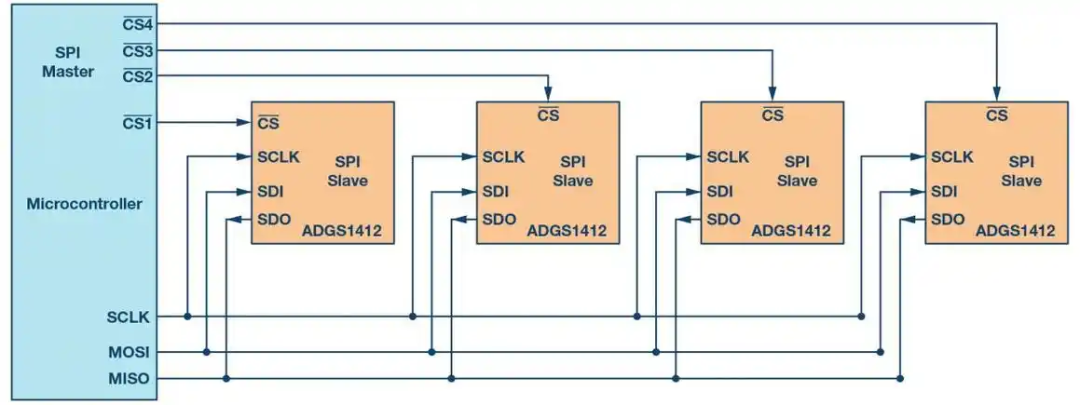

- CS (Chip Select): The master selects the slave device for communication.

Characteristics of the SPI Protocol include:

Full-Duplex Communication: The master sends data to the slave via the MOSI line while receiving data through the MISO line. Even if the slave does not send data, the MISO line may still produce noise or invalid data, but the master will read this data on the clock edge.

Point-to-Point Connection: Each slave device has an independent chip select line, allowing the master to select which slave to communicate with, thus supporting point-to-point connections.

Synchronous Transmission: Data transmission occurs under the control of the clock signal generated by the master, which synchronizes the data transmission rate between the master and the slave.

Low Overhead: The SPI bus requires only four lines, which is lower in hardware overhead compared to other serial communication protocols like I2C and UART.

The SPI protocol is widely used in many embedded systems and digital systems due to its simplicity and efficiency, making it one of the common interfaces for connecting peripheral devices.

What is 7-Wire SPI?

If you are still with me, you might be wondering: “Isn’t 4 wires enough? Why add 3 more wires?”

In fact, 7-wire SPI is not needed in all situations; it is only used in more complex application scenarios. So what are these additional 3 wires?

-

SDO (Slave Data Out): SDO is the data output channel from the slave device. In certain special cases, both SDO and MISO can exist simultaneously to achieve more efficient bidirectional data transmission. In simple terms, if your SPI communication needs to send and receive data simultaneously in both directions, SDO comes into play.

-

SDI (Slave Data In): Opposite to SDO, SDI is the data input channel for the slave device. It is similar to MOSI but is typically used as an independent input signal line to support more complex communication.

-

IRQ (Interrupt Request): IRQ is an interrupt request signal, usually used for the slave device to actively notify the master of certain events. For example, when data is ready or the device needs the master to handle certain states. This signal line is very useful in applications requiring real-time responses, allowing the master to respond quickly without constantly polling for data, saving a lot of time and computational resources.

Of course, these three pins may have different names on different platforms, but their functions are the same.

Advantages of 7-Wire SPI

After introducing the 7-wire SPI protocol, what advantages does it offer? Why add 3 more lines? In fact, the addition of these signal lines is to provide more control capabilities and higher performance, especially in the following aspects:

Increased Data Transmission Rate: 7-wire SPI avoids data conflicts and blocking through independent input and output signals. Especially with the introduction of SDO and SDI, bidirectional data transmission can occur simultaneously, enhancing overall data throughput.

Improved Response Speed with Interrupt Notifications: The addition of the IRQ signal line allows the slave to promptly notify the master of important events, avoiding the need for the master to continuously query the status of peripherals, thus saving computational resources and wait time. This results in faster system response times.

Stronger Device Control Capabilities: The 7-wire SPI protocol, by adding extra signal lines, allows the master to have more detailed control over peripherals, such as real-time status retrieval or more flexible management of the data transmission process. This can bring higher stability and scalability in complex embedded applications.

7-Wire SPI Transmission Process

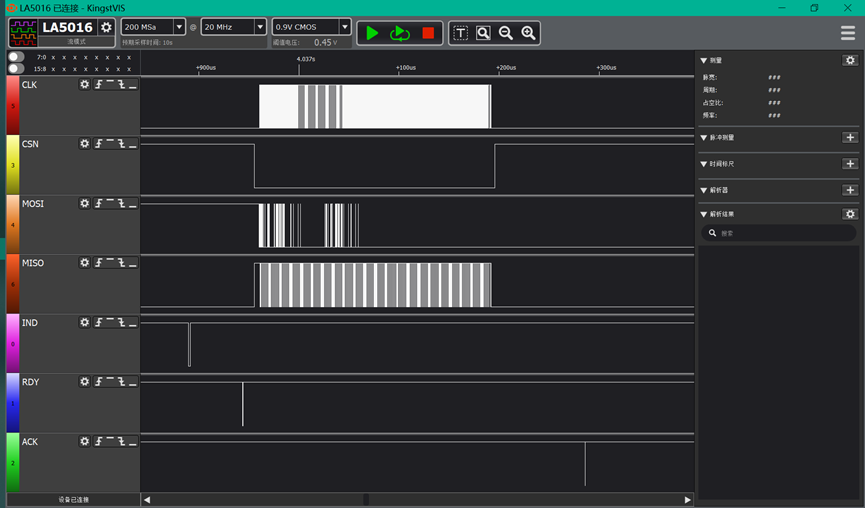

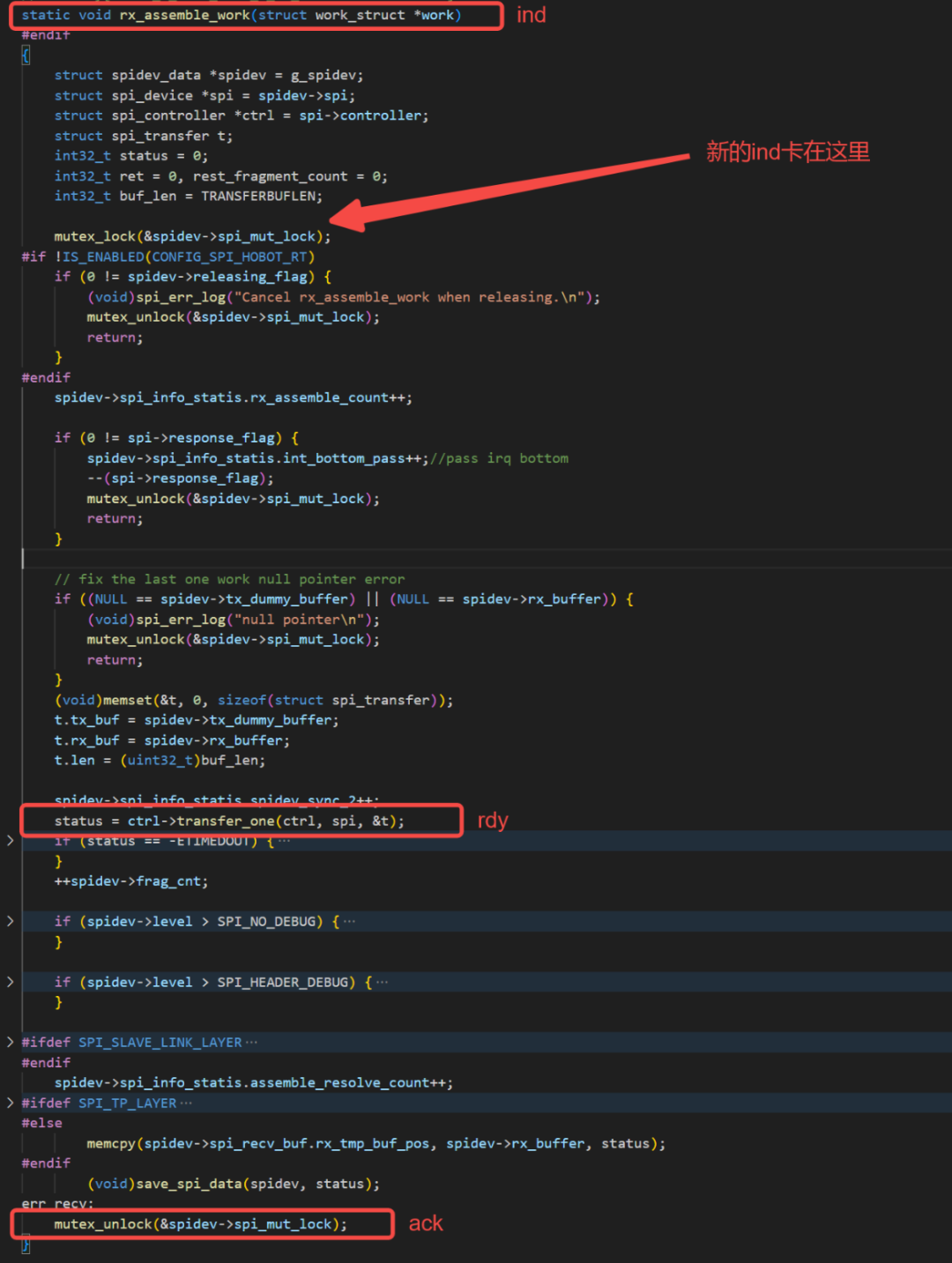

Here, I will briefly introduce the implementation idea of the 7-wire SPI protocol driver used in my current project. The three signal lines in my project are named IND, ACK, and RDY, and their usage logic is as follows:

Master Sends Message to Slave:

Step 1: The master pulls the IND line, which is an interrupt for the slave, indicating that the master is telling the slave to prepare for data transmission.

Step 2: If the slave is ready, it will pull the RDY (ready) GPIO line, which serves as an interrupt signal for the master, notifying the master that the slave is ready to receive messages.

Step 3: If the master detects the interrupt on the RDY line, it needs to provide the clock and CS signals. If the master does not provide the clock and CS within 2 seconds, the slave will trigger a timeout.

Step 4: If the master provides the clock and CS, data transmission can begin. No need for further explanation; this part follows the standard SPI protocol and requires no additional analysis.

Step 5: After the slave successfully receives the data sent by the master and caches it in the buffer, it will send an ACK signal to the master to notify that it has successfully received the data.

The above is the complete process of a single SPI message. Of course, in the 7-wire SPI protocol, many additional logics will be added to ensure high-speed and stable transmission. Now let’s look at the process of the slave sending messages to the master.

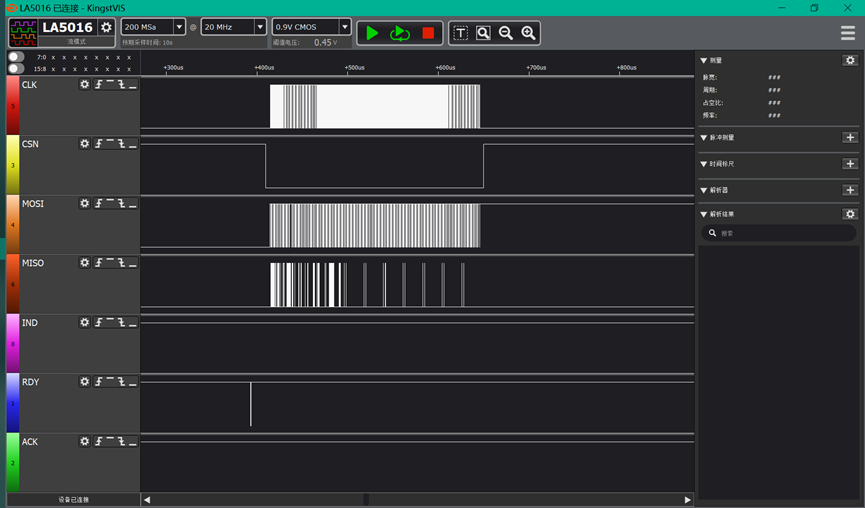

Slave Sends Message to Master:

Step 1: The slave triggers a RDY signal, telling the master, “I am about to start sending data, please provide CS and clock quickly. If you do not provide them within 2 seconds, I will timeout.”

Step 2: After receiving the RDY signal, the master starts providing CS and clock signals. If the master does not provide CS and clock, the slave will print a timeout message.

Step 3: The slave begins to send data according to the standard SPI protocol.

The process of the slave sending messages to the master is relatively simple, so I will not analyze it further. Now let’s briefly analyze how the master sends messages to the slave and how the slave’s driver code should be implemented.

7-Wire SPI Protocol Slave Driver

To implement a 7-wire SPI driver, we first need to configure 3 GPIOs in the device tree, namely IND, ACK, and RDY, where IND is set as an interrupt to notify the slave when the master starts SPI transmission.

Register the interrupt service function for the IND pin, and in this interrupt service function, the following tasks need to be completed:

- Allocate a buffer to store data;

- Check if the device status is normal;

- Check if data is currently being transmitted; if so, wait or exit (receive frame by frame);

- Set the RDY pin to notify the master of its status;

- Call the receive interface in the standard SPI driver to start data transmission;

- After transmission is complete, process the data, such as serialization, storing it in a linked list, etc.;

- After transmission is complete and verification is successful, set the ACK pin to indicate that the data has been correctly received.

Of course, when designing the SPI driver, there are more considerations, such as handling abnormal data, retransmission, and other logics.

Additionally, consider using memory pools or DMA buffer management to ensure efficient resource utilization. If high-frequency transmission is involved, avoid frequent memory allocation and deallocation.

Confirm the order of data reception and transmission to avoid data confusion or loss during processing. You may also add data verification mechanisms (such as CRC checks or checksums) to ensure the integrity and correctness of the transmitted data upon reception.

Depending on the actual application scenario, consider how to handle data after transmission is complete. If the data requires further processing, such as deserialization or batch transmission, it is best to design an efficient processing method in advance.

Finally, ensure that the operations of the RDY and ACK pins are synchronized with the master device to avoid race conditions. You may need to consider locking or queuing management for these signals to prevent conflicts caused by simultaneous modifications.

Conclusion

From the perspective of driver analysis, there are significant differences in implementation and usage between the 4-wire and 7-wire versions of the SPI protocol. The 4-wire SPI is suitable for simple, low-speed data exchanges, with a relatively simple driver implementation; while the 7-wire SPI introduces more signal lines, supports interrupt notifications, and has a more complex driver implementation, suitable for efficient, real-time communication needs.

In summary, when developing complex embedded systems, the choice between 4-wire and 7-wire SPI should be based on specific performance requirements and hardware resources.

END

Author:JamesBin

Source:Embedded Yu Xiang GardenCopyright belongs to the original author. If there is any infringement, please contact for deletion..▍Recommended ReadingSupply Cut! Huawei No Longer Has Windows AvailableThe company received a lawyer’s letter for using pirated AD software…A Step-by-Step Guide to Writing Embedded Driver Programs (Based on Timing Diagrams)→ Follow for More Updates ←