Skip to content

Recently, the eMMC of the product encountered some issues. In response to these issues, I read the relevant sections of the Embedded Multi-Media Card (eMMC) Electrical Standard (5.1) JESD84-B51 and recorded the eMMC boot process as follows.

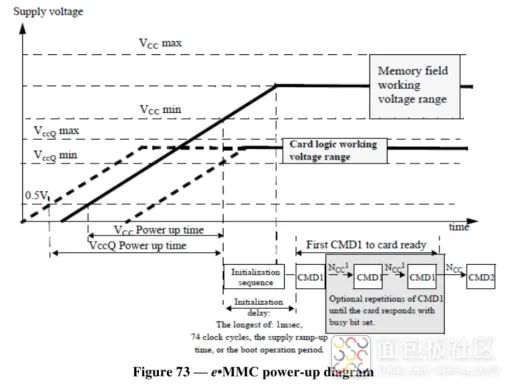

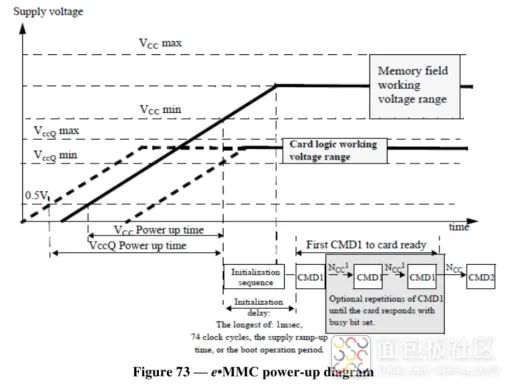

The above figure shows the eMMC power-on process, with the following steps:

1. Power on VCC and VCCQ, with no timing requirements;

2. After power on, eMMC enters the pre-idle state, and the power-on time for each supply voltage must be within the specified range (tPRU);

3. If the eMMC does not support boot mode, or if the BOOT_PARTITION_ENABLE bit is cleared, it enters the idle state. In this state, it only responds to the CMD1 command. If it is version 4.2 or earlier, it directly enters the idle state after power on;

4. If the BOOT_PARTITION_ENABLE bit is set, eMMC enters the pre-boot state and then waits for the boot initialization process. After the boot operation, eMMC enters the idle state. During the pre-boot period, if eMMC receives any command other than the boot initialization sequence and CMD1, it enters the idle state. If eMMC receives the boot initialization sequence, it begins the boot operation. If boot ack is enabled, eMMC sends 010 to the host within the specified time. After the boot operation is completed, eMMC enters the idle state and prepares for CMD1 operation. If eMMC receives the CMD1 command during the pre-boot phase, it starts to respond to the command and enters the card identification state;

5. In the idle state, eMMC only responds to CMD1 commands;

6. CMD1 is a specific synchronization command that can be used to negotiate the voltage range and poll the device status until power on is complete. Devices that have not completed power on will return a busy flag in response to CMD1, indicating that the device is still in the power-on process and cannot be identified yet. The device must complete the initialization process within 1 second of receiving the first CMD1, and its level must be within the valid OCR range. If the eMMC device was previously set with EXT_CSD byte【155】 bit0 PARTITION_SETTING_COMPLETED, the initial delay will no longer be 1 second, but will be calculated by EXT_CSD byte【241】 INI_TIMEOUT_PA. This timeout period is only used for the first boot after setting; for all subsequent initializations, the 1-second timeout is still used.

7. After power on is complete, the host begins to send CLK and CMD;

8. Each bus master must execute CMD1;