According to reports from Electronic Enthusiasts (by Huang Jingjing),IDC predicts that the shipment of AI PCs will grow from the current approximately 50 million units to over 167 million units by 2027. At that time, AI PCs will account for about 60% of the total global PC shipments.With more AI PC processors supporting DDR5, DDR5 memory will penetrate and become more widespread. Compared to DDR4, where all voltages are supplied by the motherboard, DDR5 memory modules are equipped with PMICs.PMICs are key to achieving efficient power delivery, providing breakthrough performance for advanced computing applications.Recently, Rambuslaunched a complete client chipset for the next generation ofAI PCmemory modules, which includes two new power management chips (PMICs) for client computing.Mr. John Eble, Vice President of Product Marketing for Rambus Memory Interface Chips,and Mr. Su Lei, General Manager of Rambus Greater China,were interviewed by the media to share the latest PMIC products and memory chipset solutions.

Features of PMIC5200 and PMIC5120

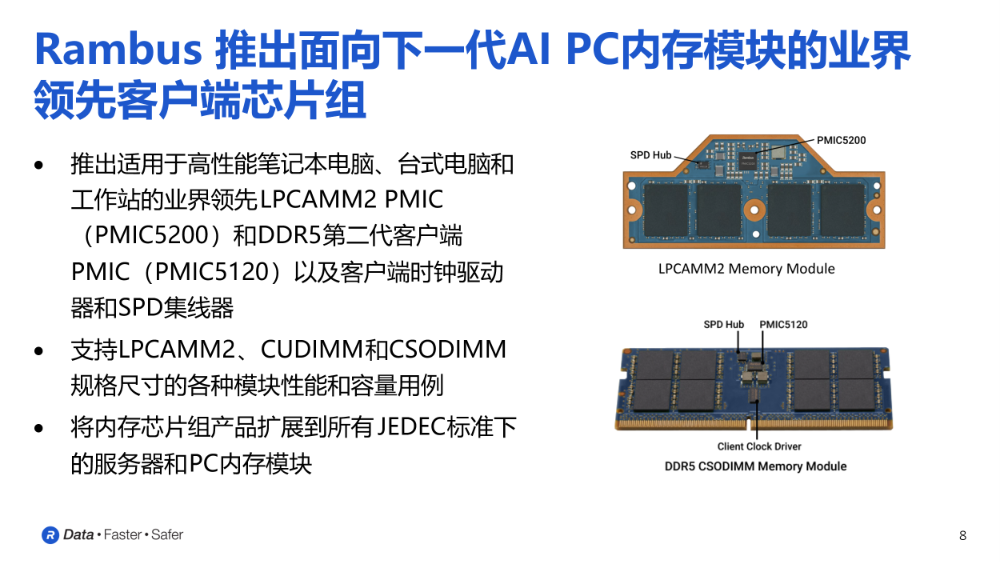

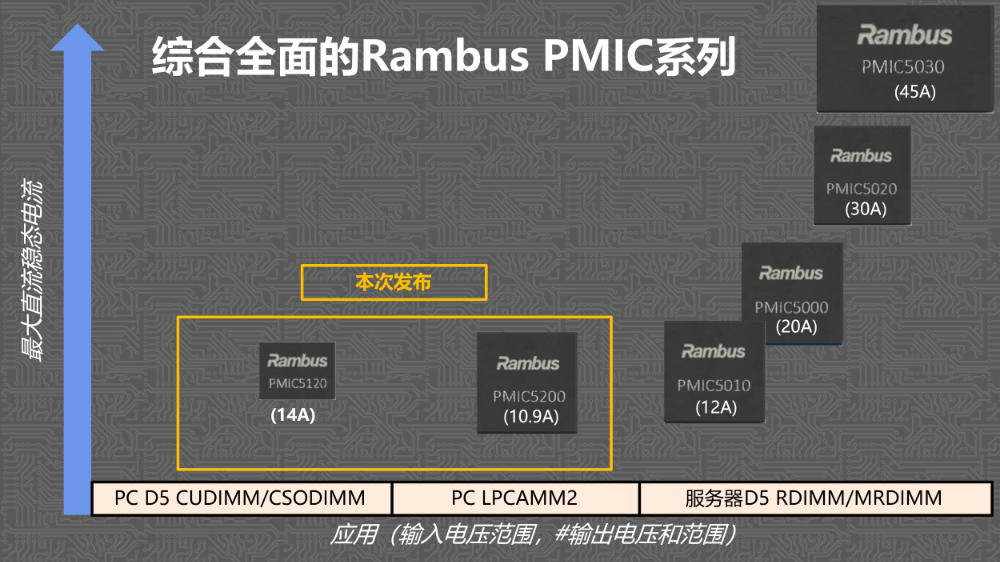

The two new Rambus PMICs are PMIC5200, suitable for LPDDR5 CAMM2 (LPCAMM2) memory modules, and PMIC5120, suitable for DDR5 CSODIMM and CUDIMM.PMIC5200 is a dedicated power management chip that supports LPDDR memory on the recently released LPCAMM2 memory modules; the introduction of LPCAMM2 modules brings the much-needed flexibility for LPDDR memory in laptops. PMIC5120 is the second-generation DDR5 client PMIC, featuring stronger current supply capabilities and optimized functional characteristics, designed for CSODIMM and CUDIMM modules, and widely used in laptops, desktops, and workstations.

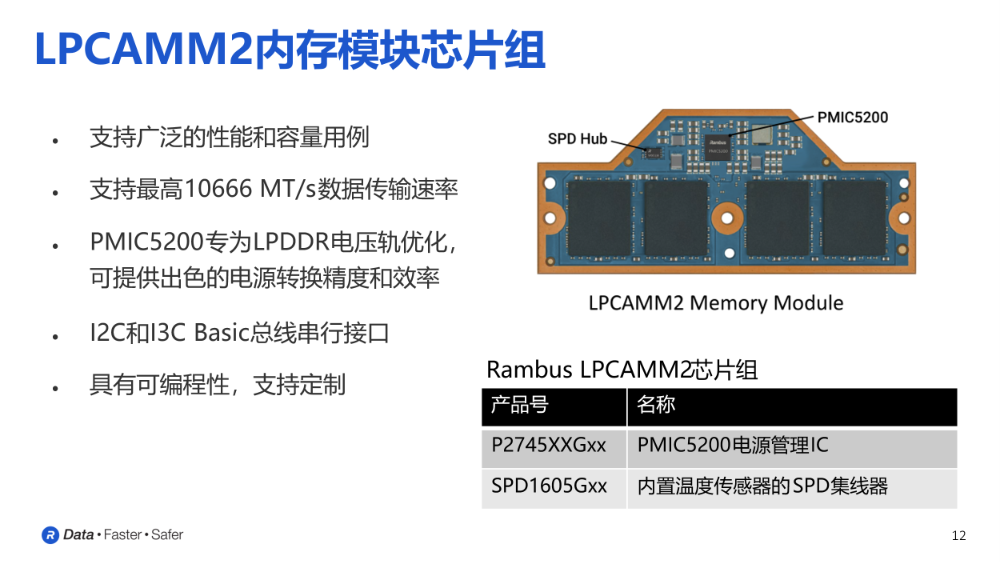

PMIC5120 is the second-generation DDR5 client PMIC, featuring stronger current supply capabilities and optimized functional characteristics, designed for CSODIMM and CUDIMM modules, and widely used in laptops, desktops, and workstations. The LPCAMM2 module chipset integrates PMIC5200, which is optimized for LPDDR voltage rails, aiming to provide industry-leading power conversion accuracy and efficiency. Additionally, the chipset includes an SPD Hub, which not only stores non-volatile configuration information but also provides bidirectional retiming and redriving capabilities for I2C and I3C buses, and integrates an on-chip temperature sensor.

The LPCAMM2 module chipset integrates PMIC5200, which is optimized for LPDDR voltage rails, aiming to provide industry-leading power conversion accuracy and efficiency. Additionally, the chipset includes an SPD Hub, which not only stores non-volatile configuration information but also provides bidirectional retiming and redriving capabilities for I2C and I3C buses, and integrates an on-chip temperature sensor. These chips (referring to PMICs and SPD Hub, etc.) work together to achieve highly configurable module designs through sideband interfaces, enabling them to support a wide range of performance and capacity application scenarios based on core LPDDR5 technology. Looking ahead, it is expected that this module’s form factor and its component chips will further expand their capabilities to support data transfer rates of up to 10.7 GT/s.

These chips (referring to PMICs and SPD Hub, etc.) work together to achieve highly configurable module designs through sideband interfaces, enabling them to support a wide range of performance and capacity application scenarios based on core LPDDR5 technology. Looking ahead, it is expected that this module’s form factor and its component chips will further expand their capabilities to support data transfer rates of up to 10.7 GT/s. The new client modules using DDR5 memory, including CSODIMM and CUDIMM, feature the PMIC5120, a CKD (Client Clock Driver) designed to enhance clock signal integrity and reduce jitter, as well as the SPD Hub.Currently, the chipset supports module speeds of up to 6400 MT/s and 7200 MT/s. However, with its enhanced current supply capabilities, the architecture of PMIC5120 is already designed to support all future DDR5 data rates. PMIC5120 and CKD themselves also possess high configurability, supporting a wide range of performance and capacity applications.These two PMICs, along with the client clock driver (CKD) and serial presence detect (SPD) hub, form a complete chipset solution for memory modules in AI laptops, desktops, and workstations. Furthermore, with the launch of these two new PMICs, Rambus can now provide a complete memory interface chipset for all JEDEC standard DDR5 and LPDDR5 memory modules for both servers and clients.

The new client modules using DDR5 memory, including CSODIMM and CUDIMM, feature the PMIC5120, a CKD (Client Clock Driver) designed to enhance clock signal integrity and reduce jitter, as well as the SPD Hub.Currently, the chipset supports module speeds of up to 6400 MT/s and 7200 MT/s. However, with its enhanced current supply capabilities, the architecture of PMIC5120 is already designed to support all future DDR5 data rates. PMIC5120 and CKD themselves also possess high configurability, supporting a wide range of performance and capacity applications.These two PMICs, along with the client clock driver (CKD) and serial presence detect (SPD) hub, form a complete chipset solution for memory modules in AI laptops, desktops, and workstations. Furthermore, with the launch of these two new PMICs, Rambus can now provide a complete memory interface chipset for all JEDEC standard DDR5 and LPDDR5 memory modules for both servers and clients.

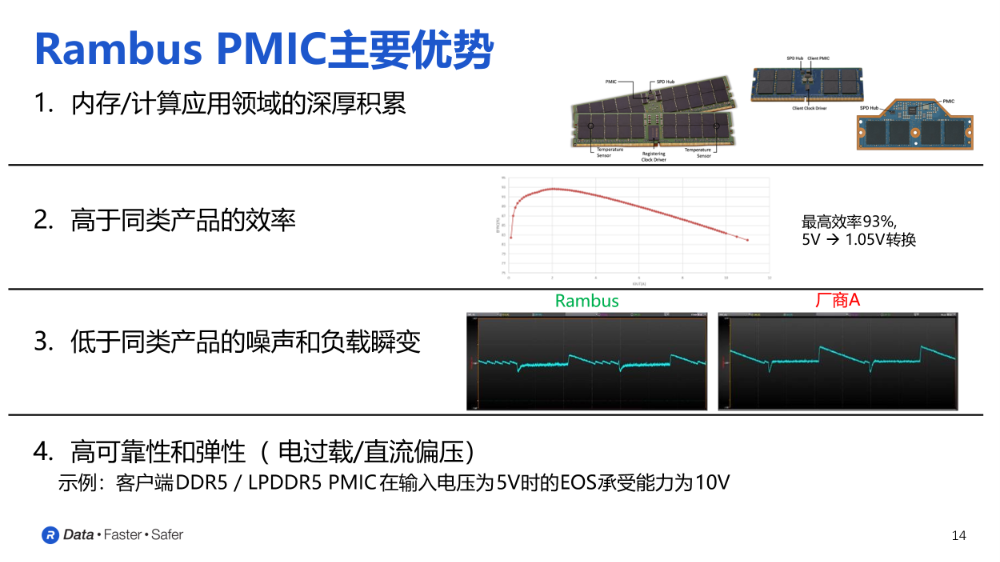

Key Advantages of Rambus PMICs

Rambus has accumulated 35 years of deep experience in high-performance memory,and possesses profound insights into the end markets served by its products.“Our testing goes beyond the component level, extending to extensive system-level module testing; our engineers have a thorough understanding of the entire system, firmware, and interface training. We know every component on the module and can provide industry-leading technical support for any module-related issues,”said John Eble.He further pointed out thatin terms of power conversion efficiency, our designs aim to exceed standard specifications. This not only saves power and reduces total cost of ownership (TCO) but also helps customers achieve their goals.Industry insiders estimate that the memory capacity required for AI PCs may be 1.5 to 2 times that of traditional PCs, and all these performance improvements (including bandwidth and capacity) must be achieved within a reasonable power budget. PMICs help address the platform-level power delivery challenges of modules. They can optimize and finely control voltage and current, thereby improving power efficiency. Additionally, when PCs switch between different power states, PMICs must maintain high power conversion rates across a wide load range. Moreover, PMICs need to support advanced features such as Dynamic Voltage Frequency Scaling (DVFS).Our delivered products minimize the noise they generate and respond quickly and accurately to load transients that may occur in computing systems.Finally, modules may encounter overstress situations during manual handling. To this end, our designed PMICs can withstand overvoltage of at least twice the nominal input voltage to ensure high reliability and robustness under any stress events.Driven by the demands of advanced workloads such as generative AI, data rates and capacities are continuously rising, accompanied by increasing challenges in power integrity and signal integrity. Rambus has successfully extended and applied its expertise and innovations from server modules to these two client chipsets—specifically for LPCAMM2 and DDR5 CSODIMM and CUDIMM chipsets.Furthermore, choosing suppliers with a good track record in quality and mass production, along with deep expertise in sourcing the complete chipset, will help reduce customer risks, ensure supply chain stability, and accelerate time to market.

Rambus has accumulated 35 years of deep experience in high-performance memory,and possesses profound insights into the end markets served by its products.“Our testing goes beyond the component level, extending to extensive system-level module testing; our engineers have a thorough understanding of the entire system, firmware, and interface training. We know every component on the module and can provide industry-leading technical support for any module-related issues,”said John Eble.He further pointed out thatin terms of power conversion efficiency, our designs aim to exceed standard specifications. This not only saves power and reduces total cost of ownership (TCO) but also helps customers achieve their goals.Industry insiders estimate that the memory capacity required for AI PCs may be 1.5 to 2 times that of traditional PCs, and all these performance improvements (including bandwidth and capacity) must be achieved within a reasonable power budget. PMICs help address the platform-level power delivery challenges of modules. They can optimize and finely control voltage and current, thereby improving power efficiency. Additionally, when PCs switch between different power states, PMICs must maintain high power conversion rates across a wide load range. Moreover, PMICs need to support advanced features such as Dynamic Voltage Frequency Scaling (DVFS).Our delivered products minimize the noise they generate and respond quickly and accurately to load transients that may occur in computing systems.Finally, modules may encounter overstress situations during manual handling. To this end, our designed PMICs can withstand overvoltage of at least twice the nominal input voltage to ensure high reliability and robustness under any stress events.Driven by the demands of advanced workloads such as generative AI, data rates and capacities are continuously rising, accompanied by increasing challenges in power integrity and signal integrity. Rambus has successfully extended and applied its expertise and innovations from server modules to these two client chipsets—specifically for LPCAMM2 and DDR5 CSODIMM and CUDIMM chipsets.Furthermore, choosing suppliers with a good track record in quality and mass production, along with deep expertise in sourcing the complete chipset, will help reduce customer risks, ensure supply chain stability, and accelerate time to market.

Technological Evolution of Memory Modules

From the perspective of end application processes,LPCAMM2 is a new technology that OEM manufacturers may deploy first in workstation-level laptops.John Eble believes that LPCAMM2, with the additional bandwidth provided by LPDDR5X,will have great potential in the fields of AI laptops and desktops.Becausewithin a fixed power envelope, if the power consumption of the memory portion can be reduced, then the saved power budget can be allocated to the GPU or dedicated accelerators.Currently, there are versions on the market for CUDIMM and CSODIMM modules that support ECC (Error Correction Code) functionality. Our chipsets are designed to fully consider and support the additional DRAM load brought by ECC, which is reflected in the assurance of clock signal integrity and the power output capabilities provided for such memory. Therefore,John Eble stated thatthis is another excellent example of extending (or “downstreaming”) mature technologies from server fields to client applications.Regarding future technological directions,John Eble predicts thatthe current LPCAMM modules have not widely seen products supporting ECC functionality, which presents development opportunities.Secondly,LPCAMM currently does not adopt true signal buffering designs, while CUDIMM and CSODIMM typically buffer clock signals. Future implementations of clock signal buffering on LPCAMM, and even adding buffering designs for command/address (CA) buses and data buses across various module forms, to further enhance signal integrity, may be a potential technological path for continuous evolution and performance enhancement.It is expected that the first PC platform supporting LPCAMM2 will be launched by the end of this year, which will promote the wider adoption of LPDDR5 modular solutions. The first platforms equipped with PMIC5120 are expected to be launched a year later, by the end of 2026. At that time, memory module solutions are expected to achieve data transfer rates of 8000 MT/s (megatransfers per second).

Disclaimer:This article is originally from Electronic Enthusiasts, please indicate the source above when reprinting. For group communication, please add WeChat elecfans999,for submission of interview requests, please send an email to [email protected].

More Hot Articles to Read

-

Haiguang “swallows” Zhongke Shuguang, domestic computing power “super aircraft carrier” sets sail!

-

IT jobs are collapsing! Claude 4 shocks the release: AI programming large model evolves again

-

Exhibition Highlights: Drones dazzling, chips positioning low-altitude economic explosion

-

Exhibition Highlights: From AI glasses to AI toys, workers’ counterattack equipment + parenting artifacts debut

-

Xiaomi’s self-developed 3nm flagship SoC and 4G baseband debut! Lei Jun reviews 11 years of chip-making journey

Click to Follow and Star Us

Set us as a star to not miss any updates!