Can Xilinx FPGA General IO Be Directly Connected to PLL as Clock Input?

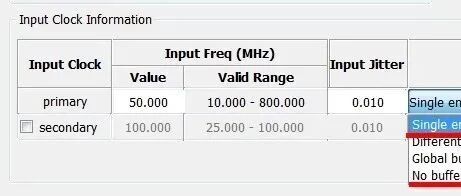

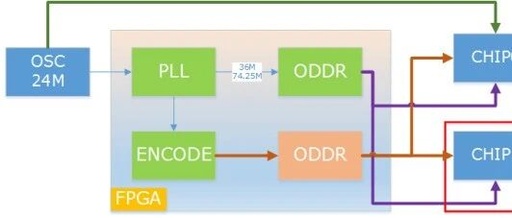

[Conclusion] General IO cannot be directly used as a clock input for PLL; dedicated clock pins can be used instead. General IO can be connected to the PLL clock input through a BUFG, but the PLL settings must be modified to select “No Buffer” for the input clock option. The specific internal layout can be … Read more