The third installment of the basic knowledge of FPGA internal resources is here! Today we will discuss the FPGA clock processing unit module. The clock is the soul of logic, so the clock signal is very important, take note!!Look me~

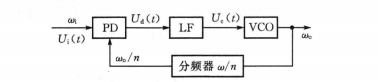

1. PLL

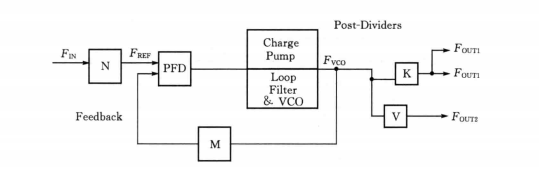

1. Introduction to Xilinx’s Phase-Locked Loop Structure

The basic structure of Xilinx’s phase-locked loop is shown in the figure:

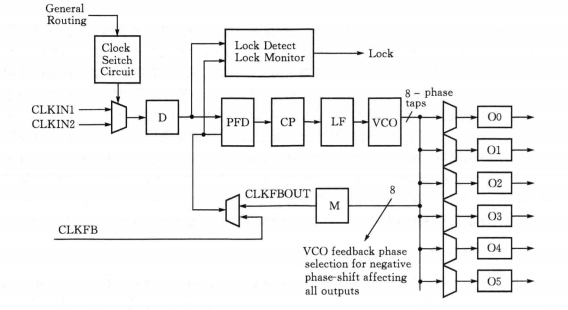

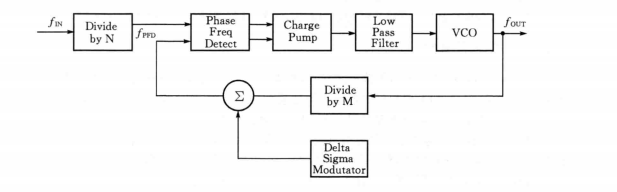

2. Introduction to Altera’s Phase-Locked Loop Structure

The basic structure of Altera’s phase-locked loop is shown in figure 3:

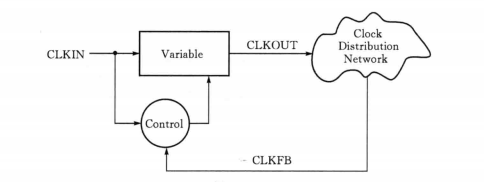

2. DCM

Chengdian Youth Learning 100-Day Order Class is Hotly Launched!!! Online and offline synchronous learning on the think tank platform.“FPGA Introduction Eight Classes”, “FPGA Introduction Ten Projects”, “FPGA Advanced Five Projects”, and other series of courses. The course starts from zero foundation, with each class guiding students through a small experiment, learning the FPGA course step by step.

Currently, Chengdian Youth Learning has provided many companies with high-level FPGA talents, with salaries exceeding those of graduates from the same period by 52%, and an employment rate of 100%.

Welfare Giveaway!! You can now apply for free to learn the FPGA course online, hurry up, slow hands will miss out! Course linkhttps://z.shaonianxue.cn. Students can follow the “Chengdian Youth Learning” public account, with the latest updates in the FPGA industry continuing to be updated~~

END