Comprehensive Analysis of Interrupt Handling in ARM Cortex-M

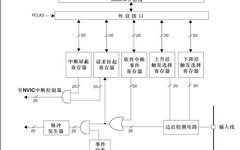

Today, we will discuss interrupt handling in ARM Cortex-M. In embedded systems, interrupts are the core mechanism for achieving real-time responses. Imagine if there were no interrupts: • When a button is pressed, the system might be busy with other tasks and miss the response. • Incoming communication data might be lost due to untimely … Read more