The Serial Peripheral Interface (SPI) is one of the most widely used interfaces between microcontrollers and peripheral ICs (such as sensors, ADCs, DACs, shift registers, SRAM, etc.). SPI is a synchronous, full-duplex, master-slave interface. Data from the master or slave is synchronized on the rising or falling edge of the clock. Both the master and slave can transmit data simultaneously. The SPI interface can be either 3-wire or 4-wire.

1. Interface

4-wire SPI devices have four signals:

-

SCLK, SPI Clock;

-

CS, Chip Select;

-

MOSI, Master Output, Slave Input;

-

MISO, Master Input, Slave Output.

The device that generates the clock signal is called the master. The data transmitted between the master and slave is synchronized with the clock generated by the master. Generally, chips support clock speeds up to several tens of megahertz; specific clock frequency specifications for the SPI interface should be checked in the chip’s data sheet. The chip select signal from the master, CS, is used to select the slave. CS is typically an active-low signal, and when pulled high, the slave is disconnected from the SPI bus. When using multiple slaves, the master needs to provide a separate chip select signal for each slave. MOSI and MISO are the data lines. MOSI sends data from the master to the slave, while MISO sends data from the slave to the master.

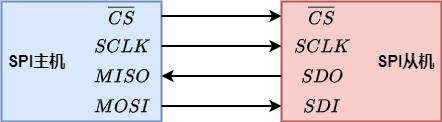

There can only be one master in an SPI interface, but there can be one or more slaves. The diagram below shows the SPI connection between the master and one slave.

Figure 1 SPI Interface between Master and Slave

To start SPI communication, the master must send a clock signal and enable the CS signal (by pulling it low) to select the slave. SPI is a full-duplex interface, allowing the master and slave to send data simultaneously through the MOSI and MISO lines. During SPI communication, data transmission (serially shifting out to the MOSI bus) and reception (sampling or reading data on the MISO bus) occur simultaneously. The serial clock edge synchronizes the shifting and sampling of data. The SPI interface allows users to flexibly choose the rising or falling edge of the clock to sample and/or shift data.

2. Clock Polarity and Clock Phase

In SPI, the master can select the clock polarity and clock phase. CPOL (clock Polarity) bit sets the polarity of the clock signal during idle state. The idle state refers to when CS is high at the start of transmission and during the transition to low, and when CS is low at the end of transmission and during the transition to high. CPHA (clock Phase) bit selects the clock phase, where 0 indicates sampling on the first clock edge and 1 indicates sampling on the second clock edge. Depending on the state of the CPHA bit, data can be sampled and/or shifted using the rising or falling edge of the clock. The master must select the clock polarity and clock phase according to the requirements of the slave. Based on the selections of CPOL and CPHA bits, four SPI modes are available. The table below shows these four SPI modes.

|

SPI Mode |

CPOL |

CPHA |

Clock Polarity in Idle State |

Clock Phase for Sampling and/or Shifting Data |

|

0 |

0 |

0 |

0 |

Sample on rising edge, shift out on falling edge |

|

1 |

0 |

1 |

0 |

Sample on falling edge, shift out on rising edge |

|

2 |

1 |

0 |

1 |

Sample on falling edge, shift out on rising edge |

|

3 |

1 |

1 |

1 |

Sample on rising edge, shift out on falling edge |

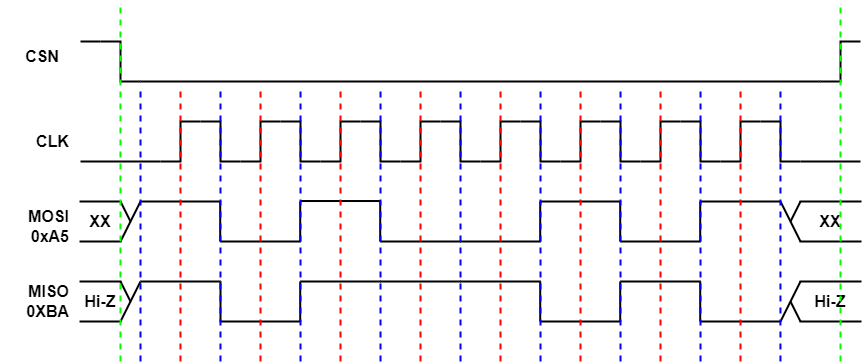

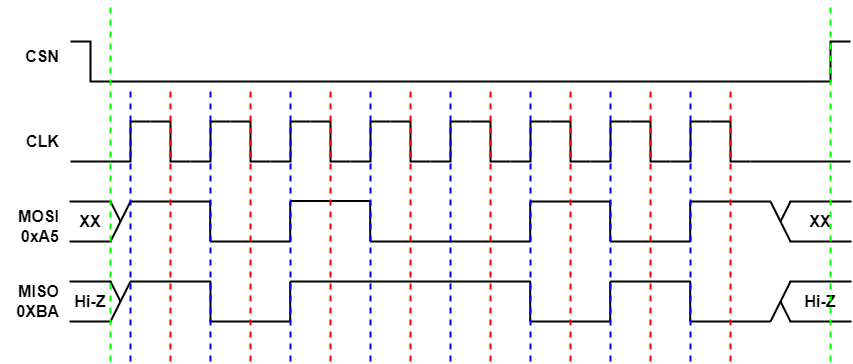

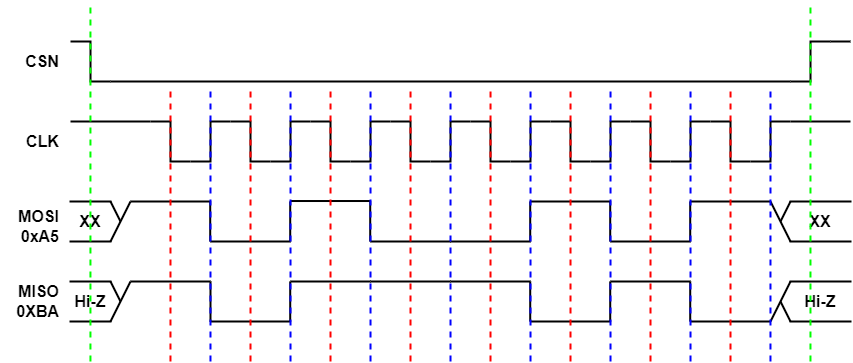

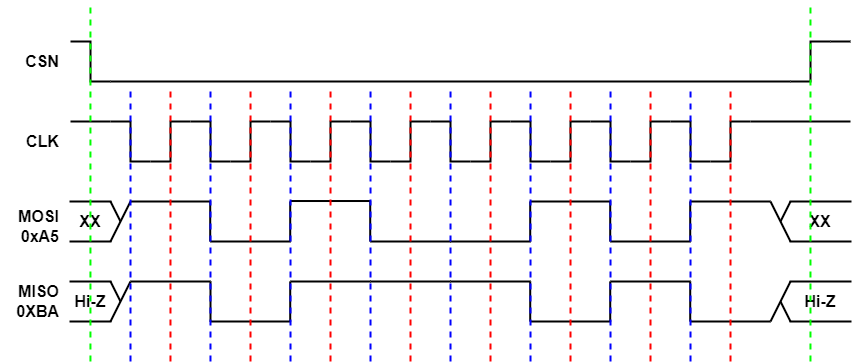

Figures 2 to 4 show communication examples under the four SPI modes, with data displayed on the MOSI and MISO lines. The start and end of transmission are indicated by green dashed lines, the sampling edges by red dashed lines, and the shifting edges by blue dashed lines. The sampled edge corresponds to the data the master intends to send, while the master changes the data at the shifting edge.

Figure 2 presents the timing diagram for SPI mode 0. In this mode, CPOL is 0, indicating that the idle state of the clock signal is low; CPHA is 0, indicating that data is sampled on the rising edge (shown by the red dashed line), and data is shifted out on the falling edge of the clock signal (shown by the blue dashed line).

Figure 2 SPI Mode 0, CPOL = 0, CPHA = 0: CLK idle state is low, data is sampled on the rising edge, and shifted out on the falling edge.

Figure 3 presents the timing diagram for SPI mode 1. In this mode, CPOL is 0, indicating that the idle state of the clock signal is low; CPHA is 1, indicating that data is sampled on the falling edge (shown by the red dashed line), and data is shifted out on the rising edge of the clock signal (shown by the blue dashed line).

Figure 3 SPI Mode 1, CPOL = 0, CPHA = 1: CLK idle state is low, data is sampled on the falling edge, and shifted out on the rising edge.

Figure 4 presents the timing diagram for SPI mode 2. In this mode, CPOL is 1, indicating that the idle state of the clock signal is high; CPHA is 0, indicating that data is sampled on the falling edge (shown by the red dashed line), and data is shifted out on the rising edge of the clock signal (shown by the blue dashed line).

Figure 4 SPI Mode 2, CPOL = 1, CPHA = 0: CLK idle state is high, data is sampled on the falling edge, and shifted out on the rising edge.

Figure 5 presents the timing diagram for SPI mode 3. In this mode, CPOL is 1, indicating that the idle state of the clock signal is high; CPHA is 1, indicating that data is sampled on the rising edge (shown by the red dashed line), and data is shifted out on the falling edge of the clock signal (shown by the blue dashed line).

Figure 5 SPI Mode 3, CPOL = 1, CPHA = 1: CLK idle state is high, data is sampled on the rising edge, and shifted out on the falling edge.

From the examples of the four SPI communication modes, it can be seen that when CPHA is 0, data should be stable at the first clock edge sampling, and the first data should ideally be shifted out half a clock cycle before the first clock edge after CS is pulled low to allow sufficient setup time. When CPHA is 1, data is sampled at the second clock edge, and the last data transition should ideally be delayed half a clock cycle at the end clock edge to allow sufficient hold time.

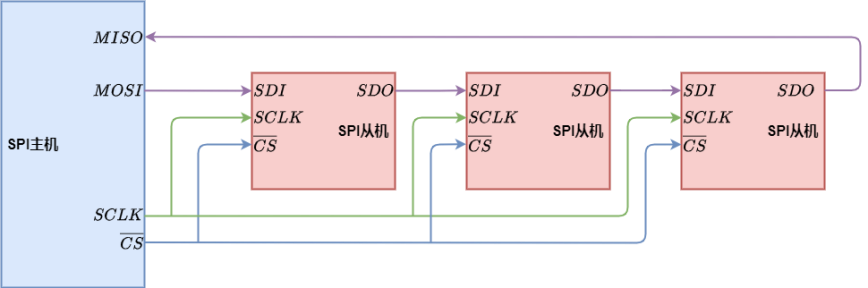

3. Multi-Slave Configuration

Multiple slaves can be used with a single SPI master. Slaves can be connected in a conventional mode or in a daisy chain mode.

Conventional SPI Mode:

In conventional mode, the master needs to provide a separate chip select signal for each slave. Once the master enables (pulls low) the chip select signal, the clock and data on the MOSI/MISO lines can be used for the selected slave. If multiple chip select signals are enabled, the data on the MISO line will be corrupted because the master cannot identify which slave is transmitting data.

From Figure 6, it can be seen that as the number of slaves increases, the number of chip select lines from the master also increases. This quickly increases the number of inputs and outputs that the master needs to provide and limits the number of slaves that can be used. Other techniques can be used to increase the number of slaves in conventional mode, such as using multiplexers to generate chip select signals.

Figure 6 Multi-Slave SPI Configuration

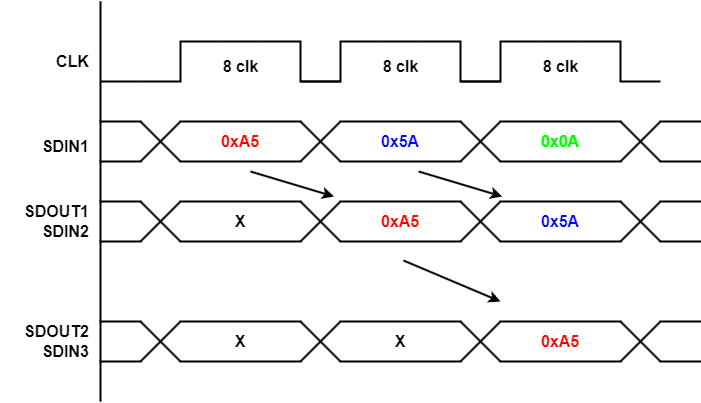

Daisy Chain Mode:

In daisy chain mode, the chip select signals of all slaves are connected together, and data propagates from one slave to the next. In this configuration, all slaves receive the same SPI clock simultaneously. Data from the master is sent directly to the first slave, which then provides the data to the next slave, and so on.

When using this method, since data propagates from one slave to the next, the number of clock cycles required to transmit data is proportional to the position of the slave in the daisy chain. For example, in the 8-bit system shown in Figure 7, to enable the third slave to receive data, 24 clock pulses are needed, while only 8 clock pulses are required in conventional SPI mode. Figure 8 shows the clock cycles and data propagation through the daisy chain. Not all SPI devices support daisy chain mode.

Figure 7 Multi-Slave SPI Daisy Chain Configuration

Figure 8 Data Propagation in Daisy Chain Configuration