Semiconductor Industry Observation(icbank)

Semiconductor Industry Observation: The first vertical media in the semiconductor industry【www.icbank.cc】

Author: Junko Yoshida

With advancements in LTE technologies such as LTE Advanced and LTE Advanced Pro, the industry has been stirred up—triggering a series of new demands that make next-generation baseband designs more complex than any previous generation of smartphone modem chips.

Major global telecom chip suppliers Qualcomm, DSP core supplier CEVA, and processor core provider ARM are all racing to meet this challenge. All three companies have developed new processor architectures and have rushed to announce them ahead of this year’s Mobile World Congress (MWC). Qualcomm announced the Snapdragon X16, CEVA unveiled the CEVA-X4, and ARM discussed its new Cortex-R8.

Qualcomm’s new modem chip executes intensive LTE protocols and voice codecs in its Hexagon DSP core while also using ARM Cortex to run the Linux operating system (OS), IMS, and IP stack.

What are the challenges?

So, what distinguishes these new baseband modems?

Issues related to this technology include: increased carrier aggregation (CA), integrating multiple radio access technologies (Multi-RAT) into a single modem, low-latency operations when switching between different modems, synchronizing dual base stations, and the complexity that comes with high-quality voice services via VoLTE. According to CEVA, the new baseband modems must be able to handle all of the above or more.

Mike Demler, a senior analyst at The Linley Group, calls for a “comprehensive check-up” of existing modem chip architectures to meet the increasingly stringent performance and power consumption limits of LTE Advanced (LTE-A) and LTE-A Pro standards.

Thus, the competition among Qualcomm, CEVA, and ARM is beginning to transform into a new battleground focused on processors, hardware acceleration, and DSP.

Vendors are actively discussing how to optimize the increased LTE baseband workloads that should be handled between Layer 1 physical (PHY) controllers, Layer 2, and Layer 3 processing; and whether to adopt advanced DSP cores, enhanced processor cores, or a combination of both?

Each vendor, based on their different spheres of influence, clearly has different ideas.

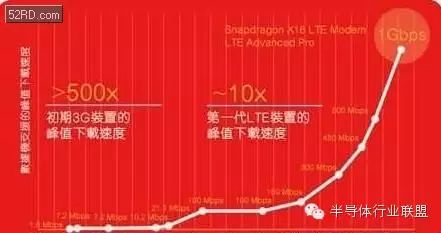

Qualcomm announced its advanced LTE modem Snapdragon X16, which supports LTE-A Pro Category 16 with downlink speeds of up to 1 Gbps and Category 13 with uplink speeds of up to 150 Mbps.

Qualcomm’s latest Snapdragon X16 supports download speeds of up to 1 Gbps, claiming to be the first Gigabit-level LTE modem in the mobile industry.

(Source: Qualcomm)

To prevent Qualcomm from monopolizing the market, CEVA and ARM also released their latest core designs—CEVA-X4 and ARM Cortex-R8, respectively. They claim that their latest architectures are ready to meet the challenges of LTE-A Pro modems. However, currently, no commercial baseband chip has adopted the processor cores from any of the IP suppliers.

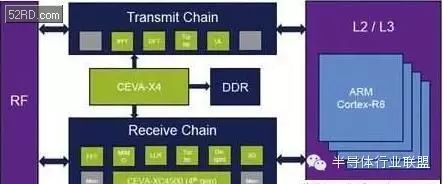

In response to the increasing processing demands of LTE-A Pro modem chips, the two IP core suppliers have clearly taken entirely different development focuses. For example, CEVA updates its L1 PHY controller with CEVA-X4. In contrast, ARM focuses on meeting the continuously increasing demands for Layer 2 and Layer 3 software processing through its latest four-core Cortex-R8 design.

Demler clearly points out that Cortex-R8 and CEVA-X4 are two completely different cores. CEVA-X4 is used for PHY layer control, while ARM Cortex-R is not. He emphasizes, “X4 and R8 may coexist in a modem application, with X4 handling the physical layer while Cortex-R manages higher-level control functions.”

Could CEVA-X4 and ARM Cortex-R8 coexist in the next-generation modem chip?

(Source: CEVA)

Encountering Bottlenecks

Eran Briman, Vice President of Marketing and Business Development at CEVA, pointed out that after a detailed study of the demands for the latest advanced baseband data modems, “we found that the PHY controller is the bottleneck in the next-generation baseband.”

By redefining the performance and energy efficiency of processing control and data planes for baseband applications, CEVA has developed a new CEVA-X DSP architecture.

CEVA-X4 is the first licensed core from the CEVA-X architecture. Although DSP has always been CEVA’s strong suit, Demler believes that CEVA-X4 is more like “a controller with DSP capabilities.”

Emmanuel Gresset, Director of Business Development for CEVA’s Wireless Business Unit, explains that the advanced DSP features added to CEVA-X4 combine control layer processing with “support for co-processors and hardware acceleration.”

He believes that CEVA-X4 is a “new type of processor that achieves a true balance between DSP and control.”

Gresset also noted that CEVA-X4 achieved a CoreMark/MHz benchmark of 4.0. CoreMark is a benchmark specifically designed to measure CPU performance in embedded systems. Gresset stated that this is very important for CEVA, as CEVA-X4 is currently “on par with ARM Cortex-R7/R8.”

The new CEVA-X4 architecture fully integrates controller and DSP processing, targeting applications in smartphones, IoT devices, and next-generation 5G baseband data modems.

(Source: CEVA)

Defending the L2/L3 Processing Domain

ARM has always been the leading CPU core supplier in the smartphone market.

Chris Turner, Director of Advanced Technology Marketing at ARM, explains, “ARM Cortex-R7 is currently deployed in a large number of 3G/4G smartphone modems, while Cortex-R4 and Cortex-R5 are also used in modem products from ARM partners.”

With the launch of Cortex-R8, ARM plans to meet the increasing demands for protocol software processing as well as LTE-A Pro and first-generation 5G. He added, “We expect to see new baseband designs upgraded to use Cortex-R8.”

It is worth noting that Cortex-R is optimized for hard real-time applications, and Turner thus describes Cortex-R8 as “the only real-time processor designed for 5G performance.”

However, strangely, Qualcomm has apparently not adopted ARM cores in its new Snapdragon X16 modem, instead opting to deploy its own DSP to handle the LTE-A Pro workload.

The main difference between ARM Cortex-R8 and R7 is that R8 supports up to four superscalar out-of-order execution cores. Additionally, ARM states that R8 is equipped with “up to 2MB of tightly coupled memory per core,” providing larger capacity.

With the significant increase in data transmission rates for 5G, Cortex-R8 combines low latency, high performance, and low power consumption, helping to create modems that support LTE-A Pro and 5G.

(Source: ARM)

Regarding other parts of the modem chip, Turner admits that “the physical layer is a very complex engineering task, including analog conversion, DSP modulation and demodulation, Turbo coding, error checking, and acceleration encryption, as well as header compression, etc.”

So how do ARM Cortex-R series cores connect with it? Turner said, “Indeed, some technologies can be obtained from specialized IP suppliers, but they usually still need to be modified or configured to be used in a company’s proprietary modem architecture.”

He added, “We see ARM Cortex-R series processors appearing in software interfacing with physical layer (Layer-1) hardware, providing Layer-2 and Layer-3 processing for managing and scheduling all software according to different standards for connections.”

Additionally, he stated that ARM processors can also execute Layer-1 control software, configuring and managing interfaces connected to Layer-1 hardware (including DSP and localized control logic).

Is there an overlap?

However, CEVA has a slightly different view of this competitive landscape. Gresset pointed out that ARM’s Cortex-R7 or R8 in this regard “lacks DSP and system control.” He explained that this makes it difficult for ARM to expand the role of Cortex-R in processing PHY controllers.

Gresset also added, “Compared to CEVA-X4 using VLIW/SIMD cores, ARM’s R7/R8, due to their superscalar out-of-order architecture, result in larger chip sizes and higher power consumption per core.”

Therefore, Gresset emphasized that CEVA, while defending its territory in Layer 1 PHY controllers by adding more hardware acceleration, also hopes to create a pathway to enhance Layer-2 and Layer-3 processing, even though this has traditionally been dominated by ARM. He referred to the powerful DSP processing (up to 16 GOP), efficient controller performance, and advanced system control as the “three pillars of the new CEVA-X architecture.”

On the other hand, ARM believes that the key advantage of Cortex-R8 lies in its ability to “interface with four consistent cores and extend modem software data.” Its goal is to achieve parallelization for intensive real-time software workloads and meet the performance and timing required for LTE-A and LTE-A Pro.

Source: eettaiwan